Fターム[5F140BD13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | 金属酸化膜 (2,702) | 複合金属酸化膜 (873)

Fターム[5F140BD13]に分類される特許

21 - 40 / 873

金属酸化物高誘電体エピタキシャル膜の製造方法、および基板処理装置

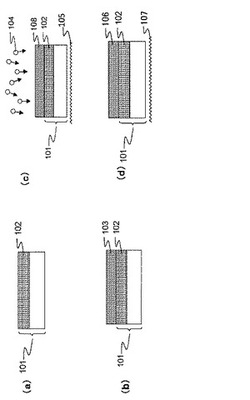

【課題】ゲート絶縁膜を形成する際に、界面準位を低減しつつ、EOTのさらなる低減が実現可能な金属酸化物高誘電体エピタキシャル膜の製造方法、および基板処理装置を提供すること。

【解決手段】単結晶領域102を有する基板101上に、金属膜であって、該金属膜の酸化物の誘電率が酸化シリコン膜よりも高く、かつ金属膜の酸化物が単結晶領域102とエピタキシャル関係を有する金属膜103を、単結晶領域102と金属膜103とが界面反応しない基板温度で形成する(図1(b))。金属膜103が形成された基板101を、上記界面反応しない基板温度で、単結晶領域102と金属膜103とが界面反応しない酸素分圧の酸素ガス雰囲気に暴露する(図1(c))。酸素ガス雰囲気に暴露された基板103を、上記酸素分圧の酸素ガス雰囲気に保持し、金属膜の酸化物である金属酸化物高誘電体膜が結晶化する基板温度で熱処理する(図1(d)。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

振幅変調された高周波エネルギーを使用してゲート誘電体をプラズマ窒化するための方法及び装置

【課題】二酸化シリコン層及びシリコン基板を窒素イオンで過剰にダメージを生じさせることのないプラズマ窒化プロセスのための方法及び装置を提供する。

【解決手段】窒化ゲート誘電体層を形成するための方法及び装置。この方法は、電子温度スパイクを減少するために、滑らかに変化する変調のRF電源により処理チャンバー内に窒素含有プラズマを発生することを含む。電源が滑らかに変化する変調のものであるときには、方形波変調のものに比して、電界効果トランジスタのチャンネル移動度及びゲート漏洩電流の結果が改善される。

(もっと読む)

仮想ボディ・コンタクト型トライゲート

【課題】FETデバイスにおける閾値電圧をより良く制御できるデバイスの提供。

【解決手段】基板101と、基板101の上のSiGe層103と、SiGe層上の半導体層105と、基板、SiGe層及び半導体層に隣接した絶縁層109aと、絶縁層に隣接した一対の第1のゲート構造体111と、絶縁層上の第2のゲート構造体113とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び導体層の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体が、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】下地絶縁膜の膜厚精度の向上とトランジスタ特性の変動抑制との両立が図られたMISトランジスタを備えた半導体装置、及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100における活性領域103a上に形成されたゲート絶縁膜108aと、ゲート絶縁膜108a上に形成されたゲート電極111aとを有するMISトランジスタ170を備えている。ゲート絶縁膜108aは、活性領域103a上に形成された板状の下層ゲート絶縁膜210aと、下層ゲート絶縁膜210a上に形成された断面形状が凹状の上層ゲート絶縁膜211aとを有する。下層ゲート絶縁膜210aは、活性領域103a上に形成された下地絶縁膜104aと、第1の高誘電率絶縁膜106aとで構成され、上層ゲート絶縁膜211aは、第1の高誘電率絶縁膜106a上に形成された第2の高誘電率絶縁膜107aで構成される。

(もっと読む)

半導体装置

【課題】半導体集積回路の微細化に伴い非常に短くなったゲート長を有するトランジスタにおいて、ゲート絶縁膜におけるリーク電流の発生を抑制し、トランジスタとしての機能を高めることが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された1対のソース/ドレイン領域と、1対のソース/ドレイン領域に挟まれる領域上であって、主表面に接するように形成されたゲート絶縁膜AFEと、ゲート絶縁膜AFEの上面に接するように形成されたゲート電極POとを備える。上記1対のソース/ドレイン領域の一方から他方へ向かう方向のゲート電極POの長さは45nm未満である。ゲート絶縁膜AFEは反強誘電体膜を有する。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】電界効果トランジスタであって、半導体基板10上に垂直に形成され、且つ第1の領域が第2の領域よりも高く形成された半導体フィン31と、第1の領域の両側面にゲート絶縁膜40を介して設けられたゲート電極50と、第2の領域に第1の領域の上端よりも低い位置まで設けられた、合金半導体からなるソース・ドレイン下地層63,73と、下地層63,73上に第1の領域の上部を挟むように設けられた、下地層63,73とは格子定数の異なるソース・ドレイン領域60,70とを備えている。チャネル領域には応力が付与され、下地層63,73は、空乏層が収まる厚さよりも厚く、熱平衡状態で結晶にミスフィット転位が導入される熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜をCMP法で研磨、平坦化する際、MOS型トランジスタのチャネル領域に応力を与えるためにゲート電極を覆うように形成される応力ライナー膜が研磨されて、トランジスタ特性の変動やバラツキが発生しないようにする。

【解決手段】 第1活性領域(例えばPチャネルトランジスタ形成領域)上のゲート電極(シリコン膜14と金属シリサイド膜15との積層膜)上には第1応力膜(圧縮応力ライナー膜)16のみを形成し、第2活性領域(例えばNチャネルトランジスタ領域)上のゲート電極上には第2応力膜(引っ張り応力ライナー膜)18のみを形成する。一方、素子分離10上のゲート電極上には第1および第2応力膜16、18の積層膜を形成する。層間絶縁膜20のCMP法による研磨は、素子分離10上の第2応力膜18の露出後に停止する。

(もっと読む)

ゲルマニウム酸化膜の形成方法および電子デバイス用材料

【課題】Ge基板と絶縁膜との界面に、良好なGe酸化膜を形成する。

【解決手段】上面に絶縁膜(High−k膜)32が積層されたGe基板31の絶縁膜32の表面から、酸素原子含有ガスを含む処理ガスのプラズマを照射する。絶縁膜32越しにGe基板31を酸化させて、絶縁膜32とGe基板31との界面にGe酸化膜33を形成する。絶縁膜32がGe酸化膜33に対して保護膜として機能し、形成されたGe酸化膜33の劣化を防ぐ。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜界面材料としてGeO2 を用いた場合においてもGeO2 層の劣化を抑制することができ、素子の信頼性向上をはかると共に、プロセスの歩留まり向上をはかる。

【解決手段】本発明の実施形態による電界効果トランジスタは、Geを含む基板10上の一部に設けられた、少なくともGeO2 層を含むゲート絶縁膜20と、ゲート絶縁膜20上に設けられたゲート電極30と、ゲート電極30下のチャネル領域を挟んで前記基板に設けられたソース/ドレイン領域50と、前記ゲート絶縁膜20の両側部に形成された窒素含有領域25と、を備えた。

(もっと読む)

トンネルトランジスタの製造方法

【課題】1回のリソグラフィ工程によりセルフアラインでトンネルトランジスタを製造する方法を提供する。

【解決手段】ゲート絶縁膜及びゲート電極が積層された半導体基板上に第1の絶縁膜を形成しリソグラフィにより第1の絶縁膜の端部に第1の絶縁膜とは薬品選択性が異なりゲート電極位置を画定する第2の絶縁膜を形成する工程と、第1及び第2の絶縁膜をマスクにゲート電極の一端を画定する工程と、第1及び第2の絶縁膜をマスクにして第1導電型不純物を半導体基板に導入しソースを形成する工程と、半導体基板全面に第1の絶縁膜とは薬品選択性が異なる第3の絶縁膜を被覆する工程と、該第3の絶縁膜の一部を除去することにより該第1の絶縁膜を選択的に除去する工程と、第2及び第3の絶縁膜をマスクにしてゲート電極を形成した後、第2導電型不純物を半導体基板に導入しドレインを形成する工程を含むトンネルトランジスタの製造方法。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

CVDエッチングおよび堆積シーケンスにより形成されるCMOSトランジスタ接合領域

【課題】CMOSトランジスタのソース−ドレイン置換技術に関し、装置一式を利用して基板材料に窪みをエッチングして、その後、応力を有する異なる材料を堆積することに関し、大気に曝すことなく、エッチングとその後の堆積とを行う方法の提供。

【解決手段】エッチングおよびデポジションによりCMOSトランジスタの接合領域を形成する方法であって、

第1接合領域270を形成すべくゲート電極190の隣の基板120の第1箇所と、前記基板120に第2接合領域280を形成すべく前記ゲート電極190を介して前記第1箇所とは反対側に位置する前記基板120の第2箇所とを除去する工程と、前記第1接合領域270と前記第2接合領域280とに結晶質材料のエピタキシャル厚みを有する層を形成する工程とを含み、前記除去する工程と前記形成する工程は同一のチャンバ内で前記チャンバの封止を破ることなく行う。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】MISFETにおいて、信頼性寿命の低下を抑制する。

【解決手段】半導体装置100は、少なくとも1つのMISFETを備える。MISFETは、第1導電型の半導体基板101と、半導体基板101上にゲート絶縁膜104を介して形成されたゲート電極105と、半導体基板101におけるゲート電極105の側方に形成された第2導電型のソース領域106と、他方の側方に形成された第2導電型のドレイン領域107と、半導体基板101におけるゲート電極105の下方であり且つソース領域106及びドレイン領域107に挟まれたチャネル領域111とを備える。ゲート絶縁膜104は、ゲート電極105の底面下から側面上にまで亘って形成されている。チャネル領域111において、ドレイン領域107近傍の第1領域における不純物濃度は、チャネル領域111における第1領域以外の第2領域における不純物濃度に比べて低い。

(もっと読む)

半導体装置、試験装置、および製造方法

【課題】閾値変動を抑えつつ、ゲートリーク電流を低減させた窒化物半導体HEMT。

【解決手段】窒化物系半導体で形成された半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、を備え、ゲート絶縁膜は、酸窒化膜で形成された第1絶縁膜と、タンタル、ハフニウム、ハフニウムアルミニウム、ランタン、およびイットリウムの少なくとも1つを含む第2絶縁膜と、を有する半導体装置を提供する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリ・オフ動作に適したMIS型を採用するも、電流コラプス特性を大幅に向上させて、デバイス効率及び耐圧に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成されたゲート絶縁膜6と、ゲート電極7とを含み、ゲート電極7は、ゲート絶縁膜6上に形成されたゲート基部7aと、ゲート基部7a上に形成されたゲート傘部7bとを有しており、ゲート傘部7bの下面が化合物半導体積層構造2とショットキー接触する。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

21 - 40 / 873

[ Back to top ]