Fターム[5F140BD13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | 金属酸化膜 (2,702) | 複合金属酸化膜 (873)

Fターム[5F140BD13]に分類される特許

81 - 100 / 873

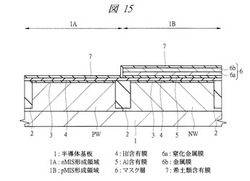

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】工数を大幅に増加せず且つ高誘電体からなるゲート絶縁膜にダメージを与えることがない、仕事関数変更用金属不純物膜の効果を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたp型活性領域110と、p型活性領域110の上に形成されたゲート絶縁膜150と、ゲート絶縁膜150の上に形成されたゲート電極106とを有している。ゲート絶縁膜150は、二酸化シリコンよりも大きい誘電率を有する高誘電体膜103と、高誘電体膜103の上に形成され、炭素を含む炭素含有膜104とを有している。高誘電体膜103及び炭素含有膜104は、第1の金属としてランタン又はマグネシウムを含み、ゲート電極106は、第2の金属を含む。

(もっと読む)

半導体装置の製造方法

【課題】キャップ材料を使用した半導体装置のウェハ面内における閾値電圧Vtのバラツキを抑制することを目的とする。

【解決手段】まず、半導体基板1001の上に、高誘電率ゲート絶縁膜1006及び第1のキャップ膜1008を順に形成する。次に、熱処理を行って、第1のキャップ膜1008中の第1の金属を高誘電体膜1006に拡散させる。その後、高誘電体膜1006に拡散せずに高誘電体膜1006の上に残存した第1のキャップ膜1008を除去して、第1の金属が拡散した高誘電率ゲート絶縁膜1006Aの上に金属電極1010を形成する。

(もっと読む)

ノーマリオフ型GaN系電界効果トランジスタ

【課題】ゲート耐電圧が高くかつオン抵抗が低減されたノーマリオフ型GaN系FETを提供する。

【解決手段】ノーマリオフ型GaN系FETは、第1種GaN系半導体からなるチャネル層4と、このチャネル層上で互いに隔てて設けられた第2種GaN系半導体からなる一対の電子供給層5と、これら電子供給層の間でチャネル層を覆うゲート絶縁膜7と、チャネル層にオーミックコンタクトしているソース電極およびドレイン電極と、ゲート絶縁膜上に形成されたゲート電極とを備え、ゲート絶縁膜はチャネル層上に順次堆積された第1と第2の絶縁層を含み、第1絶縁層7aはSiの酸化物、窒化物および酸窒化物のいずれかからなりかつ5nm以下の厚さを有し、第2絶縁層7bは第1絶縁層に比べて大きなε×Ecを有し、ここでεは誘電率を表し、Ecは絶縁破壊電界を表している。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な電気的特性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜20と、ゲート絶縁膜上に形成されたキャップ膜22と、キャップ膜上に形成されたシリコン酸化膜23と、シリコン酸化膜上に形成された金属ゲート電極24と、金属ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層48とを有している。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】低閾値動作が可能な電界効果トランジスタを提供する。

【解決手段】n型半導体領域2と、半導体領域に離間して形成されたソース領域およびドレイン領域12a、12bと、ソース領域12aとドレイン領域12bとの間の半導体領域上に形成され、シリコンと酸素を含む第1絶縁膜4と、第1絶縁膜上に形成され、Hf、Zr、Tiから選ばれた少なくとも1つの物質と酸素を含む第2絶縁膜8と、第2絶縁膜上に形成されたゲート電極10と、を備え、第1絶縁膜と第2絶縁膜との界面7aを含む界面領域7に、Geが導入されており、Geの面密度が、界面領域7内の第1絶縁膜4側においてピークを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチング量を少なくしても素子分離膜の周辺にHigh−kゲート絶縁膜材料やゲート電極材料が残ることを抑制できるようにする。

【解決手段】素子分離膜102はSTI構造を有しており、基板101に埋め込まれており、かつトランジスタが形成される素子形成領域を分離している。素子分離膜102の側面の上端は、トランジスタのチャネル形成層よりも上に位置しており、かつチャネル形成層の表面から素子分離膜102の側面の最上部までの高さhが35nm以下である。また素子分離膜102のうちチャネル形成層よりも上に位置している部分の側面は、基板の表面に対する角度θが80度以下である。

(もっと読む)

炭素ベース材料上の向上した結合界面を有する半導体構造体、その形成方法、及び、電子デバイス

【課題】 高密度で、構造部寸法がより小さく、より正確な形状の半導体構造体及び電子デバイスを提供する。

【解決手段】 炭素ベース材料の上面上に配置された少なくとも一層の界面誘電体材料を含む、半導体構造体及び電子デバイスが提供される。少なくとも一層の界面誘電体材料は、炭素ベース材料のものと同じである、典型的には六方晶短距離結晶結合構造を有し、従って、少なくとも一層の界面誘電体材料が、炭素ベース材料の電子構造を変えることはない。炭素ベース材料のものと同じ短距離結晶結合構造を有する少なくとも一層の界面誘電体材料の存在により、炭素ベース材料と、誘電体材料、導電性材料、又は誘電体材料及び導電性材料の組み合わせを含む、上にある任意の材料層との間の界面結合が改善される。その結果、改善された界面結合が、炭素ベース材料を含むデバイスの形成を容易にする。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】ゲート電極が金属窒化膜により構成されるMOSFETにおいて、電流駆動能力の向上を図る。

【解決手段】基板10に、素子形成領域20を分離する素子分離領域50を設ける。次に素子形成領域20上にゲート絶縁膜100を形成する。その後ゲート絶縁膜100上に金属窒化膜により構成される下部ゲート電極膜200を形成する。さらに下部ゲート電極膜200を熱処理する。そして下部ゲート電極膜200上に上部ゲート電極膜220を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】電界効果型トランジスタの閾値電圧を精度よく制御することができ、かつその範囲を広くする。

【解決手段】この半導体装置は、ゲート絶縁膜120及びゲート電極130を有する電界効果型トランジスタ101を備える。ゲート絶縁膜120は、界面層110と高誘電率膜112とを積層した構成を有している。高誘電率膜112は、酸化シリコンより誘電率が高い金属酸化物からなる。そしてゲート絶縁膜120は、高誘電率膜112と界面層110の界面近傍に、窒素を含有する窒素含有層を有している。窒素含有層は高誘電率膜112から界面層110に渡って形成されている。窒素含有層において、窒素の濃度は高誘電率膜112と界面層110の界面が最も高い。

(もっと読む)

金属窒化膜、該金属窒化膜を用いた半導体装置、および半導体装置の製造方法

【課題】所望の実効仕事関数(例えば、高い実効仕事関数)を実現し、かつ、EOTが変化しない、またはEOTの変化を低減した金属窒化膜、金属窒化膜を用いた半導体装置、および半導体装置の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る金属窒化膜は、TiとAlとNを含有し、該金属窒化膜のTiとAlとNのモル比率(N/(Ti+Al+N))が0.53以上であり、かつ、上記金属窒化物層のTiとAlとNのモル比率(Ti/(Ti+Al+N))が0.32以下であり、かつ上記金属窒化物層のTiとAlとNのモル比率(Al/(Ti+Al+N))が0.15以下である。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

強誘電性電界効果トランジスタデバイス

半導体装置およびその製造方法

【課題】界面準位を低減しつつ、電荷トラップに起因するヒステリシスを抑制できる半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置200は、GaNを含む半導体層101を表面の少なくとも一部に有する基板(半導体基板100)と、半導体層101と接するように半導体基板100上に設けられており、窒素を含まず、Alを含む酸化金属層からなる第1のゲート絶縁層(Al2O3膜114)と、Al2O3膜114上に設けられており、SiおよびOを含む第2のゲート絶縁層(SiO2膜116)と、SiO2膜116上に設けられたゲート電極118と、を備え、ゲート電極118の下面は、SiO2膜116に接しており、Al2O3膜114の膜厚は、SiO2膜116の膜厚より薄い。

(もっと読む)

半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板(シリコン基板7)上にゲート絶縁膜5とゲート電極膜(ポリシリコン膜3)とをこの順に形成し、ポリシリコン膜3上にハードマスク(第2のハードマスク2)を形成する工程と、第2のハードマスク2を用いて、ポリシリコン膜3を選択的にエッチングして、ゲート電極20を形成する工程と、ゲート絶縁膜5の側壁、ゲート電極20の側壁、第2のハードマスク2の側壁および上面上、ならびにシリコン基板7上に、第1の絶縁膜(第1のスペーサ用絶縁膜)を形成する工程と、異方性ドライエッチングを行うことにより、シリコン基板7上、ならびに第2のハードマスク2の上面上および側壁上の第1のスペーサ用絶縁膜を除去しつつ、ゲート絶縁膜5およびゲート電極20の側壁上に第1の絶縁膜(第1のスペーサ)を残す工程と、第2のハードマスク2を除去する工程と、ゲート電極20および第1のスペーサをマスクとしてシリコン基板7にイオン注入を行う工程と、を含む

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極に注入された不純物に起因するゲートリークを低減させる。

【解決手段】ゲート電極14が形成されたアクティブ領域による被覆率が50%以上かつその面積が0.02mm2以上の領域において、多結晶シリコン膜14´に炭素15を導入してから、多結晶シリコン膜14´にリン16を導入し、多結晶シリコン膜14´をパターニングすることにより、ゲート絶縁膜13上にゲート電極14を形成する。

(もっと読む)

ダイヤモンド半導体素子及びその製造方法

【課題】耐電圧、耐熱性、耐放射線性、及び高速性が優れ、かつ、チャネル領域を短くでき、素子の応答性が高いダイヤモンド半導体素子を高精度で製造できる半導体素子の製造方法を提供する。

【解決手段】第1のダイヤモンド半導体領域1の表面上に、絶縁膜2と多層金属電極層3と犠牲層4とを積層し、犠牲層4上に、局所的にレジスト5をパターン形成する。多層金属電極層3の最上層は、Pt又はPt合金により形成する。そして、レジスト5をマスクとして第1の犠牲層、多層金属電極層及び絶縁膜をエッチングした後、レジスト5を除去して、第1のダイヤモンド半導体領域1上に絶縁膜2と金属電極層3と第1の犠牲層4との積層体をパターン形成する。その後、第1のダイヤモンド半導体領域1上に、不純物の高濃度ドープ層7を形成する。その後、犠牲層4をエッチング除去し、高濃度ドープ層7上に金属電極8を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

81 - 100 / 873

[ Back to top ]