Fターム[5F140BE03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜の製造 (6,009) | ゲート絶縁膜を形成前の処理 (668) | エッチング (356)

Fターム[5F140BE03]に分類される特許

21 - 40 / 356

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】閾値電圧のバラつきを抑制する溝トランジスタを提供する。

【解決手段】図1に示すように、表面に少なくとも一つ以上の溝部250を有している半導体基板40と、溝部250の側壁を覆うように形成されたゲート絶縁膜20と、溝部250に埋めこまれているゲート電極10と、半導体基板40の表面に形成され、ゲート電極10を介して互いに対向しているソースおよびドレイン150と、を含み、溝部250の側壁には、複数の凸凹100が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させ、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

(もっと読む)

コーナートランジスターとその製作方法

【課題】改善された性能を有し、かつ縮小されたサイズを有することのできるコーナートランジスターを提供する。また、コーナートランジスターを製作する方法を提供し、それがトランジスターの性能を改善するとともに、簡単なプロセスを介して、そのサイズを縮小することができる。

【解決手段】この発明のコーナートランジスターを製作する方法を以下に記述する。分離構造(isolation structure)が基板中に形成されて能動エリア(active area)を定義する。処理プロセスが実施されて、能動エリア中の基板がそのトップエッジに鋭いコーナーを有するようにする。能動エリア中の基板がゲート誘電層により被覆される。ゲート導体がゲート誘電層上に形成される。ソース領域およびドレイン領域がゲート導体両側の基板中に形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体装置の、ソース・ドレイン間のオン抵抗を低減する。

【解決手段】ソース・ドレイン間を走行する窒化物半導体層と下地となる窒化物半導体層の間に、両窒化物半導体層より電子親和力が大きく、下地となる窒化物半導体よりも格子定数の大きい材料を形成する。その結果、ゲート電圧の印加によりゲート絶縁膜の下方に形成されるチャネルと、ゲート部以外で形成される二次元電子ガスを、深さ方向において近づけることができ、オン抵抗の低減が可能となる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

半導体装置の製造方法、並びにデータ処理システム

【課題】チャネル領域を拡大することが可能な半導体装置の製造方法を提供する。

【解決手段】素子分離用の溝部3を形成した後、素子分離絶縁膜4として、当該溝部3に埋め込まれた状態で基板2の面上を覆うシリコン酸化膜26,31を形成する工程と、シリコン酸化膜26,31上に少なくとも埋め込みゲート用の溝部10を形成する位置に開口部を有するマスクパターンを形成する工程と、マスクパターンの開口部を通してシリコン酸化膜31を異方性エッチングにより選択的に除去することによって、当該シリコン酸化膜31に第1の溝部9と同じ幅及び深さとなる第2の溝部10を形成する工程と、第2の溝部10の底面及び側面に位置するシリコン酸化膜26,31を等方性エッチングにより選択的に除去することによって、当該第2の溝部10を活性領域6に形成される第1の溝部9よりも深く、且つ、第1の溝部9よりも大きい幅とする工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】トレンチを均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、第1の材料からなる第1部分及び前記第1の材料とは異なる第2の材料からなる第2部分を含む被加工基材上に、前記第1部分の直上域に配置され第3の材料からなる第3部分及び前記第2部分の直上域に配置され前記第3の材料とは異なる第4の材料からなる第4部分を含み、前記第3部分及び前記第4部分の双方に開口部が形成されたマスク膜を形成する工程と、前記マスク膜をマスクとして、前記第4の材料のエッチングレートが前記第3の材料のエッチングレートよりも高く、前記第1の材料のエッチングレートが前記第2の材料のエッチングレートよりも高くなるような条件でエッチングを施すことにより、前記第1部分及び前記第2部分をそれぞれ選択的に除去する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

電界効果型トランジスタ

【課題】実用上十分なプロセスマージンを備える状態で、リーク電流の増大およびキャリア濃度の低下を招くことなく、ゲート電極とチャネル層との距離が短縮できるようにする。

【解決手段】InPからなる基板101の上に形成された電子供給層102と、電子供給層102の上に形成されたスペーサ層103と、スペーサ層103の上に形成されたチャネル層104と、チャネル層104の上に形成された障壁層105とを備え、障壁層105は、GaおよびAlの少なくとも1つと、Inと、Pとを含んだアンドープの化合物半導体から構成し、InPよりショットキー障壁高さが高いものとされている。

(もっと読む)

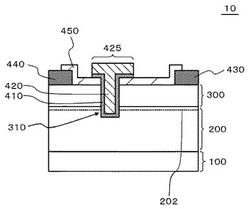

半導体装置の製造方法

【課題】ゲート絶縁膜に劣化が生じることを抑制する。

【解決手段】ハードマスクを用いて素子分離溝102を形成した後、素子分離溝102に素子分離膜20を埋め込む。次いで、ハードマスクの窒化シリコン膜210を除去する。次いで、ハードマスクの表面酸化膜200を薄くする。その後、シリコン基板100を熱酸化することにより、表面酸化膜を厚くして再酸化膜202を形成する。次いで、第1素子形成領域101及び第2素子形成領域103に位置するシリコン基板に、再酸化膜202を介してチャネル不純物を注入する。次いで、再酸化膜202を除去する。次いで、第1素子形成領域101に位置するシリコン基板100に、ゲート絶縁膜110及びゲート電極120を形成する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ横型パワーMOSFETにおいて、装置の信頼性を高めること。

【解決手段】半導体基板1の表面層にトレンチ5を形成する。トレンチ5は、半導体基板1の表面層を第1メサ領域41と第2メサ領域42に分割し、かつ第1メサ領域41と第2メサ領域42を交互に配置させる。第1メサ領域41および第2メサ領域42は、それぞれソース電流およびドレイン電流の引き出しをおこなう。第2メサ領域42は、半導体基板1からの深さが、第1メサ領域41よりも深くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、接合リーク電流を低減可能で、かつトランジスタの信頼性を向上させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極61よりも上方に配置されたゲート絶縁膜21、及びゲート電極61の上面61aを覆う水素含有絶縁膜62と、水素含有絶縁膜62を介して、ゲート電極用溝17の上部17Bを埋め込むフッ素含有絶縁膜63と、を備え、ゲート絶縁膜21と接触する第1及び第2の不純物拡散領域65,66の面に、半導体基板13に含まれるシリコンと水素含有絶縁膜62に含まれる水素とが結合したSi−H結合、及び半導体基板13に含まれるシリコンとフッ素含有絶縁膜63に含まれるフッ素とが結合したSi−F結合を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

半導体素子、半導体素子の製造方法、およびトランジスタ回路

【課題】高電子移動度トランジスタの耐圧を高くする。

【解決手段】第1の高電子移動度トランジスタ4と、負の閾値電圧を有する第2の高電子移動度トランジスタ6とを有し、第2の高電子移動度トランジスタ6のソースS2は、第1の高電子移動度トランジスタ4のゲートG1に接続され、第2の高電子移動度トランジスタ6のゲートG2は、第1の高電子移動度トランジスタ4のソースS1に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】消費電力が低く、かつ、動作時の電流値が高い半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置は、第1導電型の基板上のソース領域に形成された第2導電型の第1の不純物拡散層と、前記基板上のポケット領域に形成された第1導電型の第2の不純物拡散層と、前記基板上のドレイン領域に形成された第1導電型の第3の不純物拡散層と、前記第1乃至第3の不純物拡散層の表面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲートと、を含む。前記ポケット領域は前記ソース領域に隣接し、リセスを有するように形成される。前記ゲートは、前記ゲート絶縁膜を介して前記リセスを埋め込むように前記ゲート絶縁膜上に形成される。

(もっと読む)

21 - 40 / 356

[ Back to top ]