Fターム[5F140BE03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜の製造 (6,009) | ゲート絶縁膜を形成前の処理 (668) | エッチング (356)

Fターム[5F140BE03]に分類される特許

121 - 140 / 356

半導体装置及びその製造方法

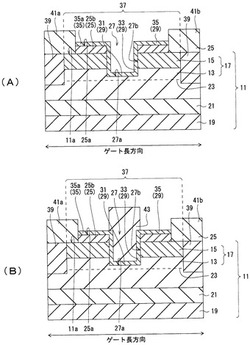

【課題】MIS−HEMTにおいて、閾値電圧の低下を抑制する。

【解決手段】半導体装置は、基板19と、この基板上に形成されており、電子走行層13及び電子供給層15が順次積層されて形成された積層構造体17とを含む下地11を具えている。この下地の下地面には、互いに離間し、かつ対向して第1及び第2主電極が形成されている。そして、下地面11aの、これら第1主電極41a及び第2主電極41b間に挟まれた領域内に、ゲート形成用凹部27が形成されている。更に、半導体装置はゲート絶縁膜29を具えている。そして、このゲート絶縁膜は、最小でも2.9g/cm3の結晶密度で形成されている。また、半導体装置は、ゲート絶縁膜が形成された前記ゲート形成用凹部を埋め込むゲート電極43を具えている。

(もっと読む)

半導体装置の製造方法

【課題】Geを含有する半導体基板に効果的な洗浄方法が適用された半導体装置の製造方法を提供する。

【解決手段】Geを含有する半導体基板を、HClガス、HBrガスまたはHIガスの少なくとも一種を含むハロゲン化ガスで洗浄処理を行うことを特徴とする半導体装置の製造方法。Geを含有する半導体基板を、75℃以上110℃以下のHCl溶液で洗浄処理を行うことを特徴とする半導体装置の製造方法。例えば、MISFETのゲート絶縁膜の前処理、ソース・ドレイン電極形成の前処理、コンタクトの金属プラグ形成の前処理に適用される。

(もっと読む)

半導体基板、半導体装置およびその製造方法

【課題】 (111)表面のシリコン(Si)基板に、原子レベルで超平坦な表面を実現する。

【解決手段】 シリコン基板(111)表面を、予め、フッ化アンモニウム(NH4F)溶液で表面処理した後、濃度68%,沸点120.7℃の共沸硝酸溶液内に浸漬して、前記シリコン基板表面に二酸化シリコン(SiO2)主体の被膜を形成し、ついで、濃度40重量%のフッ化アンモニウム(NH4F)溶液で上記二酸化シリコン(SiO2)主体の被膜をエッチング除去する。AFM像では、バイレイヤー ステップが観測され、表面粗さの指標(RMSラフネス値)が0.07nmと判定され、原子レベルでの超平坦な表面が形成できた。

(もっと読む)

絶縁ゲート型半導体装置およびその製造方法

【課題】 絶縁ゲート型半導体素子が形成されるウェル領域は拡散領域であり、その底部ほど不純物濃度が薄くなり、抵抗が増加する問題がある。このため特に、アップドレイン構造の絶縁ゲート型半導体素子ではオン抵抗が増加する問題があった。

【解決手段】 p型ウェル領域を、2つのp型不純物領域を積層することにより構成する。それぞれのp型不純物領域は、p型不純物を、異なる注入エネルギーでn型半導体層内部と表面に多段注入し、熱処理により同時に拡散してp型ウェル領域とする。これにより、表面からある程度の深さ(5μm程度)までの不純物プロファイルが略平坦なp型ウェル領域を得ることができ、その表面に形成されるチャネル層の特性変動も抑制できる。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース/ドレイン領域における接合部の耐圧を向上でき、寄生バイポーラトランジスタ特性の影響を低減できる半導体装置を提供する。

【解決手段】(a)に示す低耐圧トランジスタは、ソース/ドレイン領域13,14間の基板11の第1領域上に形成されたゲート絶縁膜15及び第1ゲート電極16と、ソース/ドレイン領域13,14上のシリサイド層13A,14Aとを備える。(b)に示す高耐圧トランジスタは、ソース/ドレイン領域23,24間の基板11の表面が所定の深さ除去された第2領域上に形成された、ゲート絶縁膜15より膜厚が厚いゲート絶縁膜25、及び第2ゲート電極16と、ソース/ドレイン領域23,24上のシリサイド層23A,24Aとを備える。所定の深さはゲート絶縁膜25とゲート絶縁膜15との厚さの差に相当し、シリサイド層23A,24Aの上面は基板11の第2領域とゲート絶縁膜25との界面より高い構造を有する。

(もっと読む)

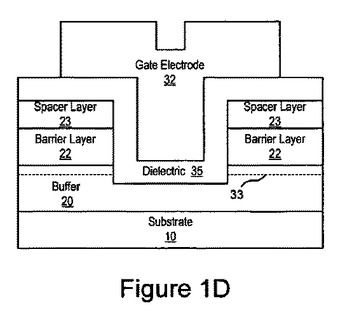

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】金属ゲートを形成した後に形成される絶縁膜中の水素の影響を抑制して、しきい値電圧Vthを所望の値(例えば0.3V)以下にすることを可能にする。

【解決手段】半導体基板11上に第1絶縁膜41が形成され、第1絶縁膜41に溝部42が形成され、溝部42の第1絶縁膜41側の半導体基板11上にサイドウォールスペーサ31が形成され、溝部42内にゲート絶縁膜21を介してゲート電極22が形成され、ゲート電極22の両側の半導体基板11にエクステンション領域23,24を介してソース・ドレイン領域25,26が形成され、第1絶縁膜41上にゲート電極22上を被覆する第2絶縁膜43を有し、サイドウォールスペーサ31は水素の通過を阻止する絶縁膜からなり、ゲート電極22上に水素の通過を阻止する水素バリア膜33が形成され、水素バリア膜33はゲート電極22上の周囲でサイドウォールスペーサ31と接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】パンチスルーの発生を抑制すると共に、ソース、ドレインの寄生容量を低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】凹部13が形成された半導体基板1と、凹部13の底面上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成されたゲート電極5と、ゲート電極5とその直下6とを含む領域の両側の半導体基板1にそれぞれ形成された第1導電型のS/D層7と、半導体基板1に形成された第2導電型のハロー層9と、を備え、S/D層7は、凹部13の直下の領域に形成された低濃度の第1不純物層7aと、凹部13の側面に隣接する領域に形成された高濃度の第2不純物層7bと、を有し、ハロー層9は、第1不純物層7aの直下の領域に形成され、且つ第2不純物層7bの直下の領域には形成されていない。

(もっと読む)

半導体装置およびその製造方法

【課題】 高OFF耐圧および低ON抵抗を実現し、かつ小形化が可能な半導体装置およびその製造方法を提供する。

【解決手段】 ゲート電極4Aをドレイン側N-拡散層2b上まで設けることによって、ゲート電極4Aに電圧が印加されるON状態において、ドレイン側N-拡散層2bにキャリアを誘起することができるので、前提技術に比べて、ON抵抗を低下させることができる。これによって、第1ゲート絶縁膜6A上の部分と、ドレインN+拡散層5との離隔距離であるドレインオフセット長DL2を小さくすることなく、ON抵抗を低下させることができる。したがって、ドレインオフセット長DL2を前提技術のドレインオフセット長DL1と同程度に維持することができるので、ゲート電極4Aに電圧が印加されないOFF状態では、前提技術とほぼ同じOFF耐圧を得ることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置及びその製造方法

【課題】フィールド・プレート電極下の絶縁膜における電界集中を抑制することを課題とする。

【解決手段】本発明に係る半導体装置の製造方法は、表面に素子分離層形成領域と保護絶縁膜形成領域とを備えた半導体基板を準備する工程と;前記表面を覆う酸化膜を形成する工程と;前記酸化膜を覆う窒化膜を形成する工程と;前記素子分離形成領域上の前記絶縁膜を開口すると共に、前記保護絶縁膜形成領域上の前記絶縁膜に前記保護絶縁膜形成領域上の酸化膜を部分的に開口する開口パターンを形成する工程と;前記酸化膜を熱酸化させて、前記保護絶縁膜上に保護絶縁膜を形成し、前記素子分離層形成領域上に素子分離層を形成する工程と;前記窒化膜を除去する工程と;前記半導体基板の表面上に前記保護絶縁膜に接続するゲート絶縁膜を形成する工程と;前記ゲート絶縁膜上及び前記保護絶縁膜上に跨るゲート電極を形成する工程とを有することを特徴とする。

(もっと読む)

半導体素子のトリプルゲート形成方法

【課題】プラズマのエッチング工程によって発生する素子特性および信頼性の劣化を防止することのできる半導体素子のゲート形成方法と、プラズマのエッチング工程によって発生する上部の隅部における電界の集中現象を防止することのできる半導体素子のゲート形成方法を提供すること。

【解決手段】支持基板と、埋め込み絶縁層および半導体層からなる基板を備えるステップと、蒸気エッチング工程で前記半導体層をエッチングして互いに離隔した第1トレンチおよび第2トレンチを形成するステップと、前記第1トレンチおよび第2トレンチを備える前記基板の上面にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上にゲート導電膜を形成するステップとを含む半導体素子のトリプルゲート形成方法を提供する。

(もっと読む)

MOS電界効果トランジスタおよびその製造方法

【課題】少ない工程でオーミック抵抗が小さく、界面準位が少なく、移動度が大きい窒化物系III−V族化合物半導体を用いたノーマリオフ型のMOS電界効果トランジスタおよびその製造方法を提供することを課題とする。

【解決手段】窒素面を有するストレス緩和されたAlN層、前記AlN層の窒素面上に形成されたAlxGa1-xN(0≦x<1)層、前記AlxGa1-xN層上に形成されたオーミック電極からなるソース/ドレイン電極、前記ソース/ドレイン電極間に形成された酸化領域、および前記酸化領域上に形成されたゲート電極を有することを特徴とするMOS電界効果トランジスタにより、上記の課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート酸化膜の信頼性を阻害せずに、ゲート電極の低抵抗化を実現可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、炭化珪素からなり、表面にエピタキシャル結晶成長層2が形成された半導体基板1と、エピタキシャル結晶成長層2上部に選択的に形成されたウェル領域3とを備える。そして、ウェル領域3上部に選択的に形成されたソース領域4と、ソース領域4とエピタキシャル結晶成長層2とに挟まれたウェル領域3の表面を覆うゲート絶縁膜6上に形成されたゲート電極7とを備える。ゲート電極7は、珪素層7aと、炭化珪素層7bとの積層構造からなり、ゲート電極7上部に形成されたシリサイド層7cをさらに備える。

(もっと読む)

絶縁ゲート型半導体装置およびその製造方法

【課題】 絶縁ゲート型半導体素子が形成されるウェル領域は拡散領域であり、その底部ほど不純物濃度が薄くなり、抵抗が増加する問題がある。このため特に、アップドレイン構造の絶縁ゲート型半導体素子ではオン抵抗が増加する問題があった。

【解決手段】 p型ウェル領域を、2つのp型不純物領域を積層することにより構成する。それぞれのp型不純物領域は、表面にp型不純物を注入したn型半導体層を順次積層し、熱処理により同時に拡散してp型ウェル領域とする。これにより、所望の耐圧を確保するのに十分な不純物濃度が所望の深さまで略均一なp型ウェル領域を得ることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】動作特性の制御が容易で微細化に有利なトランジスタを有する半導体装置およびその製造方法を提供する。

【解決手段】活性領域K内に設けられたトレンチ100と、トレンチ100と素子分離領域Sとの間の活性領域Kに形成されたフィン型チャネル領域185と、トレンチ100に埋設され、ゲート絶縁膜191を介してフィン型チャネル185と接するゲート電極225と、フィン型チャネル185と接続され、活性領域K内においてゲート電極225を挟んでトレンチ100の両側に位置するソース/ドレイン拡散領域241と、を具備してなり、ソース/ドレイン拡散領域241と半導体基板101の接合部241aは、フィン型チャネル領域185の最下端部185aより深い位置にあることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【目的】耐圧とオン抵抗のトレードオフを改善し、高耐圧で低オン抵抗のトレンチ横型パワーMOSFETなどの半導体装置およびその製造方法を提供する。

【解決手段】ピラー部30の側壁に局所的に厚い酸化膜10を形成し、さらにpリサーフ領域4と第2nドレイン領域8を形成することで、第2nドレイン領域8の不純物濃度を上げても高耐圧が得られると同時に低オン抵抗化を図ることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法並びにデータ処理システム

【課題】動作特性の制御が容易で微細化に有利なトランジスタを有する半導体装置およびその製造方法並びにデータ処理システムを提供する。

【解決手段】活性領域K内に設けられたトレンチ100と、トレンチ100と第1素子分離領域S1との間の活性領域Kに形成されたフィン型チャネル領域185と、第1素子分離領域S1に埋設され、第1ゲート絶縁膜141を介してフィン型チャネル185と接する第1ゲート電極151と、トレンチ100に埋設され、第2ゲート絶縁膜191を介してフィン型チャネル185と接する第2ゲート電極225と、フィン型チャネル185と接続され、活性領域K内において第2ゲート電極225を挟んでトレンチ100の両側に位置するソース/ドレイン拡散領域241とを具備してなるトレンチゲート型MOSトランジスタTrを有する半導体装置1を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】 トレンチを有する半導体装置の駆動能力を向上させる。

【解決手段】 トランジスタのL長と同じ距離かそれより短い距離の深さのトレンチを有すること、さらにトレンチの底部に埋め込み層を用いることで、ソース高濃度拡散層下端あるいはドレイン高濃度拡散層下端からトレンチ底面までの実効的なチャネル長をトレンチ上面のゲート長よりも短くすることができ、駆動能力を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 他の半導体素子とのオンチップ化が容易で高駆動能力を有する半導体装置を提供する。

【解決手段】 半導体基板1に設けられた第1導電型ウェル領域2に、トレンチ領域12を複数本設けられており、ソース電極10は、前記トレンチ領域12の間の基板表面に設けられた第2導電型ソース領域6とオーミック接合されている。また、第2導電型ソース領域6と隣接して第1導電型高濃度領域11が設けられており、第2導電型ソース領域6と共にソース電極10にバッティングコンタクトされ、基板電位が固定されるようになっている。第2導電型ドレイン領域5はトレンチ領域12の底部に設けられており、トレンチ領域12の内部に埋め込まれたドレイン電極9によって基板表面に取り出されている。ゲート電極4a、4b及びドレイン電極9に任意の電圧を印加することにより、第2導電型ソース領域6から第2導電型ドレイン領域5にキャリアが矢印8の方向流れ、半導体装置がオン状態となる。

(もっと読む)

121 - 140 / 356

[ Back to top ]