Fターム[5F140BF20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 金属 (2,560) | 金属化合物(窒化物、酸化物) (305)

Fターム[5F140BF20]に分類される特許

121 - 140 / 305

半導体装置

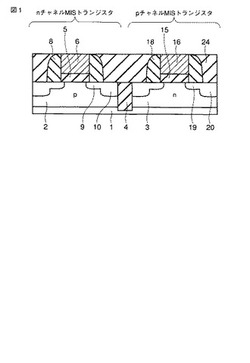

【課題】高い反転層キャリア移動度を有するシングルメタルCMISFETを提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板上に形成されたpチャネルMISトランジスタとnチャネルMISトランジスタとを具備し、pチャネルMISトランジスタとnチャネルMISトランジスタは、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極層を夫々備え、pチャネルMISトランジスタとnチャネルMISトランジスタのゲート電極における、少なくともゲート絶縁膜と接する最下層は、TaとCを含む同一組成を有し、CとTaとの合計に対するTaのモル比(Ta/(Ta+C))が0.5より大であり、最下層は同一配向性を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに容易な製造プロセスにより、微細で、高速且つ高性能なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1上に酸化膜2を介して、横方向エピタキシャル半導体層3が設けられ、素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。絶縁分離された横方向エピタキシャル半導体層3上に選択的に縦方向エピタキシャル半導体層7が設けられ、上部には高濃度ドレイン領域10及び低濃度ドレイン領域9が設けられ、下部には高濃度ソース領域8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられている。高濃度ドレイン領域10、高濃度ソース領域8及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている。

(もっと読む)

電界効果トランジスタの製造方法

【課題】所望の閾値まで低減させたnMOSFETおよびpMOSFETを簡易に製造できる電界効果トランジスタの製造方法を提供する。

【解決手段】pMOSFET領域に閾値制御膜としてAl2O3膜が少なくとも形成され、nMOSFET領域に閾値制御膜としてランタノイド系のフッ化酸化膜が形成されるとともに、閾値制御膜上にHfSiONによるゲート絶縁膜が形成される電界効果トランジスタの製造方法であって、nMOSFET領域では疎水性を示すSi基板101表面を露出させ、pMOSFET領域では親水性を示すAl2O3膜104bを露出させた状態で、LaOF膜を形成することによって、pMOSFET領域に形成されるLaOF膜105aの膜厚をnMOSFET領域に形成されるLaOF膜105bの膜厚よりも薄くする。

(もっと読む)

半導体素子製造方法および半導体素子

【課題】チャネルが上・下方向に形成されるピラーパターンの転倒現象を防止する半導体素子製造方法を提供する。

【解決手段】導電膜33Bをパターニングして複数の開放領域を形成するステップと、各々の開放領域の側壁にゲート絶縁膜41を形成するステップと、各々の開放領域内にピラーパターン42を形成するステップと、ピラーパターン42間の導電膜33Bをエッチングし、ピラーパターン各々を覆うゲート電極33Bを形成するステップを含む。ピラーパターン42を基板31のエッチングでない成長によって形成し、成長はあらかじめ形成された開放領域を埋め込む形態を取るためピラーパターン42の転倒現象を防止することができ、ひいては半導体素子の信頼性および安全性を向上させる。

(もっと読む)

半導体装置及びその製造方法

【課題】 高誘電率ゲート絶縁膜を用い、PMOS、NMOSに適したしきい値電圧を有するCMOSFETを実現する。

【解決手段】 潮解性のあるランタン酸化膜をキャップ膜として用いずに、ハフニウムを含有する絶縁膜111を形成する前にシリコン酸化膜104上にランタンを含有する絶縁膜を形成して、ハフニウムを含有する絶縁膜111で保護するとともに、エッチングによりダメージを受けたPMOS領域にSiGe層108をエピタキシャル成長させることによって、PMOS、NMOSそれぞれに適したしきい値電圧を有する構造を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】動作特性の制御が容易で微細化に有利なトランジスタを有する半導体装置およびその製造方法を提供する。

【解決手段】活性領域K内に設けられたトレンチ100と、トレンチ100と素子分離領域Sとの間の活性領域Kに形成されたフィン型チャネル領域185と、トレンチ100に埋設され、ゲート絶縁膜191を介してフィン型チャネル185と接するゲート電極225と、フィン型チャネル185と接続され、活性領域K内においてゲート電極225を挟んでトレンチ100の両側に位置するソース/ドレイン拡散領域241と、を具備してなり、ソース/ドレイン拡散領域241と半導体基板101の接合部241aは、フィン型チャネル領域185の最下端部185aより深い位置にあることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】精度良く形成された第1,第2のゲート電極を実現すると共に、ゲート幅方向の幅が縮小化された素子分離領域を実現する。

【解決手段】第1のMISトランジスタは、第1のゲート絶縁膜13a上に形成された第2の金属膜30aからなる第1のゲート電極30Aと、第1のゲート電極の側面上から第1の活性領域10aにおける第1のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第2のMISトランジスタは、第2のゲート絶縁膜13b上に形成され第1の金属膜14bと第1の金属膜上に形成された導電膜30bとからなる第2のゲート電極30Bと、第2のゲート電極の側面上から第2の活性領域における第2のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第1の金属膜と第2の金属膜とは、互いに異なる金属材料からなり、第1,第2のゲート電極の上面上には絶縁膜が形成されていない。

(もっと読む)

半導体装置およびその製造方法

【課題】酸化シリコン膜のエッチングに対するエッチング耐性を有する応力膜を形成することで、応力膜の上記エッチング時の膜減りを低減することを可能にする。

【解決手段】半導体基板11上にゲート電極形成溝23が形成されたサイドウォール絶縁膜21と、ゲート電極形成溝23内の半導体基板11上にゲート絶縁膜24を介して形成されたゲート電極25と、ゲート電極25の側壁にサイドウォール絶縁膜24を介して半導体基板11上に形成されていて応力を有する第1応力膜51と、第1応力膜51の外側の半導体基板11上に形成されていて第1応力膜51と同種の応力を有する第2応力膜52とを有し、第1応力膜51および第2応力膜52は酸化シリコン膜をエッチングするときのエッチング種に対するエッチング耐性を有し、第1応力膜51は第2応力膜52よりも前記エッチング種に対するエッチング耐性が強いことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みゲート電極脇の材料層の後退が防止され、これによって特性の向上が図られた半導体装置を提供する。

【解決手段】半導体基板1上に溝パターンaを有して設けられた絶縁膜100と、溝パターンaの内壁を覆う状態で設けられたゲート絶縁膜9と、ゲート絶縁膜9を介して溝パターンa内を埋め込むと共に、絶縁膜100上における溝パターンaの両側に溝パターンaよりも幅広に張り出して形成されたゲート電極101とを備えたことを特徴とする半導体装置104。

(もっと読む)

半導体装置及び半導体装置の製造方法並びにデータ処理システム

【課題】動作特性の制御が容易で微細化に有利なトランジスタを有する半導体装置およびその製造方法並びにデータ処理システムを提供する。

【解決手段】活性領域K内に設けられたトレンチ100と、トレンチ100と第1素子分離領域S1との間の活性領域Kに形成されたフィン型チャネル領域185と、第1素子分離領域S1に埋設され、第1ゲート絶縁膜141を介してフィン型チャネル185と接する第1ゲート電極151と、トレンチ100に埋設され、第2ゲート絶縁膜191を介してフィン型チャネル185と接する第2ゲート電極225と、フィン型チャネル185と接続され、活性領域K内において第2ゲート電極225を挟んでトレンチ100の両側に位置するソース/ドレイン拡散領域241とを具備してなるトレンチゲート型MOSトランジスタTrを有する半導体装置1を採用する。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電率ゲート絶縁膜とメタルゲート電極を用いたメタルゲートCMOSの製造方法を簡略化する。

【解決手段】 高誘電率ゲート絶縁膜6上にシリコン膜7を形成し、PMOS領域のシリコン膜7のみを選択的に窒化してSiN膜9に置換する。そしてNMOS領域上のシリコン膜7及びPMOS領域上のSiN膜9上にキャップ膜としてのLa(O)膜11及びメタル電極のW膜12を形成した後、加熱処理して、La(O)膜11のLa元素をNMOS領域の高誘電率ゲート絶縁膜に拡散させる。この際、PMOS領域においては、SiN膜9によりLa元素の拡散をブロックする。これにより、NMOSFETとPMOSFETの作りわけを容易に行える。また、窒化されやすい高誘電率ゲート絶縁膜6であれば、シリコン膜7を省略して、窒化処理によりPMOS領域の高誘電率ゲート絶縁膜6だけを選択的に窒化してもよい。

(もっと読む)

半導体装置

【課題】ゲルマニウム層に浅いn型不純物拡散領域を形成可能とした半導体装置を提供する。

【解決手段】ゲルマニウムを主成分とするp型半導体と、前記p型半導体の表面に選択的に設けられた一対のn型不純物拡散領域と、前記一対のn型不純物拡散領域により挟まれた前記p型半導体の上に設けられたゲート絶縁層と、前記ゲート絶縁層の上に設けられたゲート電極と、を備え、前記n型不純物拡散領域の少なくとも一部は、シリコン及び炭素から選択された少なくともいずれかの添加元素を含有していることを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに導電型の同じMISトランジスタを備えた半導体装置において、互いに閾値電圧の異なるMISトランジスタを精度良く且つ高性能に実現する。

【解決手段】第1のMISトランジスタLTrは、第1の活性領域1aに形成された第1のチャネル領域3aと、第1のチャネル領域上に形成された高誘電率絶縁膜からなる第1のゲート絶縁膜4aと、第1のゲート絶縁膜上に接する第1の導電部12aと、第2の導電部13aとを有する第1のゲート電極20Aとを備え、第2のMISトランジスタHTrは、第2の活性領域1bに形成された第2のチャネル領域3bと、第2のチャネル領域上に形成された高誘電率絶縁膜からなる第2のゲート絶縁膜4bと、第2のゲート絶縁膜上に接する第3の導電部12bと、第4の導電部13bとを有する第2のゲート電極20Bとを備え、第3の導電部は、第1の導電部よりも薄い膜厚で且つ第1の導電部と同じ組成材料からなる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】NMOSとPMOSとの境界を明確化して更なる微細化を可能とし、NMOSとPMOSとの閾値電圧を共に実用レベルの低い値に設定できる半導体装置を提供する。

【解決手段】 この半導体装置1は、ゲート電極Gnが金属シリサイド層111/La含有層105/ゲート絶縁膜103の積層構造のNMOSトランジスタと、ゲート電極Gpが前記金属シリサイド層111と同一組成の金属シリサイド層111/前記La含有層105と同一組成のLa含有層105/メタル層104/ゲート絶縁膜103の積層構造のPMOSトランジスタとを備える。

(もっと読む)

半導体素子のリセスゲート及びその製造方法

【課題】リセスゲート及びこれを含む半導体素子の製造方法を提供する。

【解決手段】半導体素子のリセスゲートは、基板110と、金属層165と、ポリシリコン層と、ポリシリコン層に隣接し、金属層165から離隔され、形成されたソース領域及びドレーン領域と、を含む。半導体素子の形成方法は、基板110の上にソース/ドレーン120層を形成する段階と、リセス112を形成し、第1導電層パターン145を形成する段階と、第1導電層パターン145上に第2導電層を形成する段階、ソース/ドレーン層120と重畳されるように第2導電層パターン156を形成する段階と、前記第2導電層パターン156と、前記ソース/ドレーン層120上に絶縁層を蒸着する段階と、第2導電層パターン156上にキャップを形成するように絶縁層を平坦化する段階と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】ソース及びドレイン領域の幅を確保しつつ、フィンチャネルの幅のみを狭く形成できる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】Fin型トランジスタの製造方法であって、シリコン基板1上に形成されたマスク層8をマスクとして、STI領域2を形成する工程と、マスク層8をウエットエッチングで縮退させて縮退マスク層8aを形成する工程と、縮退マスク層8aの表面にストッパ酸化膜16を形成し、全面にポリシリコン17を堆積した後、反射防止膜18、フォトレジスト19を形成する工程と、ワード線部分のフォトレジスト19を開口し、当該部分の反射防止膜18とポリシリコン17とを除去して、縮退マスク層8aを露出させた後に、フォトレジスト19を除去する工程と、縮退マスク層8aをマスクとして、縮退マスク層8aの下部両側のシリコン基板1をエッチングして、フィンチャネル30を形成する工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲートラストプロセスで形成されたゲート構造において、ソース・ドレイン領域に接続するコンタクトとゲート電極とのショートを防ぐ。

【解決手段】半導体装置100は、ゲートラストプロセスで形成された第1のゲート210を含む。第1のゲート210は、絶縁膜中に形成された第1の凹部内の底面に形成されたゲート絶縁膜、当該第1の凹部内のゲート絶縁膜上に形成されたゲート電極、および当該第1の凹部内のゲート電極上に形成された保護絶縁膜140を含む。また、半導体装置100は、第1のゲート210の両側方のN型不純物拡散領域116aに接続され、第1の凹部よりも径が大きい第2の凹部内に埋め込まれたコンタクト134を含む。

(もっと読む)

半導体装置および半導体装置を製造する方法

【課題】ソース・ドレイン領域の占有面積が小さい半導体装置およびそれを製造する方法を提供する。

【解決手段】本発明の半導体装置は、素子分離領域と活性領域を有する半導体装置であって、活性領域とゲート酸化膜が接する第1の面より上に、ソース領域およびドレイン領域の一部が存在し、該ソース領域および/または該ドレイン領域と、該ソース領域および/または該ドレイン領域に電気的に接続される電極とが接する第2の面が、該第1の面に対して傾いている。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率膜をゲート絶縁膜として用い、pチャネル型MISFETおよびnチャネル型MISFETのそれぞれに要求されるしきい値電圧を容易に実現できる相補型MISFETおよびその製造技術を提供する。

【解決手段】n型ウエル3およびp型ウエル4のそれぞれの表面に清浄な酸化シリコン膜5を形成した後、酸化シリコン膜5上に2A族元素の酸化物、3A族元素の酸化物、3B族元素の酸化物、4A族元素の酸化物、および5A族元素の酸化物等からなる酸素欠損調整層6と、高誘電率膜8と、水素に対する還元触媒効果を有する導電性膜12とを順次堆積し、H2を含む雰囲気中にて基板1に対して熱処理を施すことで酸素欠損調整層6と酸化シリコン膜5との間にダイポールを形成する。その後、導電性膜12、高誘電率膜8、酸素欠損調整層6および酸化シリコン膜5等をパターニングしてゲート電極およびゲート絶縁膜を形成する。

(もっと読む)

121 - 140 / 305

[ Back to top ]