Fターム[5F140BF20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 金属 (2,560) | 金属化合物(窒化物、酸化物) (305)

Fターム[5F140BF20]に分類される特許

101 - 120 / 305

半導体装置およびその製造方法

【課題】良好な形状のsingle metal/dual high−k構造を形成し、nMOS、pMOSそれぞれに適したフラットバンド電圧を得ることができる半導体装置を得ること。

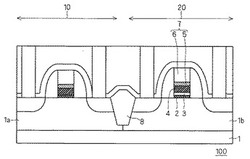

【解決手段】本発明の一実施形態における半導体装置100は、第1導電型のMOSFET10と、第2導電型のMOSFET20を有する。第1および第2導電型のMOSFET10,20は、半導体基板1上に形成された第1の絶縁膜2と、第1の絶縁膜2上に形成され、第1の絶縁膜2よりも誘電率の高い絶縁材料からなる第2の絶縁膜4と、第2の絶縁膜4上に形成され、第2の絶縁膜4に拡散して仕事関数を制御する材料を含むメタル層5を下層に有するゲート電極7と、を備える。また、第2導電型のMOSFET20は、第1の絶縁膜2と第2の絶縁膜4との間に形成され、仕事関数を制御する材料が第1の絶縁膜2界面に拡散するのを防止する拡散防止膜3をさらに備える。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル幅が狭い場合においても、eWFが十分に低減された閾値電圧が低い半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11と、半導体基板11の上に形成され、第1の元素と第2の元素とを含むゲート絶縁膜26と、ゲート絶縁膜26の上に形成されたゲート電極27とを備えている。ゲート絶縁膜26は、半導体基板11側においてゲート電極27側と比べて第1の元素の含有量が多く、ゲート電極27側において半導体基板11側と比べて第2の元素の含有量が多い。

(もっと読む)

MIS電界効果トランジスタ及び半導体基板の製造方法

【課題】高温特性を改善した高集積、高速且つ高性能なMISFETを得ること。

【解決手段】半導体基板に絶縁膜を埋め込んだトレンチ素子分離領域を選択的に設け、この絶縁分離された半導体基板上に、半導体基板と同じ第1の半導体を、筒状構造を有して縦方向にエピタキシャル成長させ、この第1の半導体層に自己整合して、格子定数がやや大きい第2の半導体を内側面の横方向にエピタキシャル成長させることにより、第1の半導体層に歪みを加える。この第2の半導体層の上部内側面を除く内側面に接して絶縁膜を設け、この絶縁膜の側面間を空孔となし、この空孔に栓をするように、第2の半導体層の上部内側面間に導電膜を設ける。歪み半導体層の外側面にはゲート絶縁膜を介してゲート電極を設ける。歪み半導体層及び第2の半導体層の上部にはドレイン領域を設け、歪み半導体層及び第2の半導体層の下部且つ半導体基板の表面にはソース領域を設けておき、配線体をそれぞれの領域に接続した縦型のMISFETを構成すること。

(もっと読む)

半導体装置の製造方法

【課題】ゲートラストプロセスで作製するトランジスタにおいて、活性領域と素子分離領域の高さばらつきのためゲートのポリシリコンを抜くことができないことにより、ゲートの抵抗にばらつきが生じるのを防ぐことを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、第1のゲート部30及び第2のゲート部31の上面が共に露出するように、酸化膜16、PMD19、及び第1のゲート部30又は第2のゲート部31の一部を研磨除去する工程、露出された部分より、ポリシリコン12を抜く工程、第1のゲート部30及び第2のゲート部31を覆うメタルを形成する工程を備える。また、第1のゲート部30及び第2のゲート部31の上面が共に露出するようにメタルを研磨除去し、第1のゲート部30と第2のゲート部31で厚みの異なるメタルを残す工程を備えて構成される。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】NMOSFET及びPMOSFET等のNMOS及びPMOSを有する半導体装置において、ゲート電極の実効仕事関数を、Siバンドギャップのmid-gap付近の値に安定的に設定することが可能な半導体装置及びその製造方法を提供する。

【解決手段】素子分離膜によって分離されてなる、p型拡散層及びn型拡散層を有する半導体基板と、前記半導体基板の、前記p型拡散層及びn型拡散層それぞれの上に形成されてなるゲート絶縁膜と、前記ゲート絶縁膜上に形成された金属膜を含むゲート電極と、前記ゲート絶縁膜と前記金属膜との界面に形成されたGe介在物と、前記金属膜上に形成されたシリコン含有層と、を具えるようにして半導体装置を構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】閾値電圧が制御されて、且つ特性のばらつきが抑制された半導体装置を提供する。

【解決手段】基板2と、STI素子分離領域3と、活性領域4と、活性領域4に形成された第1ゲートトレンチ5と、第1ゲートトレンチ5の底部に設けられた第2ゲートトレンチ6と、第1及び第2ゲートトレンチ5,6にゲート絶縁膜7を介して埋め込み形成されたゲート電極8と、第1ゲートトレンチ5の幅方向両側の活性領域4にイオンを注入することによって形成されたソース/ドレイン領域9とを備え、第2ゲートトレンチ6と第2ゲートトレンチ6の長手方向に位置するSTI素子分離領域3との間に、チャネルを構成するシリコン薄膜部10が設けられていることを特徴とする半導体装置1。

(もっと読む)

デュアル金属ゲートのコーナー部

【課題】 デュアル金属ゲートのコーナー部を有する改良された電界効果トランジスタを提供する。

【解決手段】 上記を鑑みて、改善された電界効果トランジスタ(FET)構造体、及び該構造体を形成する方法の実施形態が開示される。このFET構造体の実施形態の各々は、固有のゲート構造体を組み込む。具体的には、このゲート構造体は、FETチャネル領域の中央部分の上方の第1のセクションと、チャネル幅のエッジの上方(すなわち、チャネル領域と隣接する分離領域との間の界面の上方)の第2のセクションとを有する。第1のセクション及び第2のセクションは、これらが異なる有効仕事関数(すなわち、それぞれ第1の有効仕事関数及び第2の有効仕事関数)を有する点で異なる(すなわち、これらは、異なるゲート誘電体層及び/又は異なるゲート導体層を有する)。チャネル幅のエッジにおける閾値電圧が上昇することを確実にするように、異なる有効仕事関数が選択される。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】Hf及びZrの少なくともいずれかを含むゲート絶縁膜の膜質を安定させることができる半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、半導体層と、半導体層の上に設けられ、Hf及びZrの少なくともいずれかを含むゲート絶縁膜と、ゲート絶縁膜の上に設けられ、Hf及びZrの少なくともいずれかを含む炭窒化物を含むゲート電極と、を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】金属ゲートを形成した後に形成される絶縁膜中の水素の影響を抑制して、しきい値電圧Vthを所望の値(例えば0.3V)以下にすることを可能にする。

【解決手段】半導体基板11上に第1絶縁膜41が形成され、第1絶縁膜41に溝部42が形成され、溝部42の第1絶縁膜41側の半導体基板11上にサイドウォールスペーサ31が形成され、溝部42内にゲート絶縁膜21を介してゲート電極22が形成され、ゲート電極22の両側の半導体基板11にエクステンション領域23,24を介してソース・ドレイン領域25,26が形成され、第1絶縁膜41上にゲート電極22上を被覆する第2絶縁膜43を有し、サイドウォールスペーサ31は水素の通過を阻止する絶縁膜からなり、ゲート電極22上に水素の通過を阻止する水素バリア膜33が形成され、水素バリア膜33はゲート電極22上の周囲でサイドウォールスペーサ31と接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 高OFF耐圧および低ON抵抗を実現し、かつ小形化が可能な半導体装置およびその製造方法を提供する。

【解決手段】 ゲート電極4Aをドレイン側N-拡散層2b上まで設けることによって、ゲート電極4Aに電圧が印加されるON状態において、ドレイン側N-拡散層2bにキャリアを誘起することができるので、前提技術に比べて、ON抵抗を低下させることができる。これによって、第1ゲート絶縁膜6A上の部分と、ドレインN+拡散層5との離隔距離であるドレインオフセット長DL2を小さくすることなく、ON抵抗を低下させることができる。したがって、ドレインオフセット長DL2を前提技術のドレインオフセット長DL1と同程度に維持することができるので、ゲート電極4Aに電圧が印加されないOFF状態では、前提技術とほぼ同じOFF耐圧を得ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】短チャネル効果を抑制すると共に、MISトランジスタの駆動能力が劣化することを防止するMIS(Metal Inserted Semiconductor)トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10における活性領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第1の導電膜14、及び該第1の導電膜14上に形成された第2の導電膜15からなるゲート電極15Aと、活性領域10xにおける第2導電膜15の側方下に形成されたエクステンション領域16と、第1の導電膜14上に、第2の導電膜15の側面と接して形成された第1のサイドウォール17とを備え、第1の導電膜14のゲート長方向の長さは、第2の導電膜15のゲート長方向の長さよりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造を有するRC型トランジスタにおいて、しきい値電圧の低下を防止でき、さらに、しきい値電圧の制御や調整が容易にできる。

【解決手段】電界効果トランジスタを備えた半導体装置であって、電界効果トランジスタは、半導体基板1に形成された素子分離領域3によって仕切られた拡散層領域と、

その拡散層領域と交差するように設けられ、少なくとも一部が半導体基板1に形成されたゲート溝内に埋め込まれたゲート電極5と、拡散層領域内において、一方の側面がゲート電極5のうちゲート溝内に埋め込まれた部分と対向し、他方の側面が素子分離領域3の側面と接触するように形成されたSOI構造のチャネル層4とを有し、ソース・ドレイン領域として機能する不純物拡散層5がチャネル層4よりも上部に配置され、不純物拡散層5とチャネル層4とが離間して形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体材料を含むゲート絶縁膜とメタルゲート電極とを有する半導体装置の製造中にポリシリコンからなる残渣が素子分離領域上に生じる虞があり、不良の原因であった。

【解決手段】半導体基板10の第1の活性領域10a上には、高誘電体材料と第1の金属とを含有する第1のゲート絶縁膜13aと、下層導電膜15aと第1の導電膜18aと第1のシリコン膜19aとを有する第1のゲート電極30aとを備えた第1導電型の第1のトランジスタが形成されている。半導体基板10の第2の活性領域10b上には、高誘電体材料と第2の金属とを含有する第2のゲート絶縁膜13bと、第1の導電膜18aと同一の材料からなる第2の導電膜18bと第2のシリコン膜19bとを有する第2のゲート電極30bとを備えた第2導電型の第2のトランジスタが形成されている。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13、チャネル形成領域12、ゲート電極423、ゲート絶縁膜430を備え、ゲート絶縁膜430はゲート絶縁膜本体部430A及びゲート絶縁膜延在部430Bから構成されており、ゲート電極を構成する第1層431はゲート電極の側面部の途中まで薄膜状に形成されており、第2層の外側層432Aは第1層431の上に薄膜状に形成されており、第2層の内側層432Bは第2層の外側層で囲まれた部分を埋め込んでおり、第3層の外側層433Aは第2層の内側層、外側層、ゲート絶縁膜延在部を覆い、ゲート電極の頂面まで薄膜状に形成されており、第3層の内側層433Bはゲート電極の残部を占めている。

(もっと読む)

二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜の信頼性および半導体装置の性能を確保可能である半導体装置の製造方法および半導体装置を提供する。

【解決手段】本発明にかかる半導体装置の製造方法は、Si基板100上にゲート絶縁膜103を形成するゲート絶縁膜形成工程と、ゲート絶縁膜103上に第1の金属膜を形成する第1の金属膜形成工程と、第1の金属膜上に金属電極104を構成する第2の金属膜を形成する第2の金属膜形成工程と、熱処理を行なってゲート絶縁膜103と第1の金属膜との間にゲート絶縁膜103と第1の金属膜との反応膜118を形成する反応膜形成工程とを行なって、第1の金属膜形成工程時のゲート絶縁膜103の損傷を回復させている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数の半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置およびその半導体装置を容易に製造することのできる半導体装置の製造方法を提供する。

【解決手段】ゲート絶縁膜6の上面上に、全面的に、3〜30nmの厚みのゲート電極用金属膜Mを形成する。次に、ゲート電極用金属膜Mの上面のうちでnFET領域Rn内に属する部分にのみ、全面的に、ゲート電極用金属膜Mとは異種材料の、10nm以下の厚みのn側キャップ層8Aを形成する。その上で、熱処理を行って、n側キャップ層8Aを、その直下のゲート電極用金属膜M内に拡散・反応させて、nFET領域Rn内にn側ゲート電極用金属膜MAを形成する。それ以降は、ポリSi層を堆積した上で、ゲート電極加工を施す。

(もっと読む)

半導体装置

【課題】高い反転層キャリア移動度を有するシングルメタルCMISFETを提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板上に形成されたpチャネルMISトランジスタとnチャネルMISトランジスタとを具備し、pチャネルMISトランジスタとnチャネルMISトランジスタは、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極層を夫々備え、pチャネルMISトランジスタとnチャネルMISトランジスタのゲート電極における、少なくともゲート絶縁膜と接する最下層は、TaとCを含む同一組成を有し、CとTaとの合計に対するTaのモル比(Ta/(Ta+C))が0.5より大であり、最下層は同一配向性を有することを特徴とする。

(もっと読む)

101 - 120 / 305

[ Back to top ]