Fターム[5F140BF20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 金属 (2,560) | 金属化合物(窒化物、酸化物) (305)

Fターム[5F140BF20]に分類される特許

61 - 80 / 305

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

半導体装置の製造方法

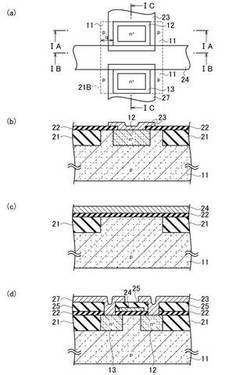

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート型FIN−FETにおいて、微細化に対してもFIN型トランジスタの利点を十分に発揮し、また、活性領域において十分なコンタクト面積を確保し、オン電流の低下を抑制したトレンチゲート型FIN−FETを提供する。

【解決手段】チャネル領域のFIN幅(162)を活性領域の幅(161)よりも狭くする。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、高誘電率膜を用いた相補型トランジスタの実効仕事関数を調整して適切なしきい値電圧を実現する際に、エッチング工程数を低減するとともに、エッチングダメージの発生を回避する。

【解決手段】 nチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第1のゲート絶縁膜と第1金属ゲート電極との間にアルミニウム膜を設けるとともに、pチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第2ゲート絶縁膜と第2金属ゲート電極との間に酸化アルミニウム膜を設ける。

(もっと読む)

電磁気素子の製造方法

【課題】レジスト残渣に起因するリーク電流の増大を生じさせることがなく、微細パターンの形成が可能であり、電極のエッジ部分の絶縁膜が薄くなることに起因するリーク電流の増大を抑制することが可能な電磁気素子の製造方法を提供すること。

【解決手段】基板上に、12(CaxSr1-x)O・7Al2O3(0≦x≦1)を含む絶縁膜を形成する絶縁膜形成工程と、絶縁膜の上にアンモニウム塩アルカリ溶液を含む現像液で現像可能な第1フォトレジストを塗布し、第1フォトマスクパターンに応じて第1フォトレジストを露光する第1フォトレジストパターン形成工程と、第1フォトレジストをアンモニウム塩アルカリ溶液を含む現像液に接触させ、第1フォトレジストの可溶部分の溶解と同時に、絶縁膜をエッチングする現像・エッチング工程とを備えた電磁気素子の製造方法。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】容易に製造できる半導体装置を提供する。

【解決手段】半導体装置は、PMOSトランジスタのゲート電極1pの仕事関数値が、High-kゲート絶縁膜16(16a)、及び、High-kゲート絶縁膜16・酸化シリコン膜15界面へのAlの拡散により調整されており、NMOSトランジスタのゲート電極1nの仕事関数値が、High-kゲート絶縁膜16・金属ゲート膜19間に挿入された、数原子層程度のAl層18により調整されている構成を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域を拡大し、駆動電流の増大を図ることを可能とした半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2に埋め込まれた埋込み絶縁膜3により絶縁分離された活性領域5と、活性領域5上に形成されたゲート絶縁膜6を介して当該活性領域5を跨ぐように形成されたゲート電極7と、ゲート電極7を挟んだ両側の活性領域5にイオン注入することによって形成されたソース領域8及びドレイン領域9とを備え、活性領域5に溝部10が設けられて、この溝部10の内側にゲート絶縁膜6を介してゲート電極7の一部が埋め込まれてなるトレンチ型のチャネル構造を有し、活性領域5の両側面に凹部11が対向して設けられて、これら凹部11の間に幅狭部12が形成されることによって、少なくとも溝部10の底面と幅狭部12との間に当該幅狭部12よりも幅広となるチャネル領域13が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体装置の製造方法

【課題】後続の工程に伴う埋め込みゲートの酸化を防止し、ビットラインコンタクト及びストレージノードコンタクトと基板との間のコンタクト面積を増加させ、コンタクト抵抗を低減し、ビットラインコンタクト及びストレージノードコンタクトと埋め込みゲートとの間のGIDLを低減し、自己整合コンタクト不良を防止することのできる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板の全面にプラグ導電膜を形成するステップと、前記プラグ導電膜をエッチングしてランディングプラグを形成するステップと、前記ランディングプラグ間の基板をエッチングしてトレンチを形成するステップと、前記トレンチの表面上にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上に前記トレンチの一部を埋め込む埋め込みゲートを形成するステップと、を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体絶縁膜及びメタルゲート電極を有する半導体装置において、高仕事関数を得ると共にNBTI信頼性劣化を低減する。

【解決手段】半導体装置100において、基板101上に、高誘電体ゲート絶縁膜109を介してメタルゲート電極110が形成されている。高誘電体ゲート絶縁膜109とメタルゲート電極110との界面におけるメタルゲート電極110の側に、ハロゲン元素が偏析している。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、極めて高い歩留まりでゲート電極について均一で十分なフル・シリサイド化を確実に実現する。

【解決手段】ゲート電極104a,104b及びソース/ドレイン領域107a,107bのNiシリサイド化を行うに際して、1回目のNiシリサイド化の後に1回目のmsecアニール処理であるフラッシュランプアニール処理を行い、2回目のNiシリサイド化、更には必要であれば2回目のフラッシュランプアニール処理を行って、ソース/ドレイン領域107a,107b上には1回目のフラッシュランプアニール処理で形成されたNiSi層111bを維持した状態で、フル・シリサイドゲート電極115a,115bを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、最適な仕事関数を有するメタルゲート電極を持つ半導体装置及びその製造方法に関する。

【解決手段】n チャネルMIS トランジスタを含む半導体装置であり、n チャネルMIS トランジスタは、基板上に形成されたp 型半導体領域、p 型半導体領域に形成されたソース領域102及びドレイン領域104、ソース領域102及びドレイン領域104間のp 型半導体領域上に形成されたゲート絶縁膜106、ゲート絶縁膜106上に形成された金属層108及び化合物層110からなる積層構造を持つゲート電極を有する。金属層108は2 nm未満の厚さ及び4.3 eV以下の仕事関数を有し、化合物層110は4.4 eVを越える仕事関数を有しかつAl及び金属層108とは異なる金属を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】High-k/metalゲート電極構造において各極性のFETに要求される仕事関数値を実現する。

【解決手段】第1の領域と第2の領域とを有する半導体基板101の上にゲート絶縁膜103を形成する。次に、ゲート絶縁膜103の上に第1の金属窒化膜105を堆積する。次に、第1の金属窒化膜105における第2の領域に位置する部分を除去することにより、ゲート絶縁膜103における第2の領域に位置する部分を露出させる。次に、ゲート絶縁膜103における第2の領域に位置する部分の上に、第1の金属窒化膜105と同じ金属窒化物からなる第2の金属窒化膜107を形成する。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】酸化処理前における基板表面の初期酸化を抑えることができるとともに、自然酸化膜を除去できるようにする。

【解決手段】基板を処理室内に搬入する工程と、処理室内に酸素含有ガスと水素含有ガスとを供給して前記基板を処理する工程と、処理後の基板を処理室内より搬出する工程とを有し、処理工程では、処理室内の圧力を大気圧未満の圧力として処理室内に水素含有ガスを先行して導入し、続いて水素含有ガスの導入を維持した状態で酸素含有ガスを導入し、その後、水素含有ガスの導入を維持した状態で酸素含有ガスの導入を停止する。

(もっと読む)

半導体ウエハを処理するための方法

【課題】

【解決手段】半導体ウエハを処理するための方法であって:ハフニウムおよび/またはジルコニウムを含む第1の酸化物材料を含む高誘電体層と;前記高誘電体層の上部に蒸着され、ランタン、ランタニド、および/または、アルミニウムを含む第2の酸化物材料を含むキャップ層と、を備えたスタックを準備する工程と;酸化剤を含む水溶液である液体Aを前記半導体ウエハの表面に供給する工程SAと;工程SAの後に、6未満のpH値の液体である液体Bを前記半導体ウエハの前記表面に供給する工程SBと;工程SBの後に、少なくとも10ppmのフッ素濃度の酸性水溶液である液体Cを前記半導体ウエハの前記表面に供給する工程SCとを備える方法が開示されている。

(もっと読む)

半導体装置及びその製造方法

【課題】導電型に応じて容易に構成を変えることが可能なFinトランジスタ及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に設けられた凸状の半導体からなるトランジスタ活性領域104と、トランジスタ活性領域104の一部の側面上及び上面上に設けられたゲート絶縁膜105aと、ゲート絶縁膜105aを間に挟んでトランジスタ活性領域104の側面及び上面の一部上に設けられたゲート電極350とを備えている。ゲート電極350のうち、トランジスタ活性領域104の側面上に設けられた部分の構成とトランジスタ活性領域104の上面上に設けられた部分の構成とは互いに異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】PMISトランジスタのソースドレイン電極に高濃度のゲルマニウムを含むシリコンゲルマニウム層を用いても、シリコンゲルマニウム層に格子緩和を生じさせることなく、ソースドレイン電極の上部にシリコン層又は金属シリサイド層を形成できるようにする。

【解決手段】半導体装置は、n型半導体領域100の上にゲート絶縁膜101を介在させて形成されたゲート電極102と、その両側方に形成されたp型のソースドレイン電極150とを有している。ソースドレイン電極150は、n型半導体領域100に設けられた各リセス部100aに、その底部から少なくともチャネル領域の深さにまで形成されたシリコンゲルマニウム層111と、その上に形成され、炭素とシリコンゲルマニウム層のゲルマニウム濃度よりも低いゲルマニウムとを含むカーボンドープドシリコンゲルマニウム層112と、その上に形成された金属シリサイド層115とから構成される。

(もっと読む)

61 - 80 / 305

[ Back to top ]