Fターム[5F140BF20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 金属 (2,560) | 金属化合物(窒化物、酸化物) (305)

Fターム[5F140BF20]に分類される特許

141 - 160 / 305

半導体装置及びその製造方法

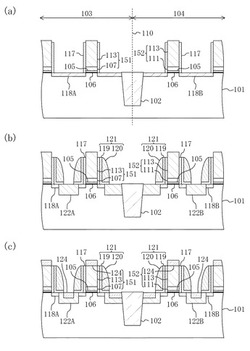

【課題】nチャネル及びpチャネルのゲート構造が異なり且つメタルゲート電極を有する半導体装置において、ゲート電極パターン形成時のドライエッチングでゲート絶縁膜の突き抜けが発生しないようにする。

【解決手段】ゲート絶縁膜105と接する第2ゲート電極材料膜(TiN膜)111がゲート電極151の一部として形成されないnチャネル領域103上に、第2ゲート電極材料膜(TiN膜)111のエッチング時にオーバーエッチング吸収層として機能する第1ゲート電極材料膜(ポリシリコン膜)107を予め形成しておく。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】仕事関数が所望の値に制御されたメタルゲート電極を備える半導体装置を提供する。

【解決手段】半導体基板2上に、ゲート絶縁膜4を介して、N等を含有する仕事関数制御層5、SiまたはAlを含んだ中間層6、およびMoN層等の低抵抗層7が積層された構造を有するメタルゲート電極を形成する。その形成時には、ゲート絶縁膜4上に仕事関数制御層5、中間層6および低抵抗層7の各層の積層後、ゲート加工を行い、LDD領域9、サイドウォール8およびソース・ドレイン領域10を順に形成して、半導体基板2に導入した不純物の活性化アニールを行う。仕事関数制御層5と低抵抗層7との間に中間層6を設けたことにより、仕事関数制御層5へのあるいは仕事関数制御層5からのN等の拡散が抑制され、その仕事関数の変動が抑制されるようになる。

(もっと読む)

半導体装置の製造方法

【課題】溝の形状を維持しながらバリを除去するとともに、溝内壁におけるシリコン表面のダメージを除去することが可能な半導体装置の製造方法、及び該製造方法によって製造された半導体装置を提供する。

【解決手段】基板1に埋設領域Mを形成して素子分離を行なう工程と、基板1に溝7a,7b,7cのパターンを形成する工程と、溝7a,7b,7c内壁に保護膜8を形成する工程と、異方性の強い条件でエッチバックすることにより、溝7a,7b,7cのゲート垂直方向側壁7dの一部に保護膜8を残しながら、溝7a,7b,7cのゲート平行方向内壁7eの保護膜8を除去する工程と、保護膜8の除去によってシリコンが露出した領域に水素ベーク処理を行って、溝7a,7b,7cのパターン形成の際に副生されたバリ1a,1aを除去する工程と、を少なくとも有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動能力を低下させることなく、半導体装置内部の高電界が与える影響によって生じるGIDLを低減する。

【解決手段】ゲート電極108は、ゲート電極108のチャネル長方向の中央部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第1の導電部108Aと、ゲート電極108のチャネル長方向の両端部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第2の導電部108Bとを含む。第1の導電部108Aの第1の仕事関数と第2の導電部108Bの第2の仕事関数とが異なっている。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜が大気やメタル電極のエッチング液等に曝されて劣化することなく、仕事関数の異なるnMOS、pMOSに適したメタルゲートMISFETを含む半導体装置の製造方法を提供する。

【解決手段】 メタル電極を有するn型MISトランジスタ及びp型MISトランジスタを備えた半導体装置の製造方法であって、単結晶シリコン基板100上に設けられたゲート絶縁膜102と、ゲート絶縁膜102上に設けられた第一の金属膜103、第二の金属膜104、第三の金属膜105、導電層106を備えたゲート電極108とを備えた構造であって、熱工程によって第二の金属膜104の構成元素を第一の金属膜103を通してゲート絶縁膜102中へ拡散させることによって、n型MISトランジスタ及びp型MISトランジスタそれぞれに適した仕事関数に変化させる。

(もっと読む)

nチャネルMOSトランジスタおよびその製造方法、半導体装置

【課題】ゲートファーストプロセスで形成できる、金属化合物をゲート電極パターンとして使うnチャネルMOSトランジスタにおいて、pチャネルMOSトランジスタのゲート電極パターンに使われる金属化合物に対し、前記nチャネルMOSトランジスタのゲート電極パターンに使われる金属化合物の仕事関数差を増大させる。

【解決手段】nチャネルMOSトランジスタは、p型シリコン活性領域上にゲート絶縁膜を介して形成された導電性金属窒化物よりなるゲート電極パターンと、前記p型シリコン活性領域中、前記ゲート電極パターンの一方および他方の側にそれぞれ形成されたn型のソースおよびドレイン領域と、を含み、前記導電性金属窒化物は、SiおよびV族元素を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】高速高周波動作に適した信頼性の高い半導体装置を得ること。

【解決手段】シリコン基板11の表面層に拡張ドレイン領域12とウェル領域13を形成し、拡張ドレイン領域12上に絶縁層20を形成する。その絶縁層20の側壁に犠牲スペーサー領域を形成し、犠牲スペーサー領域をマスクとしてウェル領域13の表面層に自己整合的に窒素を注入し熱処理を行う。犠牲スペーサー領域を除去した後に熱酸化を行ってゲート酸化膜21,22を形成する。窒素が注入された部分のシリコンの酸化速度は、窒素が注入されていない部分のシリコンの酸化速度と同じか、それよりも低下する。窒素は、絶縁層20の側壁の犠牲スペーサー領域の下には注入されないので、厚い絶縁層20に接続する部分のゲート酸化膜21の厚さが、それ以外の部分のゲート酸化膜22の厚さと同じか、それよりも厚くなる。

(もっと読む)

半導体集積回路装置

【課題】基板とゲート絶縁膜との界面近傍における窒素濃度を必要以上に高くすることなく、ゲート絶縁膜中の窒素濃度を高める。

【解決手段】電界効果トランジスタのゲート絶縁膜は、半導体基板に近い第1領域と、第1領域よりもゲート電極に近い第2領域とで窒素濃度のピークが異なっており、第1領域における窒素濃度のピークは、2.5atomic%〜10atomic%であり、第2領域における窒素濃度のピークは、第1領域における窒素濃度のピークよりも高い。

(もっと読む)

スプリット仕事関数ゲートを含むMOSFETを有する集積回路

【課題】ゲート誘起ドレインリーク電流が少ない電界効果トランジスタ、および、ゲート電極とソース/ドレイン領域との間に薄い絶縁体構造物を含む集積回路を提供する。

【解決手段】トランジスタ542のゲート電極は、ゲート電極とチャネル領域512との間の第1のフラットバンド電圧を決定する主部532と第1の側部535とを含む。この第1の側部は、上記主部に接触すると共に、上記ゲート電極と第1のソース/ドレイン領域514,516との間の第2のフラットバンド電圧を決定する。上記第1のフラットバンド電圧および上記第2のフラットバンド電圧は、少なくとも0.1eVだけ異なる。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、金属元素を有する絶縁膜の界面特性を向上させる半導体装置の製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、下層、Ge層、Ge酸化物層、上層の順に積層された構造を形成する工程と、熱処理を用いてGe酸化物層及びGe層を除去して、上層と下層とを直接接合させる工程とを有し、上層及び下層の何れかは金属元素を有する絶縁物で形成されることを特徴とする。

(もっと読む)

PチャネルMOSトランジスタ、NチャネルMOSトランジスタ及び不揮発性半導体記憶装置

【課題】高誘電率膜をゲート絶縁膜に用い、消費電力を低減したPMOSトランジスタを提供する。

【解決手段】半導体基板1と、半導体基板1の表面部にチャネル領域2を挟むように形成されたP型不純物拡散層3と、チャネル領域2上に形成されハフニウム又はジルコニウムと希土類元素又は第2族元素とを含む絶縁膜4a、4b、及び絶縁膜4a、4b上に形成されたシリコン酸化膜4cを有するゲート絶縁膜4と、ゲート絶縁膜4上に形成されたゲート電極5と、を備えるPMOSトランジスタ。

(もっと読む)

半導体装置

【課題】 ゲート電極上のシリサイド膜の断線を抑制する。

【解決手段】 ソース・ドレイン領域をデュアルシリサイド構造とし、ゲート電極の仕事関数はn型MISトランジスタ、p型MISトランジスタそれぞれの有するメタルゲート電極により定める構造とし、且つ、メタルゲート電極上の多結晶シリコン層は共通のn+ドーピング層とし、ゲート上シリサイド膜はn型領域に対しショットキー障壁が低くなる材料で形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】Pチャネル型トランジスタの閾値電圧を制御することができる半導体装置、およびその半導体装置の製造方法を提供する。

【解決手段】NTrとPTrとを含む半導体装置において、N型チャネル形成領域とP型チャネル形成領域とを有するN型半導体基板2上に絶縁膜Fが形成され、絶縁膜Fにゲート電極用溝A及びBとが形成され、ゲート電極用溝A及びBの内側表面上にゲート絶縁膜20が形成され、NTr領域におけるゲート絶縁膜20上にNTr仕事関数制御メタル膜21が形成され、NTr仕事関数制御メタル膜21及びゲート絶縁膜20上にフッ素がドープされたPTr仕事関数制御メタル膜23が形成され、PTr仕事関数制御メタル膜23の上層に、ゲート電極用溝に埋め込まれてゲート電極が形成されている構成とする。

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧が低く、トランジスタ間でしきい値電圧のばらつきの無いトランジスタを含む半導体装置を提供する。

【解決手段】nチャネルトランジスタとpチャネルトランジスタとを含む相補型の半導体装置において、nチャネルトランジスタは、ゲート絶縁膜と、ゲート絶縁膜上に形成された、第1金属(M1)とシリコン(Si)からなる第1化合物層を含む第1メタルゲート電極を備え、pチャネルトランジスタは、ゲート絶縁膜と、ゲート絶縁膜上に形成された、第1金属(M1)と第2金属(M2)とシリコン(Si)からなる第2化合物層を含む第2メタルゲート電極を備え、第1化合物層の組成が、組成式:M1Six(1≦x)で表され、第2化合物層の組成が、組成式:M1M2Siy(0<y≦0.5)で表される。

(もっと読む)

半導体装置およびその製造方法

【課題】Finの高さを必要以上に高くすることなく、実質的なチャネル幅を増大し得るFin−FETの構造及びその製造方法を提供する。

【解決手段】半導体基板11をFin状に加工して形成されたチャネル形成用半導体層11aの上面、左右両側面及び底面にゲート電極22が形成され、ゲート電極22により4面を囲まれるチャネル領域を有することを特徴とする。

(もっと読む)

半導体装置

【課題】それぞれが適した閾値を有するフィン型MOSFETとプレーナ型MOSFETが混載され、且つ少ない工程で製造することができる半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、第1のゲート電極と、前記第1のゲート電極にフェルミレベルピニングを発生させない第1のゲート絶縁膜と、を有するプレーナ型MOSFETと、第2のゲート電極と、前記第2のゲート電極にフェルミレベルピニングを発生させる第2のゲート絶縁膜と、を有するフィン型MOSFETと、を有する。

(もっと読む)

半導体素子及びそのゲート形成方法

【課題】高誘電定数を有する物質からなるゲート絶縁膜を有する半導体素子及びそのゲート形成方法を提供する。

【解決手段】素子分離膜202によりアクティブ領域が画定されている半導体基板200を提供する段階と、前記アクティブ領域上にゲート絶縁膜204を形成する段階と、前記ゲート絶縁膜204上にキャッピング膜206を形成する段階と、前記キャッピング膜206及び前記ゲート絶縁膜204を有する半導体基板200に対してアニール工程を施す段階と、前記アクティブ領域の一部にフルシリサイドゲート208を形成する段階とを含む。

(もっと読む)

半導体装置とその製造方法

【課題】微細MOSFETのゲート絶縁膜に高誘電率膜を用いた場合でも、使い易いゲート閾値電圧をもった半導体装置(特に、PチャネルMOSFET)とその製造方法を実現する。

【解決手段】ゲート電極/アルミニウムを含みシリコン酸化膜より大きな比誘電率をもった高誘電率絶縁膜/シリコン酸化膜/シリコン基板とし、熱処理によってシリコン酸化膜、あるいはシリコン酸化膜とシリコン基板との界面にアルミニウム原子あるいはアルミニウムイオンを拡散させた拡散層を設ける。高誘電率絶縁膜としては、比率が2:8から8:2の酸化ハフニウムと酸化アルミニウムの積層膜あるいは混合膜とし、熱処理は、500から1000℃で、1から100秒程度の熱処理とする。

(もっと読む)

半導体装置およびその製造方法

【課題】対称フラットバンド電圧、同一ゲート電極材料かつ高誘電率誘電体層を有するCMISFETを提供する。

【解決手段】nMISFETは、半導体基板10の表面上に配置された第1ゲート絶縁膜16と、第1ゲート絶縁膜16上に配置されたM1xM2yO(M1=Y,La,Ce,Pr,Nd,Sm,Gd,Tb,Dy,Ho,Er,Tm,YbまたはLu,M2=Hf,Zr,Ta,x/(x+y)>0.12)で表される組成比を有する第1金属酸化物層20と、第2金属酸化物層24と、第2金属酸化物層24上に配置された第1導電層28とを備え、pMISFETは、半導体基板10表面上に配置された第2ゲート絶縁膜18と、第2ゲート絶縁膜18上に配置されたM3zM4wO(M3=Al,M4=Hf,Zr,Ta,z/(z+w)>0.14)で表される組成比を有する第3金属酸化物層22と、第4金属酸化物層26と、第4金属酸化物層26上に配置された第2導電層30とを備える半導体装置およびその製法。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】不純物を混ぜなくても立方晶(cubic)、正方晶(tetragonal)又は斜方晶(orthorhombic)のハフニウム酸化物を形成することができる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】シリコン基板1上にHfO2膜3を形成する工程と、HfO2膜3上にゲート電極膜5を形成する工程と、HfO2膜3及びゲート電極膜5が形成されたシリコン基板1に熱処理を施して、HfO2膜3を結晶化する工程と、を含む。熱処理温度は例えば800℃である。

(もっと読む)

141 - 160 / 305

[ Back to top ]