Fターム[5F140BF20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 金属 (2,560) | 金属化合物(窒化物、酸化物) (305)

Fターム[5F140BF20]に分類される特許

161 - 180 / 305

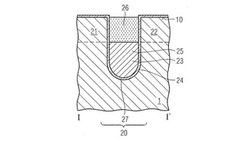

トランジスタ、集積回路および集積回路形成方法

【課題】トランジスタ、集積回路、および、集積回路形成方法を提供する。

【解決手段】半導体基板1内に形成されたゲート溝27内にゲート誘電体24を介してゲート電極23が配置された構成を有する。該ゲート電極23は、導電性炭素材を有している。

(もっと読む)

電界効果型トランジスタの修復方法、半導体装置の修復方法、半導体装置の作製方法、及び半導体装置

【課題】電界効果型トランジスタのリーク電流を低減し、寿命の向上を図るための簡便な修復方法を提供することを課題とする。また、作製コストの増加を抑え、消費電力が小さく、且つ信頼性の高い半導体装置を提供することを課題とする。

【解決手段】ソース電極又はドレイン電極の一方と、ゲート電極との間に、電気的な衝撃を加える。または、ソース電極又はドレイン電極の一方と、ソース電極又はドレイン電極の他方との間に、電気的な衝撃を加える。これにより、リークパスを絶縁化し、リーク電流を低減することができる。なお、上記の電気的な衝撃は、静電気等の電気パルスであっても良いし、直流電圧、交流電圧、直流電流、交流電流等であっても良い。

(もっと読む)

半導体装置

【課題】ポリシリコン/メタル積層電極構造のポリシリコン/メタル界面における界面抵抗を低減し、動作速度の低下を防止する。

【解決手段】半導体基板100と、領域N1にチャネル領域102を挟むように形成された拡散層103と、ゲート絶縁膜104と、金属膜105a、105b及びn型ポリシリコン膜105cを含むゲート電極105と、を有するnチャネルMISFETと、領域P1にチャネル領域202を挟むように形成されボロンをドーパントして含む拡散層203と、ゲート絶縁膜204と、金属膜205a〜c及び窒素を含む金属膜205cとの界面部におけるボロン濃度が5E19cm−3以下であるn型ポリシリコン膜205dを含むゲート電極205と、を有するpチャネルMISFETと、を備える。

(もっと読む)

半導体集積回路装置

【課題】厚さが異なる2種類以上のゲート絶縁膜を有する半導体集積回路装置の信頼性を向上させることのできる技術を提供する。

【解決手段】半導体基板1の表面に形成された酸化シリコン膜6の上層に酸化シリコン膜7を形成し、次いで厚いゲート絶縁膜を形成する領域Aを覆ったフォトレジストパターン8をマスクとして、薄いゲート絶縁膜を形成する領域Bの酸化シリコン膜6,7を除去した後、フォトレジストパターン8および酸化シリコン膜7を除去し、続いて熱酸化処理を半導体基板1に施すことによって、厚さの異なるゲート絶縁膜を形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】厚さが異なる2種類以上のゲート絶縁膜を有する半導体集積回路装置の信頼性を向上させることのできる技術を提供する。

【解決手段】半導体基板1の表面に形成された酸化シリコン膜6の上層に酸化シリコン膜7を形成し、次いで厚いゲート絶縁膜を形成する領域Aを覆ったフォトレジストパターン8をマスクとして、薄いゲート絶縁膜を形成する領域Bの酸化シリコン膜6,7を除去した後、フォトレジストパターン8および酸化シリコン膜7を除去し、続いて熱酸化処理を半導体基板1に施すことによって、厚さの異なるゲート絶縁膜を形成する。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明はフィントランジスタを含む半導体素子及びその製造方法に関する。

【解決手段】半導体素子は、素子分離構造を備えた半導体基板に画成されたフィン型活性領域と、フィン型活性領域の上部に形成されたリセスと、フィン型活性領域の上部に形成され、前記リセスを埋め込むシリコンゲルマニウム層を含むゲート電極とを含む。

(もっと読む)

絶縁層の形成方法及び半導体装置の製造方法

【課題】例えばゲート絶縁層として用いる場合に特性の良好な絶縁層を形成することができる絶縁層の形成方法を提供する。

【解決手段】被処理基板Wの表面に絶縁層を形成する方法において、前記被処理基板の表面に露出するシリコンを窒化処理して前記シリコン基板の表面にシリコン窒化膜を形成する第1の窒化工程と、前記シリコン窒化膜が形成された被処理基板をN2 O雰囲気中で、且つ圧力を50〜70Torr(6665〜9331Pa)の範囲内に維持した状態で熱処理してシリコン酸窒化膜4を形成する第1のアニール工程と、を有する。これにより、例えばゲート絶縁層として特性の良好な絶縁層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】従来のCMISデバイスにおいては、価電子帯端近くの高い仕事関数を有する金属は、還元雰囲気アニール後に実効仕事関数が低下する。

【解決手段】半導体装置は、ソースとドレイン間のN型半導体層上に形成された金属元素を含むゲート絶縁膜と、ゲート絶縁膜上に形成され、膜厚が3nm以下であるカーボン層と、カーボン層上に形成されたゲート電極とを有し、ゲート電極/ゲート絶縁膜界面へのカーボン層による仕事関数の上昇効果により、還元雰囲気アニール耐性のない価電子帯端近くの高い仕事関数を有する金属を用いずとも、PMISFETに必要な実効仕事関数を得ることができ、低い閾値電圧を実現する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜に用いられるLa−Hf−O膜系は、成膜時にシリコン基板との間に低誘電率層が出現し、これ排除する公知な技術による半導体装置及びその製造方法は提案されていなかった。

【解決手段】本発明に従う実施形態は、非晶質状態でSiが添加されたLa−Hf−O膜をゲート絶縁膜として用いる半導体装置及びその製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化が進みゲート長のバリエーションが増大した場合にも、高駆動力MISFETを搭載した高性能デバイスを安定して実現できる簡便なFUSI化技術を提供する。

【解決手段】第1のゲート長(相対的に短いゲート長)を持つ第1のゲート電極105Aがフルシリサイド化されているのに対して、第2のゲート長(相対的に長いゲート長)を持つ第2のゲート電極105Bはフルシリサイド化されていない。

(もっと読む)

CMOS半導体素子及びその製造方法

【課題】デュアルメタルゲートCMOS半導体素子を提供する。

【解決手段】金属窒化物層及び多結晶シリコンキャッピング層を備え、nMOS領域及びpMOS領域の金属窒化物層は同種物質で形成され、相異なる不純物含有量により相異なる仕事関数を持つデュアルメタルゲートCMOS半導体素子。同種の金属窒化物層によりメタルゲートを形成するので、工程が単純化して収率が向上すると共に、高性能のCMOS半導体素子を得ることができる。

(もっと読む)

半導体装置とその製造方法

【課題】MOSトランジスタのチャネル領域に高ストレス窒化膜を用いた場合に比してさらに大きな歪を与えることができる半導体装置を得ること。

【解決手段】シリコン基板10上の所定の位置に形成されるゲート絶縁膜12、ゲート電極13、ゲート絶縁膜12とゲート電極13の積層体の線幅方向両側側面に形成されるオフセットスペーサ膜15、およびオフセットスペーサ膜15の外側に形成されるサイドウォール膜16を有するゲート構造11と、ゲート構造11の線幅方向両側のシリコン基板10表面付近に形成される拡散層17と、を有する電界効果型トランジスタと、サイドウォール膜16と拡散層17上に形成される金属からなるバリア層20と、バリア層20上に形成される金属からなる応力印加層21と、を備え、バリア層20と応力印加層21は、オフセットスペーサ膜15とサイドウォール膜16によってゲート電極13と絶縁されている。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート電極の上方にコンタクトプラグを形成するときに、ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13及びチャネル形成領域12、ゲート電極23、並びに、ゲート絶縁膜30を備えており、ゲート絶縁膜30は、ゲート電極23とチャネル形成領域12との間に形成されたゲート絶縁膜本体部30A、及び、ゲート絶縁膜本体部30Aからゲート電極23の側面部23Aの途中まで延在するゲート絶縁膜延在部30Bから構成されており、チャネル形成領域12の表面を基準としたゲート電極23の高さをHGate、ゲート絶縁膜延在部30Aの高さをHInsとしたとき、HIns<HGateを満足する。

(もっと読む)

電界効果型半導体装置及びその製造方法

【課題】 電界効果型半導体装置及びその製造方法に関し、ゲート絶縁膜にダメージを与えることなく、少なくとも窒素を含有するとともにシリコンを主成分とする膜を組成制御性良く構成する。

【解決手段】 シリコンと、シリコンに対して5〜30原子数%の窒素を含有する導電膜をゲート電極3の少なくとも一部として用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されても良好な品質を有するゲート絶縁膜を備え、信頼性が高く、高速に動作可能な半導体装置およびその製造方法を提供する。

【構成】半導体装置は、半導体基板1001内に形成されたp型活性領域1003およびn型活性領域1004と、p型活性領域1003の上面に形成されたゲート絶縁膜1006と、上部におけるLaの濃度がその他の部分のLaの濃度よりも大きい第1の電極形成膜1015を含む第1のゲート電極とを有するp型MISFETとを備えている。さらに、n型活性領域1004の上面に形成されたゲート絶縁膜1006と、上部におけるAlの濃度がその他の部分のAlの濃度よりも大きい第2の電極形成膜1014を含む第2のゲート電極とを有するn型MISFETとを備えている。

(もっと読む)

絶縁ゲート電界効果トランジスタの製造方法。

【課題】ゲート電極の上方に層間絶縁層を形成するときに、ゲート電極に対向する基体の部分が酸化されることが無い、絶縁ゲート電界効果トランジスタの製造方法を提供する。

【解決手段】絶縁ゲート電界効果トランジスタの製造方法は、(a)ソース/ドレイン領域13、チャネル形成領域12、チャネル形成領域12上に形成されたゲート絶縁膜30、ソース/ドレイン領域13を覆う絶縁層21、及び、チャネル形成領域12の上方の絶縁層21の部分に設けられたゲート電極形成用開口部22を備えた基体を準備し、(b)ゲート電極形成用開口部22内を導電材料層31,32で埋め込むことでゲート電極23を形成し、次いで、(c)絶縁層21を除去し、その後、(d)全面に、第1の層間絶縁層41、第2の層間絶縁層42を、順次、成膜する工程を備え、前記工程(d)において、酸素原子を含まない成膜雰囲気中で第1の層間絶縁層41を成膜する。

(もっと読む)

絶縁膜積層体、絶縁膜積層体の製造方法、半導体装置及び半導体装置の製造方法

【課題】ボロン漏れの抑制とリーク電流増加の抑制とを同時に実現可能な、絶縁膜及びこの絶縁膜を備えた半導体装置と、絶縁膜の製造方法及び半導体装置の製造方法を提供する。

【解決手段】微結晶組織からなるハフニウム含有窒化シリコン酸化物層3aと、非晶質組織からなるハフニウム含有窒化シリコン酸化物層3bとが半導体基板2上に積層されてなる積層膜からなり、積層膜の窒素濃度が15原子%以上40原子%以下の範囲であることを特徴とする半導体装置用の絶縁膜積層体3を採用する。

(もっと読む)

半導体装置

【課題】高耐圧で、安全動作領域が広く、かつ、熱散逸性がよく、有効コンダクタンスおよび周波数特性が良好なSOIデバイスを提供すること。

【解決手段】半導体装置100において、p-基板101の表面層の一部にはBOX領域102が設けられる。BOX領域102は、ゲート構造部130の中心から下ろした垂線Lc付近まで設けられており、ドレイン領域112および拡張ドレイン領域108をp-基板101から分離する。ドレイン領域112の厚さは150nm〜300nmのいずれかであり、BOX領域102の厚さは150nm以上である。

(もっと読む)

半導体デバイスにおけるDyScO材料の選択的除去

【課題】ゲートの下にアンダーカットを形成することなく、下部の基板若しくは層の上で、希土類金属酸化物を含む高k材料を選択的に取り除く方法を提供する。

【解決手段】Si若しくはSiO2上で、例えば希土類スカンジウム酸化物高k材料(具体的にはDyScO3)を選択的に除去する方法を開示する。希土類元素ベースの高k材料層2の上面において、TiN及びTaNを含有する金属ゲートをパターニングするため、塩素含有ガスを使用することができる。塩化チタニウム及び塩化タンタルが揮発性であり、ウェハ上に存在する他の材料に対して適度な選択性を得ることができるからである。Dy及びScの塩化物は揮発性を有さないが、それらは水溶性を有するので、Dy及びSc含有高k材料の表面層は、Cl若しくはBr含有プラズマをさらす間に塩化物化(臭化物化)され、エッチング後ウォータリンスにより取り除くことができる。

(もっと読む)

ディープサブミクロントランジスタ技術用のhigh−k/金属ゲートスタックをパッシベートするためのFベースのゲートエッチングの使用

【課題】プレーナ装置またはマルチゲート装置(MuGFET)のHfベースの誘電体ゲートスタックに、フッ素を導入し、負バイアス温度安定性および正バイアス温度安定性(NBTIおよびPBTI)を大幅に改良する、新規で、効果的で、費用対効果の高い方法を提供する。

【解決手段】新規な方法は、フッ素を導入するためにSF6ベースの金属エッチング化学反応を用い、これにより標準プロセスフローの熱量の後に、界面の優秀なHパッシベーションが得られる。この方法の優位点は、この方法がFを導入するための金属ゲートエッチングを用いて、追加の注入や処理が不要であることである。新たな方法を用いた大幅なBTIの改良に加えて、MuGFET装置において、より良いVthの制御性と増加した駆動電流を得ることができる。

(もっと読む)

161 - 180 / 305

[ Back to top ]