Fターム[5F140BF42]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 形状、配置 (2,388) | 断面形状 (1,038)

Fターム[5F140BF42]の下位に属するFターム

溝掘りゲート (564)

Fターム[5F140BF42]に分類される特許

161 - 180 / 474

半導体装置の製造方法及び半導体装置

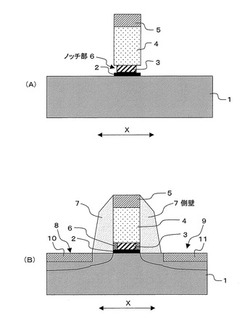

【課題】ゲートラストプロセスの適用に際して、トランジスタのフリンジ容量及びゲート抵抗の低減と、実効的なゲート長の短縮を実現する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板1上にゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4を順に積層して形成する工程と、それらをパターン加工するとともに、第1のダミーゲート部3をゲート長方向Xで第2のダミーゲート部4よりも後退させることにより、ノッチ部6を形成する工程と、ゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4の側方に絶縁材料からなる側壁7を形成し、かつ当該絶縁材料でノッチ部6を埋め込む工程と、第1,第2のダミーゲート部3,4を除去して、当該除去部分の底部にゲート絶縁膜2及びノッチ部6を残す工程と、除去部分を導電材料で埋め込むことによりゲート電極を形成する工程とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作不良を防止し、半導体装置の製造工程を簡略化する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1と、半導体基板1内に設けられる一対の不純物拡散層2A,2Bと、不純物拡散層2A,2B間の半導体基板上に設けられるゲート絶縁膜3と、ゲート絶縁膜3上に設けられるゲート電極4と、一対の不純物拡散層2A,2B上にそれぞれ設けられる2つのコンタクト5A,5Bとを具備し、ゲート電極4とコンタクト5A,5Bは、同じ材料から構成され、ゲート電極4上端およびコンタクト5A,5B上端は、半導体基板1表面からの高さが一致する。

(もっと読む)

半導体装置及びその製造方法

【課題】高速動作が可能なMIPS構造を持つメタルゲートを含む半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜3と、該ゲート絶縁膜3の上に順次形成され、TiN膜4とポリシリコン膜5とにより構成されたゲート電極20の第2のゲート電極部20bと、半導体基板1の上にゲート電極20を覆うように形成された層間絶縁膜8とを有している。層間絶縁膜8及びポリシリコン膜5を貫通して形成されたコンタクト9は、TiN膜4と直接に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】耐湿性(信頼性)及び高周波特性を両立することができる半導体装置及びその製造方法を提供する。

【解決手段】半絶縁性のSiC基板1上に化合物半導体領域2が形成されている。化合物半導体領域2上に、ゲート電極6、ソース電極4及びドレイン電極5が形成されている。シリコン窒化膜10上に、ソース電極4及びドレイン電極5から離れた位置においてゲート電極6を覆う低誘電率膜11が形成されている。低誘電率膜11の上面及び側面を覆うシリコン窒化膜12がシリコン窒化膜10上に形成されている。シリコン窒化膜12上に低誘電率膜13が形成されている。低誘電率膜13の比誘電率は低誘電率膜11のそれよりも高い。また、低誘電率膜13の耐湿性は低誘電率膜11のそれより高い。

(もっと読む)

半導体装置及びその製造方法

【課題】短チャネル効果を抑制すると共に、MISトランジスタの駆動能力が劣化することを防止するMIS(Metal Inserted Semiconductor)トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10における活性領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第1の導電膜14、及び該第1の導電膜14上に形成された第2の導電膜15からなるゲート電極15Aと、活性領域10xにおける第2導電膜15の側方下に形成されたエクステンション領域16と、第1の導電膜14上に、第2の導電膜15の側面と接して形成された第1のサイドウォール17とを備え、第1の導電膜14のゲート長方向の長さは、第2の導電膜15のゲート長方向の長さよりも大きい。

(もっと読む)

半導体装置

【課題】ゲート金属起因の閾値変調効果が制御されたCMISFETを提供する。

【解決手段】半導体基板上に設けられたCMISFETにおいて、pMISFETのゲート電極は、第1のゲート絶縁膜上に形成された第1の金属層と、その上に形成されたIIA族及びIIIA族に属する少なくとも1つの金属元素を含む第1の上部金属層とを具備し、nMISFETのゲート電極は、第2のゲート絶縁膜上に形成された第2の金属層と、第2の金属層上に形成され、前記第1の上部金属層と実質的に同一組成の第2の上部金属層とを具備し、第1の金属層が第2の金属層よりも厚く、第1及び第2のゲート絶縁膜は前記金属元素を含み、第1のゲート絶縁膜に含まれる前記金属元素の原子密度が、第2のゲート絶縁膜に含まれる前記金属元素の原子密度よりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13、チャネル形成領域12、ゲート電極423、ゲート絶縁膜430を備え、ゲート絶縁膜430はゲート絶縁膜本体部430A及びゲート絶縁膜延在部430Bから構成されており、ゲート電極を構成する第1層431はゲート電極の側面部の途中まで薄膜状に形成されており、第2層の外側層432Aは第1層431の上に薄膜状に形成されており、第2層の内側層432Bは第2層の外側層で囲まれた部分を埋め込んでおり、第3層の外側層433Aは第2層の内側層、外側層、ゲート絶縁膜延在部を覆い、ゲート電極の頂面まで薄膜状に形成されており、第3層の内側層433Bはゲート電極の残部を占めている。

(もっと読む)

半導体装置

半導体装置は、基板(11)上に形成されたフィン型半導体領域(13)と、前記フィン型半導体領域(13)の所定部分の上面及び両側面を覆うように形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜(14)上に形成されたゲート電極(15)と、前記フィン型半導体領域(13)における前記ゲート電極(15)の両側に形成された不純物領域(17)とを備えている。前記フィン型半導体領域(13)の上面上における前記ゲート電極(15)の両側に隣接して不純物阻止部(15a)が設けられている。 (もっと読む)

半導体装置

【課題】メモリセルに対して設けられる選択ゲートについて、この選択ゲートのゲート長を長くすることなく、選択ゲートの制御性を向上させる。

【解決手段】本発明の一態様において、メモリセルA1に対して設けられる選択ゲートS1を含む半導体装置は、選択ゲートS1のチャネル上に形成されているゲート絶縁膜9の上面が、選択ゲートS1の素子分離領域10の上面の一部又は全部よりも高く、Tri-gate構造を持つ。

(もっと読む)

半導体装置

【課題】オン抵抗と耐圧のトレードオフを改善し、さらにESD耐量の高い半導体装置を提供することにある。

【解決手段】ソースドレイン方向に複数のトレンチをストライプ状に形成し、そのトレンチの側面およびトレンチに挟まれた領域の上辺部にチャネル領域を形成する半導体装置とする。

(もっと読む)

半導体装置

【課題】オン抵抗と耐圧のトレードオフを改善した半導体装置を提供することにある。

【解決手段】ソースドレイン方向に複数のトレンチをストライプ状に形成し、そのトレンチの側面および底面ならびにトレンチに挟まれた領域の上面にチャネル領域を形成する半導体装置とする。

(もっと読む)

半導体装置及びその製造方法

【課題】フィールド酸化膜のエッジ付近で電界が集中するのを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】本発明に係る半導体装置は、半導体基板と;前記半導体基板に第1の導電型のイオンを注入して形成される第1の不純物拡散層と;前記第1の不純物拡散層上に形成されたゲート絶縁膜と;前記ゲート絶縁膜に隣接して形成され、前記ゲート絶縁膜の厚さより大きい厚さを有する第1のフィールド絶縁膜と;前記第1のフィールド絶縁膜に隣接して形成され、当該第1のフィールド絶縁膜の厚さより大きい厚さを有する第2のフィールド絶縁膜と;前記ゲート絶縁膜、第1のフィールド絶縁膜及び前記第2のフィールド絶縁膜上に亘って形成されたゲート電極と;前記ゲート電極に覆われる前記第1の不純物拡散層に隣接して前記半導体基板に形成され、前記第1の導電型を有する第2の不純物拡散層とを備えている。

(もっと読む)

横方向半導体デバイスおよびその製造方法

【課題】低いゲート・ドレイン間容量(CGD)を提供し、その上で、標準CMOSフローと互換性を持つ製造工程を提供する。

【解決手段】直交ゲート拡張ドレインMOSFET(EDMOS)構造は、低いゲート・ドレイン間の容量(CGD)を提供し、さらに高い信頼性を示す。シャロートレンチアイソレーション(STI)酸化膜領域に折り畳まれたゲート電極を有する。水平および垂直ゲート電極部は、ゲート制御を提供する。同じ基板上に高圧デバイスおよび標準CMOSの部品を収容する。表面電界緩和型(RESURF)技術は、高い降伏電圧と特定のオン抵抗との間のトレードオフを最適化するために使用される。デバイス製造工程は、標準CMOSフローと互換性を持ち、基本的なCMOS技術からプロセスモジュールを加えるかあるいは除くことができる。

(もっと読む)

トランジスタ、半導体装置及びその製造方法

【課題】トレンチゲート型トランジスタのオン抵抗とプレーナ型トランジスタの耐圧とを同時に最適化する。

【解決手段】半導体基板10上に、半導体層16A、16Bがエピタキシャル成長により形成される。第1の領域において第1の埋め込み層12が形成され、第2の領域において第2の埋め込み層13が形成される。第1の埋め込み層12はN+型の第1の不純物層12Aと、それより広い範囲に拡散されたN型の第2の不純物層12Bとによって形成される。第2の埋め込み層13はN+型の不純物層のみで形成される。第1の領域において半導体層16Aの表面からN型の第3の不純物層18が深く拡散される。第1の領域にはトレンチゲート型トランジスタが形成され、第2の領域にはプレーナ型トランジスタが形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル移動度の低下を防止して、パンチスルーストッパを形成する。

【解決手段】半導体基板100と、前記半導体基板上に形成され、長手方向と短手方向とを有し、順に積層されたボロンを含むシリコン炭化膜とシリコン膜とを有する半導体層110と、少なくとも前記半導体層の前記短手方向の側面に形成されたゲート電極150と、前記半導体層に形成され、前記ゲート電極の前記長手方向に隣接して形成されたソース・ドレイン領域111、112と、前記半導体層の側面であって、前記ゲート電極と前記半導体基板との間に形成された素子分離絶縁膜130と、を備える。

(もっと読む)

半導体素子製造方法および半導体素子

【課題】チャネルが上・下方向に形成されるピラーパターンの転倒現象を防止する半導体素子製造方法を提供する。

【解決手段】導電膜33Bをパターニングして複数の開放領域を形成するステップと、各々の開放領域の側壁にゲート絶縁膜41を形成するステップと、各々の開放領域内にピラーパターン42を形成するステップと、ピラーパターン42間の導電膜33Bをエッチングし、ピラーパターン各々を覆うゲート電極33Bを形成するステップを含む。ピラーパターン42を基板31のエッチングでない成長によって形成し、成長はあらかじめ形成された開放領域を埋め込む形態を取るためピラーパターン42の転倒現象を防止することができ、ひいては半導体素子の信頼性および安全性を向上させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細で精度が高く、歩留まりが向上した半導体装置を提供する。

【解決手段】半導体装置は、第1トランジスタ2と第2トランジスタ5とを具備する。第1トランジスタ2は、半導体基板100上に第1ゲート絶縁膜51を介して形成された第1ゲート電極21と第1ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第2トランジスタ5は、半導体基板100上に第2ゲート絶縁膜51を介して形成された第2ゲート電極22と第2ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第1ゲート電極21及び第2ゲート電極22は、第1共通ソース・ドレイン領域30のコンタクトである第1ノード電極41の両側壁に設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート酸化膜の信頼性を阻害せずに、ゲート電極の低抵抗化を実現可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、炭化珪素からなり、表面にエピタキシャル結晶成長層2が形成された半導体基板1と、エピタキシャル結晶成長層2上部に選択的に形成されたウェル領域3とを備える。そして、ウェル領域3上部に選択的に形成されたソース領域4と、ソース領域4とエピタキシャル結晶成長層2とに挟まれたウェル領域3の表面を覆うゲート絶縁膜6上に形成されたゲート電極7とを備える。ゲート電極7は、珪素層7aと、炭化珪素層7bとの積層構造からなり、ゲート電極7上部に形成されたシリサイド層7cをさらに備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧特性と電流増幅特性とに優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】電界緩和領域として機能するRESURF領域110を備えたRESURF−MOSFET100において、RESURF領域110と、ソース用コンタクトとして機能するn+型コンタクト領域104sと、ドレイン用コンタクトとして機能するn+型コンタクト領域104dとのうち少なくとも1つに、n型の導電性を有する原子と窒素原子とを不純物として含ませる。

(もっと読む)

161 - 180 / 474

[ Back to top ]