Fターム[5F140BF42]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 形状、配置 (2,388) | 断面形状 (1,038)

Fターム[5F140BF42]の下位に属するFターム

溝掘りゲート (564)

Fターム[5F140BF42]に分類される特許

141 - 160 / 474

半導体装置の製造方法および半導体装置

【課題】金属層にノッチ形状が形成されず、多結晶シリコン層から金属層へのシリコンの拡散を防止したMIPSゲート構造を有する半導体装置を提供する。

【解決手段】MIPSゲート構造を有する半導体装置の製造方法において、MIPSゲートの作製工程は、半導体基板上に、ゲート絶縁膜、メタル層、および多結晶シリコン層を順次堆積する工程と、多結晶シリコン層の上に形成したエッチングマスクを用いて、多結晶シリコン層をエッチングする工程と、メタル層を選択的にエッチングして、下方に向かって側壁がテーパ状に張り出したメタル層を残す工程と、多結晶シリコン層の側壁を含む平面から外方に突出したメッキ層のテーパ部を酸化して、酸化テーパ部とする酸化工程と、酸化テーパ部をエッチングで除去する除去工程とを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられる金属半導体化合物電極の界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板と、半導体基板上に形成され、Sを1×1020atoms/cm3以上含有する界面層と、界面層上に形成され、略全域にSを1×1020atoms/cm3以上含有する金属半導体化合物層と、金属半導体化合物層上の金属電極を有することを特徴とする半導体装置。半導体基板上に金属膜を堆積し、第1の熱処理により、金属膜を半導体基板と反応させて、金属半導体化合物層を形成し、金属半導体化合物層に、飛程が金属半導体化合物層の膜厚未満となる条件でSをイオン注入し、第2の熱処理により、Sを再配置することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】バルク基板を用いてもショートチャネル効果の抑制を効果的に発揮することができるFinFET構造を有する半導体装置及びその製造方法を得る。

【解決手段】Si基板1上にSiCエピタキシャル層2が形成され、SiCエピタキシャル層2の突出部2t上にSiエピタキシャル層3が形成される。突出部2t及びSiエピタキシャル層3は共に第1の方向に延びて、一方向延在形状を呈している。Siエピタキシャル層3の上面上及び両側面上には酸化膜8,窒化膜9及びゲート酸化膜20が形成される。酸化膜8,窒化膜9及びゲート酸化膜20を介して、Siエピタキシャル層3の上面上及び側面上にゲート電極G2が形成される。

(もっと読む)

半導体装置の製造方法

【課題】容易にコンタクト抵抗を低減することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に多結晶シリコン膜を形成し、その後、この多結晶シリコン膜の表面をエッチングする。そして、エッチングされた多結晶シリコン膜をシリサイド化して、シリサイド膜12を形成する。更に、シリサイド膜12に接するプラグ23s、23d及び23gを層間絶縁膜21内に形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート絶縁膜破壊が抑制された半導体装置を提供する。

【解決手段】ゲート電極給電用シリコンピラー5の表面を覆うゲート電極8と重なる位置に設けられたコンタクトホール13を備え、コンタクトホール13には、コンタクトホール13の底部から少なくともゲート電極8の上面よりも上方まで充填されたゲートリフトポリシリコン14と、ゲートリフトポリシリコン14上に配置されたゲートコンタクト15とが設けられていることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、短チャネル効果を抑制したままで、オフ電流を増加することなく、オン電流を増大させることが可能な半導体装置(縦型SGT)を提供する。

【解決手段】中空筒状に形成された半導体のボディ部4と、ボディ部4の下部に形成され、ソースおよびドレイン領域の一方となる第1の領域3と、ボディ部4の上部に形成され、ソースおよびドレイン領域の他方となる第2の領域5と、ボディ部4の前記ソース領域と前記ドレイン領域に挟まれた領域に形成されたチャネル領域4aと、チャネル領域4aの内周面および外周面をゲート絶縁膜を介して覆うように形成されたゲート電極7と、第1の領域に接するようにボディ部4の下方に形成され、第1の領域と同じ導電型の半導体層からなる第3の領域3aとを、備えたことを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置

【課題】動作特性の劣化を抑えつつ、それぞれ適切な閾値電圧を設定された、メタルゲート電極を用いたn型およびp型のMISFETを混載する半導体装置を提供する。

【解決手段】半導体基板上に第1のゲート絶縁膜を介して形成された、第1の金属層および前記第1の金属層上の第1の導電層を含む第1のゲート電極を含むn型トランジスタと、半導体基板上に第2のゲート絶縁膜を介して形成された、前記第1の金属層よりも厚さが厚く、前記第1の金属層と構成元素の同一な材料からなる第2の金属層、および前記第2の金属層上の第2の導電層を含む第2のゲート電極を含むp型トランジスタと、を有する。

(もっと読む)

半導体集積回路装置

【課題】 LCDドライバICには通常の低耐圧MISFETとともに、高耐圧MISFETが搭載される。通常のMISFETよりゲート酸化膜が厚いため、必然的に電極高さが高くなる。そのためゲート・コンタクトの深さが浅く、通常部とのプロセス上の両立が必要となる。

【解決手段】本願発明は高耐圧MISFETのたとえばチャネル幅方向において、厚膜ゲート酸化領域の境界をゲート電極端より内側に納めたものである。これにより低くなったゲート電極部にゲート・コンタクトを配置し、厚膜境界がゲート電極端より内側でかつ、ゲート・コンタクトとチャネル端との間にくることとなる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート長を決めるドライエッチングにおいてプラズマ発光をモニターすることによる終点検出方法を用いることにより半導体装置のゲート長を安定して製造する。

【解決手段】ソース拡散層、ドレイン拡散層及び柱状半導体層が基板上に垂直方向に階層的に配置され、柱状半導体層の側壁にゲートが配置される半導体装置の製造方法であって、柱状半導体層を埋め込むように第1の絶縁膜又は導電膜を成膜し、第1の絶縁膜又は導電膜を柱状半導体層上部に形成されたストッパーにより終点検出を行い平坦化し、第2の絶縁膜又は導電膜を成膜し、第2の絶縁膜又は導電膜のエッチングすると共にエッチング時のエッチングレートを算出し、第2の絶縁膜又は導電膜をエッチバックする際の第2の絶縁膜又は導電膜のエッチングレートを用いて第1の絶縁膜又は導電膜のエッチングの終点検出を行うことにより、第1の絶縁膜又は導電膜のエッチング量を制御する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】閾値電圧が制御されて、且つ特性のばらつきが抑制された半導体装置を提供する。

【解決手段】基板2と、STI素子分離領域3と、活性領域4と、活性領域4に形成された第1ゲートトレンチ5と、第1ゲートトレンチ5の底部に設けられた第2ゲートトレンチ6と、第1及び第2ゲートトレンチ5,6にゲート絶縁膜7を介して埋め込み形成されたゲート電極8と、第1ゲートトレンチ5の幅方向両側の活性領域4にイオンを注入することによって形成されたソース/ドレイン領域9とを備え、第2ゲートトレンチ6と第2ゲートトレンチ6の長手方向に位置するSTI素子分離領域3との間に、チャネルを構成するシリコン薄膜部10が設けられていることを特徴とする半導体装置1。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の周囲、全周にわたってチャネル領域を形成することで、単位面積当たりの電流量を増加させることを可能にする。

【解決手段】半導体領域11と、前記半導体領域11中に配置されたゲート電極21と、前記ゲート電極21の周囲に形成されたゲート絶縁膜22と、前記ゲート電極21の一端に前記ゲート絶縁膜22を介して形成されたソース・ドレイン電極になる第1不純物領域23と、前記ゲート電極21を横切るように前記半導体領域11に前記ゲート絶縁膜22を介して形成されたソース・ドレイン電極になる第2不純物領域24と、前記ゲート電極21の他端に接続されたゲート引き出し電極25を有し、前記第1不純物領域23と前記第2不純物領域24との間の前記ゲート電極21周囲の前記半導体領域11にチャネル領域が形成される。

(もっと読む)

デュアル金属ゲートのコーナー部

【課題】 デュアル金属ゲートのコーナー部を有する改良された電界効果トランジスタを提供する。

【解決手段】 上記を鑑みて、改善された電界効果トランジスタ(FET)構造体、及び該構造体を形成する方法の実施形態が開示される。このFET構造体の実施形態の各々は、固有のゲート構造体を組み込む。具体的には、このゲート構造体は、FETチャネル領域の中央部分の上方の第1のセクションと、チャネル幅のエッジの上方(すなわち、チャネル領域と隣接する分離領域との間の界面の上方)の第2のセクションとを有する。第1のセクション及び第2のセクションは、これらが異なる有効仕事関数(すなわち、それぞれ第1の有効仕事関数及び第2の有効仕事関数)を有する点で異なる(すなわち、これらは、異なるゲート誘電体層及び/又は異なるゲート導体層を有する)。チャネル幅のエッジにおける閾値電圧が上昇することを確実にするように、異なる有効仕事関数が選択される。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース・ドレインの寄生抵抗の低減及び短チャネル効果の抑制と共にリーク電流の低減をはかる。

【解決手段】チャネル領域を構成する第1の半導体領域12と、第1の半導体領域12上にゲート絶縁膜15を介して形成されたゲート電極16と、第1の半導体領域12をチャネル長方向から挟んで形成された金属シリサイドからなるソース・ドレイン電極14と、を具備してなる電界効果トランジスタであって、ソース・ドレイン電極14は、チャネル領域の平均的な不純物濃度よりも高い不純物濃度を有し、且つチャネル領域との界面又は界面近傍に前記不純物濃度のピークを持ち、チャネル領域は、ソース・ドレイン電極との界面又は界面近傍に前記不純物濃度のピークを持つ。

(もっと読む)

半導体装置

【課題】半導体装置の電流駆動能力の向上および電流駆動能力の変動の抑制が図られた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板200と、半導体基板200の主表面に形成された溝部内に埋め込まれた素子分離絶縁膜104と、半導体基板200の主表面上に形成されたゲート電極120と、ゲート電極120と隣り合う部分に形成されたソース領域111と、ゲート電極120と隔てて設けられたゲート電極150と、ゲート電極150と隣り合う部分に形成されたソース領域141と、ソース領域111,141を覆うように形成され、素子分離絶縁膜104が半導体基板200に加える応力と反対方向の応力を半導体基板に加えるストレス絶縁膜130を備え、ゲート電極120の隣りに位置する部分は、ゲート電極120下に位置する部分よりも下方に位置し、ゲート電極150の隣りに位置する部分からゲート電極150下に達する部分は、実質的に面一とされる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化しても動作特性の劣化が生じないSTI構造の半導体装置及びその製造方法を得る。

【解決手段】NMOSトランジスタのゲート電極部をNMOS仕事関数制御メタル層7及びゲート主電極5により構成する。NMOS仕事関数制御メタル層7をスパッタ法により形成され、ディボット部2dが設けられるエッジ近傍領域である領域bにおける膜厚は、他の領域である領域aにおける膜厚より薄く形成される。したがって、NMOS仕事関数制御メタル層7に関し、領域bにおける実効仕事関数が領域aにおける実効仕事関数に比べ、ミッドギャップよりに設定される。

(もっと読む)

半導体装置及びその製造方法

【課題】横型絶縁ゲートトランジスタ素子を備え、オン抵抗の増加を抑制しつつ体格を小型化することのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体層に構成されたLDMOS素子と、半導体層の主表面上に形成された絶縁膜を同一表面から貫通するコンタクプラグとしての、ソース領域とベースコンタクト領域とに接続された第1コンタクトプラグと、を備えた半導体装置であって、ベースコンタクト領域が、半導体層の主表面に略垂直な方向においてソース領域よりも主表面に対して下方で、半導体層の主表面に沿う方向においてソース領域と少なくとも一部が重なる位置に形成されている。そして、第1コンタクトプラグが、絶縁膜及びソース領域を貫通しつつベースコンタクト領域まで延設されている。

(もっと読む)

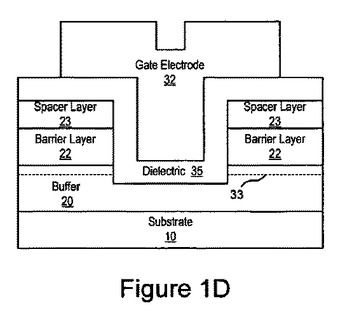

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

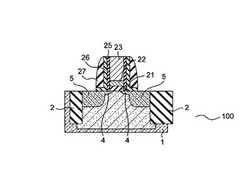

半導体装置

【課題】 一対の主電極の間に設けられたゲート電極を有する半導体装置において、高い耐圧を確保しながらオン抵抗を低くする技術を提供する。

【解決手段】 半導体装置100は、一対の主電極2,22間に設けられたゲート電極10を備えている。ゲート部10は絶縁ゲート電極部10aとショットキー電極部10bを有している。半導体装置100は、主電極2に接続するコンタクト領域18と、コンタクト領域18に隣接するチャネル半導体領域8と、チャネル半導体領域8の裏面に接しているp型半導体領域20と、チャネル半導体領域8とp型半導体領域20の両者に隣接するドリフト半導体領域12を備えている。絶縁ゲート電極部10aは、ゲート絶縁膜4を介してコンタクト領域18の表面に対向している。ショットキー電極部10bは、ドリフト半導体領域12の表面に直接的に接触している。

(もっと読む)

半導体装置およびその製造方法

【課題】 高OFF耐圧および低ON抵抗を実現し、かつ小形化が可能な半導体装置およびその製造方法を提供する。

【解決手段】 ゲート電極4Aをドレイン側N-拡散層2b上まで設けることによって、ゲート電極4Aに電圧が印加されるON状態において、ドレイン側N-拡散層2bにキャリアを誘起することができるので、前提技術に比べて、ON抵抗を低下させることができる。これによって、第1ゲート絶縁膜6A上の部分と、ドレインN+拡散層5との離隔距離であるドレインオフセット長DL2を小さくすることなく、ON抵抗を低下させることができる。したがって、ドレインオフセット長DL2を前提技術のドレインオフセット長DL1と同程度に維持することができるので、ゲート電極4Aに電圧が印加されないOFF状態では、前提技術とほぼ同じOFF耐圧を得ることができる。

(もっと読む)

141 - 160 / 474

[ Back to top ]