Fターム[5F140BG11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート側壁構造及び配置 (6,762) | ゲート側壁材料 (3,458)

Fターム[5F140BG11]の下位に属するFターム

SiO (1,611)

PSG、BSG、BPSG (16)

SiN (1,528)

多結晶Si (32)

高融点金属珪化物(高融点金属を含む) (10)

空隙 (15)

Fターム[5F140BG11]に分類される特許

141 - 160 / 246

半導体装置及びその作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

リセスのあるストレイン領域を有すマルチゲートデバイス

発明の実施形態は、多数ゲートを有すデバイスを提供する。デバイス本体金属ゲートのリセス内の応力材料は、デバイスのチャネル領域に応力を生じてよく、これによりデバイスの性能が向上する。 (もっと読む)

半導体装置およびその製造方法

【課題】ショートチャネル効果を抑制しつつ、キャリアの移動度を向上させた半導体装置およびその製造方法を提供する。

【解決手段】本実施形態に係る半導体装置は、半導体基板1と、半導体基板1上にゲート絶縁膜2を介して形成されたゲート電極3と、ゲート電極3下におけるチャネル領域を挟むように半導体基板1に埋め込まれて形成され、半導体基板1とは格子間隔の異なる材料からなる半導体層10とを有し、半導体層10は、チャネル領域側に配置された第1半導体層11と、第1半導体層11よりも不純物濃度が大きい第2半導体層12とを有する。

(もっと読む)

二重金属ゲートを含む半導体構造及びその製造方法(二重金属ゲートの自己整合集積化)

【課題】二重金属ゲートを含む半導体構造及びその製造方法を提供する。

【解決手段】少なくとも1つのn型電界効果トランジスタ(nFET)および少なくとも1つのp型電界効果トランジスタ(pFET)を含み、その両方がそれぞれnFETの性質およびpFETの性質を有する金属ゲートを含み、上部多結晶シリコンゲート電極を含まない半導体構造を提供する。本発明は、このような半導体構造を製造する方法も提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、サイドウォールスペーサの端部で接合リーク電流を増大させない半導体装置を提供することを目的とする。

【解決手段】 本発明は、シリコン基板1と、シリコン基板1の主面にゲート絶縁膜3を介して形成されたゲート電極4と、ゲート電極4の側面を覆うように形成され、最下層がシリコン酸化膜6で、シリコン酸化膜6上にシリコン窒化膜7が形成された少なくとも2層からなるサイドウォールスペーサ8と、ゲート電極4を挟むシリコン基板1の主面に形成されたソース領域及びドレイン領域と、シリコン窒化膜7の下層に延在することなく、ソース領域及びドレイン領域側のシリコン酸化膜6の端面を覆うプロテクション膜20と、ゲート電極4に対してプロテクション膜20よりも外側のソース領域及びドレイン領域に形成される金属シリサイド層11とを備える。

(もっと読む)

半導体装置の製造方法

【課題】酸化膜へのサイドエッチを防止でき、L型サイドウォールスペーサーの半導体基板の主面に沿って外方に伸びている部分の寸法を精度よく制御できるMOS型半導体装置の製造方法を提供する。

【解決手段】ゲート電極表面に絶縁膜と該絶縁膜に対して十分なエッチング選択比が得られる異種膜を形成する工程と、前記異種膜と前記絶縁膜を異方性エッチングし、前記異種膜のみを除去して、前記ゲート電極の側面にL型サイドウォールスペーサーを形成する工程と、前記ゲート電極、前記L型サイドウォールスペーサーをマスクとして、前記半導体基板の素子形成領域に不純物イオンを注入して、高濃度不純物層と低濃度不純物層を形成する工程と、前記半導体基板を熱処理して、高濃度不純物層と低濃度不純物層を活性化する工程とを含むことを特徴とするLDD構造を有する構造のMOS型半導体装置の製造方法。

(もっと読む)

成膜方法および半導体装置の製造方法

【課題】大気圧でエピタキシャル成長を行うことで、成長速度を低下させることなくヒ素を高濃度にドーピングしたシリコンエピタキシャル成長層を形成することを可能とする。

【解決手段】エピタキシャル成長によりヒ素をドーピングしたシリコン層(シリコンエピタキシャル成長層22)を形成する成膜方法であって、前記エピタキシャル成長雰囲気13を大気圧として前記エピタキシャル成長雰囲気13中にドーピング物質のヒ素を含むガスを供給することを特徴とする。

(もっと読む)

半導体素子の製造方法

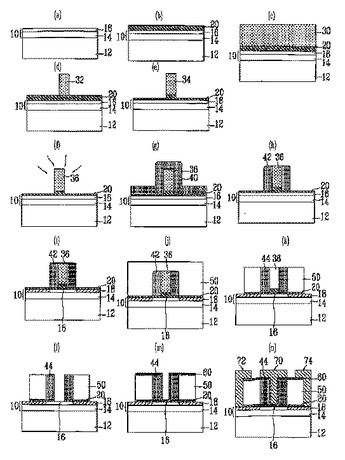

本発明は、リソグラフィ工程を経たフォトレジストの特性を変化させてダミー構造物を形成し、これをゲート電極形成工程に適用した半導体素子の製造方法に関することで、半導体基板上の最上部にバッファー層を形成するステップと、前記バッファー層の上部に無機物フォトレジストを塗布してリソグラフィを通じてフォトレジストパターンを形成するステップと、前記形成されたパターンに特定ガスを使用して熱処理を行うステップと、前記熱処理された構造物の上部に均一な厚さの絶縁膜を蒸着した後に前記パターンが露出されるように前記蒸着された膜をエッチングするステップと、前記工程を経た構造物に絶縁膜を蒸着し、前記パターンが露出されるように前記絶縁膜をエッチングするステップと、前記露出されたパターンを除去するステップと、前記パターンが除去された位置にゲート酸化膜を形成するステップと、前記形成されたゲート酸化膜の上部にゲート電極を形成するステップと、を含む。本発明によれば、ナノ素子を製作するための構造を形成する時、リソグラフィを通じて形成された膜の特性が後続熱処理を通じて改善されるので、多様な素子を製作するための構造を容易に形成することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを用いた半導体装置の製造方法において、RPTの短縮、ゲート寸法の加工精度の向上を図る半導体装置の製造方法を提供する。

【解決手段】半導体基板上にダミーゲートを形成する工程、前記ダミーゲートをマスクとして前記半導体基板に不純物を導入して、ソース・ドレイン拡散領域を形成する工程、前記ダミーゲートの周囲に絶縁膜を形成する工程、前記ダミーゲートを除去して開口部を形成する工程、及び前記開口部にゲート絶縁膜を介してゲート電極を形成する工程を具備する方法である。前記ダミーゲートは、前記半導体基板上に、炭素と水素との原子比(C/H)が1以上であり、かつ炭素の絶対量が50%以上である炭素過剰の組成のポリマーを塗布してポリマー膜を形成する工程、前記ポリマー膜上にフォトレジストパターンを形成する工程、及び前記フォトレジストパターンを前記ポリマー膜に転写する工程により形成されることを特徴とする。

(もっと読む)

半導体素子およびその製造方法

【課題】簡略化された工程の高耐圧MOSトランジスタを提供する。

【解決手段】第一導電性の基板上に形成された半導体素子を提供する。前記素子はゲートと、第二導電性のドレイン領域と、第二導電性のソース領域と、第二導電性を持つ第一の低濃度ドープ領域とを含む。前記ゲートは前記第一導電性の基板上に形成される。前記第二導電性のドレイン領域と前記第二導電性のソース領域とは、前記導電性基板中、前記ゲートの両側に形成される。前記第二導電性を持つ第一の低濃度ドープ領域は前記第一導電性の基板中、前記ゲートと前記第二導電性のソース領域との間に形成される。

(もっと読む)

方法、半導体構造(準自己整合ソース/ドレインフィンFETプロセス)

【課題】複数のフィンFETデバイスを含む半導体構造を形成する方法を提供すること。

【解決手段】具体的には本発明は、複数のフィンFETデバイスを含む半導体構造を形成する方法であって、長方形のパターンを形成して相対的に細いフィンを画定する際に、これを横切るマスクを、化学的酸化物除去(COR)プロセスとともに使用する方法を提供する。この方法はさらに、シリコンを含む選択的な材料の使用によって隣接するフィンどうしを合併させるステップを含む。本発明はさらに、本発明の方法を利用して形成された半導体構造に関する。

(もっと読む)

電荷キャリア移動度修正のための回転剪断応力

【課題】 電荷キャリア移動度修正のための回転剪断応力を提供すること。

【解決手段】 半導体構造体及びその製造方法は、分離トレンチにより取り囲まれた活性領域メサを有する半導体基板を使用する。第1応力を有する第1分離領域は分離トレンチに配置される。第1応力とは異なる第2応力を有する第2分離領域もまた分離トレンチに配置される。第1分離領域及び第2分離領域は活性領域メサに回転剪断応力をかけるような大きさにされ、そのように位置決めされる。

(もっと読む)

ゲート酸化物の漏れを抑えたリプレースメントゲートトランジスタ

ゲート酸化物層(12)とメタルゲート電極(60)との間に保護層(70)を形成することによって、リプレースメントゲートトランジスタに対してリーク電流を抑えた実効的なゲート酸化膜厚を得ることができ、これにより、応力を減らすことができる。実施形態においては、金属ゲート電極(60)から保護層を通じてゲート酸化物層(12)に向かうに従って濃度が低下する金属炭化物を含む非晶質炭素層(70)の保護層が形成される。方法の実施形態では、リムーバブルゲートを除去するステップ、ゲート酸化物層へ非晶質炭素層を蒸着するステップ、メタルゲート電極(60)を形成するステップ、を含み、さらにその後、メタルゲートからの金属を非晶質炭素層に拡散して金属炭化物を形成するように、高温に加熱するステップ、を含む。さらに、一実施形態では、高誘電定数を有するゲート酸化物層(82)と、金属ゲート電極(100)と基板(10)との界面において高濃度のシリコンと、を含むメタルゲートトランジスタが含まれる。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】金属化合物材料からなるゲート絶縁膜の高誘電率化と酸素欠損の低減とを両立させる技術を提供する。

【解決手段】シリコン基板1の表面に酸化シリコン膜を堆積した後、酸化シリコン膜上にALD法によってHf−Al−N膜を堆積する。次に、900℃〜1000℃の非酸化性雰囲気中でシリコン基板1を急速アニールすることによって、緻密で誘電率の高いHf−Al−Si−O−N膜からなるゲート絶縁膜7を形成し、続いて酸素ラジカル雰囲気中でシリコン基板1を熱酸化処理することによって、ゲート絶縁膜7中の酸素欠損を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】NMIS領域において、チャネル領域におけるキャリアの移動度を向上させる。

【解決手段】半導体装置は、半導体基板101における素子分離102によって区画されたNMIS領域103と、NMIS領域103及び素子分離102の上に、NMIS領域103を跨ぐように形成されたゲート絶縁膜111と、ゲート絶縁膜111の上に形成されたゲート電極112と、第1のゲート電極112における素子分離102の上に形成されている部分の側面に形成された側壁絶縁膜(114、115、116)と、n型エクステンション拡散層117と、n型不純物拡散層118とを備える。半導体基板101の全面上に、引っ張り応力を有するライナー膜35をさらに備えている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】シリコン窒化膜が半導体基板に近接しないようにした半導体集積回路装置と、コンタクトホールの加工を容易にする半導体集積回路装置の製造方法を提供する。

【解決手段】素子分離領域4に囲まれたシリコン基板21上に、シリコン窒化膜をエッチングストッパーとして用いた自己整合コンタクトプロセスによって形成されたコンタクトホールに埋め込まれ、拡散層2,3に電気的に接続されたコンタクトプラグ33を有する半導体集積回路装置であって、前記拡散層2、3の露出面に選択エピタキシャル成長により形成された、各ゲート絶縁膜22の前記拡散層側端部と接するシリコン層28を形成し、各ゲート電極22と前記シリコン層28との間にシリコン酸窒化膜またはシリコン酸化膜からなる絶縁膜27’が前記ゲート絶縁膜22に接して埋め込まれており、シリコン窒化膜26,29’,32が絶縁膜27’によりシリコン基板21と隔離されている。

(もっと読む)

半導体装置

【課題】 チャネル領域に十分な歪みを与えることができ、性能の向上をはかることが可能な半導体装置を提供する。

【解決手段】 空洞102を有し、空洞の上方にソース領域108、ドレイン領域108及びチャネル領域を有する半導体基板100と、チャネル領域上にゲート絶縁膜105を介して形成されたゲート電極106と、空洞の上面に形成された第1の部分を有し、チャネル領域に歪みを与える応力発生膜112とを備える。

(もっと読む)

半導体素子のトランジスタ形成方法

【課題】複数のゲートスタックの稠密度とは関係なしに、均一な厚さのスペーサ酸化膜を一層迅速に形成できる半導体素子の形成方法を提供する。

【解決手段】半導体基板100上に複数のゲートスタック110を形成する段階と;前記半導体基板100上に気体状態のトリメチルアルミニウム及びトリス(tert-アルコキシ)シラノールを交互に供給することで、前記複数のゲートスタック110上にスペーサ酸化膜118を形成する段階と;を含んで半導体素子のトランジスタ形成方法を構成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】サリサイド技術を用いてMOSトランジスタのシリサイド領域及び非シリサイド領域を形成する工程において、シリサイド層を半導体基板へのダメージなく形成する。

【解決手段】第1のサイドウォールスペーサ108を有するゲート電極103及びソース・ドレイン拡散層109,110を被覆するようにSiCwHxOyNz(w>0、x≧0、y>0、z≧0)で表される有機無機ハイブリッド膜112を堆積する工程と、有機無機ハイブリッド膜112の所定部分を酸化層115に変換する工程と、酸化層115を選択的に除去して、ゲート電極103及びソース・ドレイン109,110の所定部分を開口すると同時に第1のサイドウォールスペーサ108の側面に第2のサイドウォールスペーサ116を形成する工程と、ゲート電極103及びソース・ドレイン拡散層109,110の開口部分をシリサイド化してシリサイド層120を形成する工程を含む。

(もっと読む)

トランジスタ、並びにそれを用いた表示装置、電子機器、及び半導体装置

【課題】コンタクト抵抗の低いトランジスタを提供する。

【解決手段】P型又はN型を付与する不純物元素を含む半導体膜と、その上に形成された絶縁膜と、少なくとも前記絶縁膜に形成されたコンタクトホールを介して前記半導体膜と電気的に接続された電極又は配線とを有し、前記半導体膜は、所定の深さよりも深い領域に含まれる前記不純物元素の濃度が第1の範囲(1×1020/cm3以下)であり、且つ前記所定の深さより浅い領域に含まれる前記不純物元素の濃度が第2の範囲(1×1020/cm3を超える)であり、前記半導体膜の、前記電極又は配線と接する部分よりも深い領域は、前記不純物元素の濃度が前記第1の範囲である。

(もっと読む)

141 - 160 / 246

[ Back to top ]