Fターム[5F140BG11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート側壁構造及び配置 (6,762) | ゲート側壁材料 (3,458)

Fターム[5F140BG11]の下位に属するFターム

SiO (1,611)

PSG、BSG、BPSG (16)

SiN (1,528)

多結晶Si (32)

高融点金属珪化物(高融点金属を含む) (10)

空隙 (15)

Fターム[5F140BG11]に分類される特許

201 - 220 / 246

ステップゲートを有する半導体素子及びその製造方法

【課題】セルのしきい値電圧の低下を防止できる半導体素子及びその製造方法を提供すること。

【解決手段】第1活性領域101A及び第1活性領域101Aに比べて高い位置に形成された第2活性領域102とを有する半導体基板21を準備するステップと、第1活性領域101A及び第2活性領域102間の境界領域を面取処理するステップと、面取処理された境界領域を含む基板全面にゲート絶縁膜31を形成するステップと、境界地域上のゲート絶縁膜31上に、第1活性領域101Aの一部から第2活性領域102の一部までまたがりステップ構造を有するゲートパターン200を形成するステップと、ゲートパターン200の両側壁にゲートスペーサ34、35を形成するステップと、第1活性領域101Aに第1セル接合部36Aを、第2活性領域102に第2セル接合部36Bを形成するステップとを含む。

(もっと読む)

半導体装置

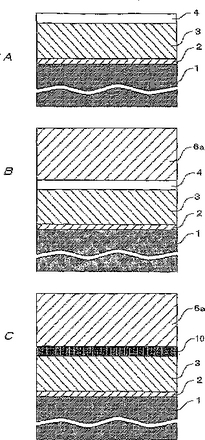

【課題】 絶縁膜層に空隙を設けずにトランジスタ間あるいは配線間の分離のための絶縁膜層の低誘電率化を行う。

【解決手段】 ゲート絶縁膜(シリコン酸化膜)5以外の素子分離領域4、層間絶縁膜10及び保護絶縁膜8、9の少なくとも一部をフッ化炭素(CFx、0.3<x<0.6)又は炭化水素(CHy、0.8<y<1.2)で形成する。

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置

【課題】 NチャネルMISFETのゲート電極およびPチャネルMISFETのゲート

電極が共に適切な仕事関数を持ち、しきい値電圧の制御が容易な絶縁ゲート型電界効果ト

ランジスタを含む半導体装置を実現する。

【解決手段】 本発明の絶縁ゲート型電界効果トランジスタを含む半導体装置は、第1の

素子領域に形成されると共に、ゲート電極膜におけるゲート絶縁膜に接する領域が、タン

グステンシリサイドで構成されたNチャネルMISFETと、第2の素子領域に形成され

ると共に、ゲート電極膜が、白金シリサイド及びタングステンシリサイドと同じ構成材料

でかつNチャネルMISFETのゲート電極膜よりもシリコン含有量が少ないタングステ

ンシリサイドで構成されたPチャネルMISFETを有し、NチャネルMISFETのゲ

ート電極膜の仕事関数が、PチャネルMISFETのゲート電極膜の仕事関数よりも小さ

い。

(もっと読む)

CMOSFET内の歪みを最適化するための構造体及び方法

【課題】 CMOSFET内の歪みを最適化するための構造体及び方法を提供すること。

【解決手段】 MOSFET内の歪みを最適化し、より具体的には、1つの種類(P又はN)のMOSFET内の歪みを最大にし、かつ、別の種類(N又はP)のMOSFET内の歪みを最小にし緩和する、PMOSFET及びNMOSFETの両方を含む歪みMOSFETの半導体構造体、及び歪みMOSFETを製造する方法が開示される。元の完全な厚さを有する歪み誘起CA窒化物コーティングが、PMOSFET及びNMOSFETの両方の上に形成され、この歪み誘起コーティングは、1つの種類の半導体デバイス内に最適化された十分な歪みをもたらし、別の種類の半導体デバイスの性能を劣化させる。歪み誘起CA窒化物コーティングは、別の種類の半導体デバイスの上で減少した厚さまでエッチングされ、減少した厚さの歪み誘起コーティングは、他方のMOSFET内でより少ない歪みを緩和し、他方のMOSFET内により少ない歪みをもたらす。

(もっと読む)

高い誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法

【課題】

高誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法を提供する。

【解決手段】

本発明の金属化合物は、TiCを含み、約4.75乃至約5.3eV、望ましくは、約5eVの仕事関数を有し且つ高誘電率の誘電体および界面層を含むゲート積層体上で熱的に安定する。更に、そのTiC金属化合物は、非常に意欲的な等価酸化膜厚(EOT)およびp型金属酸化物半導体(pMOS)装置における14Åよりも小さい反転層厚へのスケーリングを可能にする1000℃においても非常に効率的な酸素拡散バリアである。

(もっと読む)

半導体装置及びその製造方法

【課題】

静電保護用MISFETは、静電保護用MISFETの占有面積を従来よりも縮小する技術を提供する。また基板電流を発生しやすくすることで寄生バイポーラトランジスタを導通しやすくし、高い静電保護能力を備えた静電保護用MISFETを提供する。

【解決手段】

ドレインの非シリサイド領域の不純物濃度を薄くし、かつ接合を浅く形成することにより、従来よりも非シリサイド領域の比抵抗を高め、非シリサイド領域の占有面積を縮小する。さらに、非シリサイド領域の下方にウェルと同じ極性の中濃度不純物層を形成して、リーク電流の大きいpn接合を形成することにより基板電流を発生しやすくし、寄生バイポーラトランジスタを導通しやすくすることで、静電保護能力を高める。

(もっと読む)

半導体装置および半導体集積回路

【課題】 本発明は、素子面積の増大を招くこと無しに、静電放電によるサージ印加時の熱破壊に対する耐性を向上させた半導体装置および半導体集積回路を提供するものである。

【解決手段】 本発明の半導体装置は、接地線が接続された半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された抵抗ゲート部と、ゲート絶縁膜および抵抗ゲート部をゲート長方向に挟み、導体物からなるゲート側壁と、ゲート側壁の一方に接触する半導体基板表面に形成され、接地線が接続されたソース領域と、ゲート側壁の他方に接触する半導体基板表面に形成され、信号線もしくは電源線が接続されたドレイン領域と、を備えることを特徴とする。

(もっと読む)

階段状ソース/ドレイン領域を有するデバイス

【課題】階段状ソース/ドレイン領域を有するトランジスタを提供する。

【解決手段】階段状領域を設けることによって、リーク電流を最小限に留めると同時にチャネル領域のひずみを大きくするとしてもよい。このような階段状領域の形成は、基板内に2種類のリセスを形成して階段状のリセスとし、このリセス内にソース/ドレイン領域を形成することによって実現するとしてもよい。

(もっと読む)

MOS型半導体装置の製法

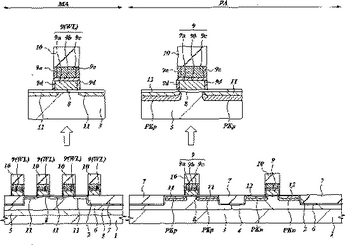

【課題】ドレイン側のポケット領域とLDD領域との間のオフセット距離のばらつきを低減できるMOS型半導体装置の製法を提供する。

【解決手段】半導体基板10の表面に形成したフィールド絶縁膜12の素子孔内にゲート絶縁膜14を形成した後、絶縁膜14及び12の上にドープトポリシリコン等からなるゲート電極層16及びキャパシタ用電極層18をそれぞれ形成する。絶縁膜12及び電極層16をマスクとするイオン注入処理によりポケット領域20,22を形成した後、電極層16,18を覆ってキャパシタ用絶縁層26をCVD法等により形成する。絶縁層26を介してのイオン注入処理により低濃度ソース、ドレイン領域28,30を形成する。ポケット領域22とLDD領域30との間のオフセット距離Lは、絶縁層26の厚さに対応して精度良く決定される。サイドスペーサ形成処理の後、高濃度ソース,ドレイン領域を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 良質でかつ良好な形状のサイドウォールを備えた半導体装置を形成する。

【解決手段】 ゲート電極側壁のサイドウォールを炭素含有シリコン窒化酸化膜を用いて形成する。炭素含有シリコン窒化酸化膜は、BTBASと酸素を原料に用い、BTBAS流量/酸素流量比を適当に設定すると共に、例えば約530℃等の低成膜温度のCVD法で成膜することができる。炭素含有シリコン窒化酸化膜を用いてサイドウォールを形成することで、窒素原子や炭素原子の寄与により、HF耐性向上やフリンジ容量低減を図れる。また、低温条件で成膜することにより、半導体基板内に導入されている不純物の不要な拡散が抑えられるようになる。これにより、トランジスタ特性を高めかつ安定化させ、半導体装置の高性能化、高品質化を図れるようになる。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】 後続するコンタクト・ホール工程で使用される層間絶縁(ILD)エッチング停止層を有する高電圧用トランジスタ・デバイスを提供する。

【解決手段】 エッチング停止層は、10Ω−cmより大きい抵抗を有する高抵抗膜である。この結果、ゲート部において5Vより大きい高電圧を駆動する場合のリークを防止し、破壊電圧は向上する。高電圧用デバイスの製造方法は、現在の低電圧デバイスの製造工程と中電圧デバイスの製造工程と混載可能である。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体措置で発生した熱を放熱しやすくすることによってESD耐圧に優れた半導体装置およびその製造方法を提供する。

【解決手段】 拡散層領域3に形成されたチャネル11の上には、ゲート絶縁膜7を介してゲート電極8が設けられている。また、ゲート電極8の側壁部には、サイドウォール9が形成されている。そして、ゲート電極8上とソース・ドレイン領域5上の一部とに、ゲート電極8およびサイドウォール9を被覆するようにしてシリサイドプロテクション膜10が形成されている。シリサイドプロテクション膜10が設けられていないソース・ドレイン領域の上には、シリサイドプロテクション膜10に隣接して金属シリサイド膜6が形成されている。ここで、シリサイドプロテクション膜10は、SiC膜およびSiOC膜の少なくとも一方からなるものとする。

(もっと読む)

延伸スペーサを利用した半導体デバイスおよびその形成方法

【課題】延伸スペーサを利用した半導体デバイスおよびその形成方法を提供する。

【解決手段】半導体デバイスは、半導体基板110を覆うゲートと、ゲートの側壁上にある誘電体ライナー150とを含む。この半導体デバイスは、誘電体ライナー150に隣接して誘電体ライナー150を越えるように半導体基板110に沿って横向きに延伸された延伸スペーサ170を含む。半導体デバイスは、半導体基板110の上面の下方に位置し、ゲート下のチャネル領域145に隣接するソース/ドレインをさらに含む。ソース/ドレインは、誘電体ライナー150および延伸スペーサ170下で延伸される。半導体デバイスは、ソース/ドレインの一部上を覆い、半導体基板110に沿って横向きに延伸するシリサイド領域190をさらに含む。従って、延伸スペーサ170はソース/ドレインの一部上において誘電体ライナー150とシリサイド領域190との間に形成される。

(もっと読む)

交互ガス供給による選択的エピタキシープロセス

一実施形態において、基板表面上にシリコン含有材料をエピタキシャル形成する方法であって、単結晶表面及び第2表面(アモルファス又は多結晶)を有する基板をプロセスチャンバー内に位置させるステップと、基板を、堆積ガスに露出されて、単結晶表面にエピタキシャル層を形成すると共に、第2表面に多結晶層を形成するステップとを備えた方法が提供される。堆積ガスは、シリコンソースと、少なくとも第2の元素ソース、例えば、ゲルマニウムソース、炭素ソース又はその両方とを含むのが好ましい。その後、この方法は、更に、基板をエッチング剤ガスに露出させて、多結晶層がエピタキシャル層より速い速度でエッチングされるようにするステップも備えている。基板は、堆積ガス及びエッチング剤ガスに順次に繰り返し露出されて、シリコン含有材料を形成する。一実施例において、堆積ガスはシランを含み、エッチング剤ガスは塩素及び窒素を含む。 (もっと読む)

半導体素子およびその製造方法

【課題】素子の微細化が可能でスイッチング性能の高い立体構造を有する電界効果型トランジスタである半導体素子を提供する。

【解決手段】ソース領域と、前記ソース領域の上部に配置された半導体機能層と及び、前記半導体機能層の上部に配置されたドレイン領域とを備え、前記半導体機能層は、前記ソース領域に対してほぼ垂直に配列した、複数の柱状あるいは円筒状の半導体物質からなる第1の部材と、前記第1の部材を取り囲み、前記ソース領域と絶縁体を介して配置された第2の部材から構成され、前記第2の部材はゲート領域と、絶縁体領域とから構成されており、前記第1の部材の平均直径が1nm以上30nm以下であり、前記第1の部材の平均間隔が3nm以上50nm以下であり、前記半導体層の酸素を除く主成分がシリコン、またはゲルマニウム、またはシリコンとゲルマニウムの混合物のいずれかである半導体素子を用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、シリサイドプロセスを適用したMOSFETにおいて、シリサイド膜をより大きく形成できるようにする。

【解決手段】たとえば、シリコン基板11の表面上に設けられたゲート電極16の側面には、それぞれ、内側ゲート側壁膜18および外側ゲート側壁膜21が形成されている。一方、ゲート電極16の形成位置を除く、シリコン基板11の表面部には、浅い低濃度拡散層17、および、二段構造の浅い高濃度拡散層19と深い高濃度拡散層22とが形成されている。そして、浅い高濃度拡散層19および深い高濃度拡散層22に対応するシリコン基板11の表面部には、それぞれの高濃度拡散層19,22の深さに応じて厚さの異なる二段構造のシリサイド膜23が形成されている。

(もっと読む)

MIS型半導体装置およびMIS型半導体装置の製造方法

ゲート絶縁膜に高誘電率膜を用いるMOSFETにおいて、基板−高誘電率膜間の低誘電率層(シリコン酸化膜)を増大させないようにするために、基板(1)上に高誘電率膜(3)、拡散バリア層(4)を堆積した後、高誘電率膜(3)の膜質改善のための熱処理を行う。次に、ゲート電極材料膜を堆積し、これをパターニングしてゲート電極(6)を形成する。このエッチング工程において、高誘電率膜3)はその側面がプラズマに曝されることにより、電荷が注入されまたダメージを受ける。この電荷を逃がしダメージを修復するために拡散バリア層(8)でゲート部を含む全面を被覆して熱処理を行う。その後、ソース・ドレイン領域となる不純物拡散層を形成する。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 MOSトランジスタのLDD(Lightly−Doped Drain)形成工程において、サイドウォールスペーサを半導体基板の削れなく形成する。

【解決手段】 半導体基板100上にゲート絶縁膜101を介してゲート電極102を形成する工程と、ゲート電極102を被覆するようにSiCwHxOyNz(w>0、x≧0、y>0、z≧0)で表される有機無機ハイブリッド膜106を堆積する工程と、有機無機ハイブリッド膜106の所定部分を酸化層108に変換する工程と、酸化層108を選択的に除去して、ゲート電極102の側壁に有機無機ハイブリッド膜からなるサイドウォールスペーサ109を形成する工程を含む。

(もっと読む)

半導体集積回路装置およびその製造方法

ポリメタルゲートを構成する高融点金属膜の洗浄工程における欠けを防止し、装置の特性を向上させ、また、洗浄効率を向上させるため、基板1上の低抵抗多結晶シリコン膜9a、WN膜9bおよびW膜9cを、窒化シリコン膜10をマスクにドライエッチングし、これらの膜よりなるゲート電極9を形成し、ウエットハイドロゲン酸化により薄い酸化膜9dを形成した後、RPN法を用いて窒化処理を行い、ゲート電極の側壁から露出したW膜9cをWN膜9eとする。その結果、その後の洗浄工程、例えば、n−型半導体領域11やp−型半導体領域12の形成時に行われる、1)レジスト膜のホトリソグラフィー工程、2)不純物の注入工程、3)レジスト膜の除去工程および4)基板表面の洗浄工程が繰り返し行われても、W膜9cの欠けを防止でき、また、洗浄液としてU洗浄液やフッ酸系の洗浄液のような強い洗浄液を用いることができる。  (もっと読む)

(もっと読む)

半導体構造およびそれを形成する方法(金属酸化物の付着を介して形成されたしきい電圧制御層を含む窒素含有電界効果トランジスタ・ゲート・スタック)

【課題】 ゲート誘電体とゲート電極との間にVt安定化層を含む半導体構造を提供することにある。

【解決手段】 Vt安定化層は、構造のしきい電圧およびフラットバンド電圧を目標値に安定化することができ、窒化金属酸化物または窒素なし金属酸化物を含み、Vt安定化層が窒素なし金属酸化物を含む条件で半導体基板またはゲート誘電体のうちの少なくとも一方が窒素を含む。また、本発明は、このような構造を形成する方法も提供する。

(もっと読む)

201 - 220 / 246

[ Back to top ]