Fターム[5F140BJ27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | コンタクト構造 (1,444) | プラグを有するもの (1,074)

Fターム[5F140BJ27]に分類される特許

361 - 380 / 1,074

半導体装置及びその製造方法

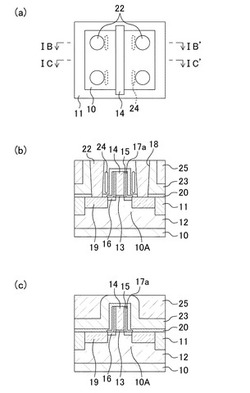

【課題】前記従来のエアーギャップを有するMISトランジスタ及びその製造方法では、ゲート電極の周囲にエアーギャップを設けるため、ゲート電極に近接して応力絶縁膜を形成することができない。

【解決手段】半導体装置は、ゲート絶縁膜13と、ゲート電極14と、ソースドレイン領域19と、コンタクトプラグ22と、応力絶縁膜23とを備えている。ゲート電極14の側方のうちゲート電極14とコンタクトプラグ22との間に位置する領域のみに空洞24が形成されており、応力絶縁膜23は半導体基板10上にゲート電極14を覆うように形成されており、半導体基板10におけるゲート電極14の直下に位置するチャネル領域に対して応力を生じさせる。

(もっと読む)

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

半導体装置

【課題】ゲート・ドレイン間容量、ゲート・ソース間容量を低減し、微細プロセスに混載しやすい電界効果トランジスタの半導体装置を提供する。

【解決手段】基板10に設けられたPウエル11と、Pウエル11に設けられたN+ソース13と、N+ドレイン12と、Pウエル11とN+ドレイン12の間に設けられた低濃度N型領域40と、領域40に設けられた絶縁層17と、N+ソース領域13と領域40との間に挟まれたPウエル11上にゲート絶縁層を介して設けられた制御電極と、制御電極と離隔して、絶縁層17上に設けられた補助電極18と、N+ソース13と接続された第1の主電極31と、N+ドレイン12と接続された第2の主電極32と、を備え、主電極31,32間で流れる主電流の方向を第1の方向と規定し、第1の方向と垂直な方向を第2の方向と規定した場合、絶縁層17の第2の方向に沿った幅が、主電極32に向かって細くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】容易に製造することができ、トランジスタの性能を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上にゲート絶縁膜2及びゲート電極3が形成されている。半導体基板1の表面の、平面視でゲート電極3を挟む位置に2個の不純物拡散層4が形成されている。2個の不純物拡散層4の表面に、ゲート絶縁膜2と半導体基板1との界面より低くなった掘り込み部6が設けられている。更に、半導体基板1のゲート絶縁膜2下の領域(チャネル)に応力を付加する応力付加膜が、少なくとも掘り込み部6内に位置している。

(もっと読む)

半導体装置の製造方法

【課題】MISFETのしきい値のばらつきを抑制する。

【解決手段】半導体基板1に素子分離領域2を形成し、MISFETのしきい値調整用のチャネルドープイオン注入を行なってから、ゲート絶縁膜5a,5bおよびゲート電極GE1,GE2を形成する。それから、イオン注入によりエクステンション領域7a,7bおよびハロー領域8a,8bを形成し、更に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入することにより拡散防止領域10a,10bを形成する。その後、ゲート電極GE1,GE2の側壁上にサイドウォールSWを形成してから、イオン注入により、ソース・ドレイン用のn+型半導体領域11aおよびp+型半導体領域11bを形成して、nチャネル型MISFETおよびpチャネル型MISFETが形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の仕事関数を得ると共にトランジスタの駆動力を劣化させない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、半導体基板1の上に形成された界面層5と、界面層5の上に形成された高誘電率ゲート絶縁膜6と、高誘電率ゲート絶縁膜6上に形成されたゲート電極とを備える。高誘電率ゲート絶縁膜6はランタンを含有し、高誘電率ゲート絶縁膜6におけるゲート電極との界面に含まれているランタンの濃度は、高誘電率ゲート絶縁膜における界面層との界面に含まれているランタンの濃度よりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜形成工程のような大きな熱負荷を避けて、チャネルの最上面の不純物濃度を薄くした、深さ方向のドーピング・プロファイルを実現し、オン電流が向上する半導体装置の製造方法を提供することである。

【解決手段】 ゲート電極形成後にゲート電極をマスクにして角度10度以下でチャネル不純物をイオン注入し、この後、チャネル不純物の活性化を、基板表面から所定の深さのチャネル不純物濃度がゲート長方向に一定になるように、RTAを用いたアニールで行う、さらに、その後のエクステンション/ハロー注入、深いS/D注入の後の活性化を、拡散レスアニールで行う。

(もっと読む)

半導体装置

【課題】トランジスタの集積化を妨げることなく、トランジスタの駆動力を向上させる半導体装置を提供する。

【解決手段】所定の結晶からなる半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、ゲート幅方向に凸部を有して前記半導体基板内に形成され、前記所定の結晶とは異なる格子定数を有するエピタキシャル結晶が埋め込まれたソース・ドレイン領域と、を具備するトランジスタと、前記凸部以外の前記ソース・ドレイン領域に接続されたコンタクトプラグと、を備えた半導体装置を提供する。

(もっと読む)

半導体装置、半導体装置の製造方法、静電放電保護素子

【課題】製造効率を向上すると共に、内部回路の保護を的確に行うことが容易に可能な半導体装置、半導体装置の製造方法、静電放電保護素子を提供する。

【解決手段】半導体基板20に第1導電型の第1半導体領域21が形成され、その両側に第2導電型の第2及び第3半導体領域(22,23)が形成され、第1半導体領域の上方に絶縁膜を介してゲート電極32が形成され、第1半導体領域と第3半導体領域の接合面をまたいでそれらにかかるように第1導電型の第4半導体領域30が形成され、第2及び第3半導体領域にソース領域26とドレイン領域28が形成され、ゲート電極及びソース領域が接地され、内部回路に接続された入力パッド40がドレイン領域に接続され、入力パッドにサージ電圧が入力された際にドレイン領域と第4半導体領域との間でツェナー降伏が生じて寄生バイポーラトランジスタがオン状態となり、サージ電圧を放電する。

(もっと読む)

半導体装置

【課題】温度が上昇するほどキャリアの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、素子形成面が(110)面方位の半導体基板上10−1に、チャネル長方向が<−110>方向に沿って配置される絶縁ゲート型電界効果トランジスタpMOSと、前記半導体基板における素子分離領域の溝内に埋め込まれ、正の膨張係数を有し、前記絶縁ゲート型電界効果トランジスタに、動作熱によりチャネル長方向に沿って圧縮応力を加える第1素子分離絶縁膜11−1とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】隣接する活性領域間が狭くなった場合においても、コンタクトプラグと拡散層とのコンタクト抵抗を低く抑えることが可能な半導体装置及びその製造方法を提供する。

【解決手段】X方向に延在する活性領域102内に設けられたゲートトレンチ103gt1、103gt2及びダミーゲートトレンチ103dgtと、活性領域102を横切るY方向に延在し、各トレンチ103gt1、103gt2、103dgt内にそれぞれ少なくとも一部が埋め込まれたゲート電極104g1、104g2及びダミーゲート電極104dgとを有し、ゲート電極104g1とその両側に設けられた拡散層105a1,105a2とからなるトランジスタ109と、ゲート電極104g2とその両側に設けられた拡散層105b1,105b2とからなるトランジスタ110は、拡散層105a2と拡散層105b1との間に配置されたダミーゲート電極104dgにより絶縁分離される。

(もっと読む)

カーボンナノチューブの製造装置及びカーボンナノチューブを分別する方法

【課題】カーボンナノチューブを特性毎に分別する。

【解決手段】本発明の例に関わるカーボンナノチューブの分別装置は、第1の磁気特性を有する第1のカーボンナノチューブSCNTと第2の磁気特性を有する第2のカーボンナノチューブMCNTとが共通に導入される導入部2と、第1及び第2のカーボンナノチューブSCNT,MCNTをそれぞれ回収する第1及び第2の回収部4A,4Bと、第1及び第2のカーボンナノチューブSCNT,MCNTを導入部2から回収部4A,4Bまで搬送する搬送部3と、搬送部3に隣接して配置され、カーボンナノチューブSCNT,MCNTに対して磁場Hを印加する磁場発生部5とを具備し、第1の磁気特性と磁場Hとの相互作用によって、第1のカーボンナノチューブSCNTと第2のカーボンナノチューブMCNTとを分別する。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISのソース・ドレイン領域端部における転位の発生および拡散抵抗の上昇を防止する。

【解決手段】CMISにおけるソース・ドレイン領域12、14の形成時、シリコン基板1に不純物をイオン注入する前に、Pウエル層4には転位抑制元素としてアルゴンを打ち込み、かつNウエル層5には窒素を転位抑制元素として打ち込む。これにより転位の発生を抑制しつつ、かつ、Pウエル層4とNウエル層5それぞれに適した転移抑制元素を打ち分けることで拡散抵抗の上昇を抑制し、歩留まりを向上させ、素子の信頼性を高めることができる。

(もっと読む)

半導体装置の製造方法

【課題】デュアルメタルゲート構造を有する半導体装置において、ゲート電極除去する工程において、ゲート絶縁膜に与える損傷を抑える。

【解決手段】 第1のトランジスタと第2のトランジスタとを備える半導体装置において、第1のトランジスタは、第1の仕事関数を有する第1の材料からなる第1のゲート電極と、第1のゲート絶縁膜とを含む。また、第2のトランジスタは、第2の仕事関数を有する第2の材料からなる第2のゲート電極と、第2のゲート絶縁膜とを含む。ここで、第1のゲート絶縁膜は、高誘電率膜と、第1の高誘電率膜上に形成された第1の絶縁膜とを含むものとする。第2のゲート絶縁膜においては、高誘電率膜上部に形成した第1の絶縁膜を、第1のゲート電極を除去した後に除去する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクトプラグとゲート電極との間のショートおよび/またはコンタクトプラグとシリコンピラーとの間のショートを防止した半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】基板1上に立設された第一のシリコンピラー2と、その側面を覆う絶縁膜5と、絶縁膜5を覆うとともに、その先端部6aが第一のシリコンピラー2の先端部2aよりも基板1よりに位置してなるゲート電極6と、からなる縦型Tr部101と、基板1上に立設された第二のシリコンピラー2’と、その側面を覆う絶縁膜5’と、絶縁膜5’を覆うとともに、その先端部6’aが第二のシリコンピラー2’の先端部2’aよりも基板1から離れた側に位置してなり、ゲート電極6に接続されてなるゲートコンタクト電極6’と、からなるゲートコンタクト部102と、を有する半導体装置111を用いることにより、上記課題を解決できる。

(もっと読む)

半導体素子及びその製造方法

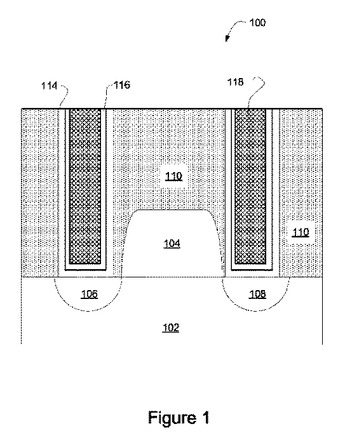

【課題】LDMOS素子においてのオン抵抗を減少させることができる半導体素子及びその製造方法を提案する。

【解決手段】本実施例による半導体素子は、第1導電型のウェル110が形成された基板100と、及びゲート電極182を含んで、前記基板100に形成されるLDMOS素子として、前記ゲート電極182一側の基板100に形成されるソース領域132と、前記ゲート電極182他側の基板100に形成されるドレイン領域133と、前記ゲート電極182下側の基板100に形成される第1導電型の不純物層140を含むLDMOS素子と、を含む。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを高選択的に除去することのできる半導体装置の製造方法を提供すること。

【解決手段】半導体装置1の製造工程において、シリコン基板2上にゲート絶縁膜8を形成し、このゲート絶縁膜8上にダミーゲート32を形成する。ダミーゲート32の側面には、サイドウォール10を形成する。サイドウォール10の形成後、ダミーゲート32を被覆する第1絶縁層17を形成し、第1絶縁層17の表面がダミーゲート32の表面と面一となるように加工する。第1絶縁層17の加工後、ダミーゲート32に、ダミーゲート32とサイドウォール10とのエッチング選択比を確保可能なエッチング液を供給することにより、ダミーゲート32をウェットエッチングする。そして、ダミーゲート32のエッチングにより現れるゲート絶縁膜8上に、金属材料からなるゲート電極9を形成する。

(もっと読む)

電子デバイスの製造方法及び設定装置

【課題】電子デバイスの更なる微細化及び高集積化が進んでも、リソグラフィー及びエッチングにより被加工対象の極めて高い寸法精度を達成し、信頼性の高い電子デバイスを実現する。

【解決手段】被加工対象上に形成されたレジスト膜を加工してレジストパターンを形成する工程と、レジストパターンをマスクとして、所定のエッチング条件で被加工対象をエッチングする工程とを実行する際に、形成されたレジストパターンの寸法及び形状(膜厚及びテーパ角度)を測定し、測定されたレジストパターンの寸法及び形状に基づいて前記エッチング条件を調整する。

(もっと読む)

半導体装置

【課題】ソース/ドレインの配線抵抗の上昇を抑制し、ゲート配線の低抵抗化を図る。

【解決手段】もっとも半導体基板10側に位置する第1配線層20は、半導体素子のソース領域15に電気的に接続された第1ソース配線21と、半導体素子のドレイン領域12に電気的に接続された第1ドレイン配線22と、ゲート電極17に電気的に接続された中継部23とを備えている。そして、第1ソース配線21および第1ドレイン配線22にそれぞれ設けられたソース側凹部21aおよびドレイン側凹部22aによって設けられた間隙24にこの中継部23を配置する。

(もっと読む)

361 - 380 / 1,074

[ Back to top ]