Fターム[5F140BJ27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | コンタクト構造 (1,444) | プラグを有するもの (1,074)

Fターム[5F140BJ27]に分類される特許

301 - 320 / 1,074

半導体装置及びその製造方法

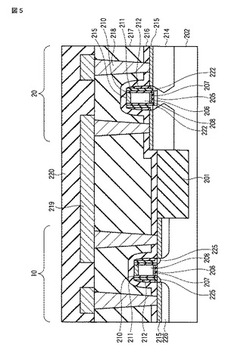

【課題】pMOSトランジスタにcSiGeとeSiGeを適用し、且つゲート絶縁膜におけるダメージ発生を防止でき、素子特性の向上及びしきい値制御性の向上をはかる。

【解決手段】pMOSトランジスタのチャネル部及びソース・ドレイン領域にSiGeを用いた半導体装置において、Si基板202上の一部に形成され、pMOSトランジスタのチャネルとなる第1のSiGe層205と、第1のSiGe層205上にゲート絶縁膜206を介して形成されたゲート電極208と、pMOSトランジスタのソース・ドレイン領域に埋め込み形成され、且つチャネル側の端部が基板表面よりも深い位置でチャネル側に突出するように形成された第2のSiGe層214と、第1のSiGe層205と第2のSiGe層214とを分離するように、基板の表面部でSiGe層205,214間に挿入されたSi層222とを備えた。

(もっと読む)

半導体装置の製造方法

【課題】チャネルに大きな歪を生じさせることができ、制御を容易に行うことができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、絶縁膜3、多結晶シリコン膜4及びアモルファスシリコン膜5を含む積層体を、ゲート電極の平面形状に形成する。多結晶シリコン膜4及びアモルファスシリコン膜5の側方にサイドウォール6を形成する。サイドウォール6をマスクとして半導体基板1の表面にp型不純物を導入して不純物導入領域7を形成する。サイドウォール6をマスクとして不純物導入領域7の表面に溝8を形成する。溝8内にSiGe層9を選択成長させる。アモルファスシリコン膜5を選択的に除去して、多結晶シリコン膜4を露出する。多結晶シリコン膜4上に導電層11を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】LDMOSFETを有する半導体装置では、ソース電極が裏面にあることから、表面のソース・コンタクト領域と裏面のソース電極間の電気抵抗を低減するため、上面からP型エピタキシャル層を貫通してP+型基板内に伸びるボロンを高濃度にドープしたポリ・シリコン埋め込みプラグが設けられている。このポリ・シリコン埋め込みプラグの周辺のシリコン単結晶領域に転位が発生しており、これにより、リーク不良が誘発されていることが明らかとなった。

【解決手段】本願発明は、相互に不純物濃度の異なる第1及び第2の半導体層の境界面を貫通するシリコン系プラグを有する半導体装置であって、このプラグの少なくとも内部は多結晶領域であり、この多結晶領域表面の内、先の境界面の両側近傍は、固相エピタキシャル領域で覆われている。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチゲート構造を有するトランジスタにおいて、サブスレッショルド特性を良好にする。

【解決手段】半導体装置100は、第1導電型のソース領域112およびドレイン領域113、これらの間に第2導電型のチャネル領域108が形成された基板102と、チャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162を埋め込むように形成されたゲート電極122とを有するトランジスタを含む。チャネル領域108において、基板102表面およびトレンチ162の底部には、それぞれ第2の高濃度領域132および第1の高濃度領域130が形成されており、第2導電型の不純物濃度がトレンチ162側方における第2導電型の不純物濃度よりも高くなっている。また、第1の高濃度領域130の第2導電型の不純物濃度が第2の高濃度領域132の第2導電型の不純物濃度以上である。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、極めて高い歩留まりでゲート電極について均一で十分なフル・シリサイド化を確実に実現する。

【解決手段】ゲート電極104a,104b及びソース/ドレイン領域107a,107bのNiシリサイド化を行うに際して、1回目のNiシリサイド化の後に1回目のmsecアニール処理であるフラッシュランプアニール処理を行い、2回目のNiシリサイド化、更には必要であれば2回目のフラッシュランプアニール処理を行って、ソース/ドレイン領域107a,107b上には1回目のフラッシュランプアニール処理で形成されたNiSi層111bを維持した状態で、フル・シリサイドゲート電極115a,115bを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】フィントランジスタの素子分離膜中にボイドが発生しにくい構造の半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1の基準面103及び第1の基準面103よりも高い位置に設けられた第2の基準面104を有するシリコン基板100を備えている。シリコン基板100の上には、互いに間隔をおいて、上面が第2の基準面103よりも高い位置にあり、フィントランジスタを構成するフィン121及びフィン122が形成されている。第1の基準面103の上には、上面がフィン121及びフィン122の上面よりも低い位置にある第1の素子分離膜131Aが形成されている。第1の基準面103を挟んで隣接する2つのフィン121の間隔は、第2の基準面104を挟んで隣接する2つのフィン122の間隔よりも広い。

(もっと読む)

基板処理装置、半導体デバイスの製造方法及び半導体デバイス

【課題】酸素を含む高品質な薄膜の形成が可能で、水分発生器やオゾン発生器を必要とせず、低コスト化を実現する。

【解決手段】複数の基板を積層して収容する反応管203と、第1の原料ガスを供給する第1のガス供給手段232aと、O含有ガスとH含有ガスとを含む第2の原料ガスを供給する第2のガス供給手段232bと、反応管内を排気する排気手段246と、を有し、第1のガス供給手段は、反応管の下部に接続され第1の原料ガスを供給する第1のガス供給配管と、反応管内に立設され複数のガス供給口248aを有するガスノズル233と、を備え、第2のガス供給手段は、反応管の頂部に接続され第2の原料ガスを供給する第2のガス供給管を備え、第1の原料ガスと第2の原料ガスとを互いに混合することなく交互に供給して基板上に酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタ特性を向上させる。

【解決手段】STI109と、STI109によって互いに分離されたp型ウェル102及びn型ウェル103と、p型ウェル102及びn型ウェル103上に形成されたSiGe膜108とを有するSi基板101を用意する工程と、n型ウェル103上に位置するSiGe膜108をSiO2膜116で被覆する工程と、SiO2膜116をマスクとして酸化処理を行うことによりp型ウェル102上に形成されたSiGe膜108を酸化し、SixGeyOz膜117を形成する工程((c))と、SixGeyOz膜117を除去する工程((d))と、を行い、半導体装置を製造する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】同一の工程で、同一半導体基板上に異なる構造のトランジスタを形成する半導体装置の提供。

【解決手段】半導体基板上に第一及び第二のゲート電極40,41を形成する工程と、第一のゲート電極の側壁面に第一の絶縁層122を形成するとともに、第二のゲート電極のゲート幅方向両側の半導体基板上にエピタキシャル成長層9aを形成する工程と、第二のゲート電極の側壁面に第二の絶縁層を形成する工程と、第一の絶縁層及び第二の絶縁層を覆うように第三の絶縁層を形成する工程と、第二の絶縁層を覆う第三の絶縁層を除去する工程と、第一のゲート電極のゲート幅方向両側の半導体基板及びエピタキシャル成長層にそれぞれ不純物を拡散させて、第一及び第二の不純物拡散領域6,8を形成する工程と、第一及び第二の不純物拡散領域にコンタクトプラグ12,15を接続させる工程と、を具備してなることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】nチャネル型MISFETQnは、半導体基板1のp型ウエルPWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3aを介して形成されたゲート電極GE1を有し、pチャネル型MISFETQpは、n型ウエルNWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3bを介して形成されたゲート電極GE2を有している。ゲート電極GE1,GE2は、金属膜7とその上のシリコン膜8との積層構造を有している。Hf含有絶縁膜3aは、Hfと希土類元素とSiとOとNとからなる絶縁材料膜またはHfと希土類元素とSiとOとからなる絶縁材料膜であり、Hf含有絶縁膜3bは、HfとAlとOとNとからなる絶縁材料膜またはHfとAlとOとからなる絶縁材料膜である。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】突出部の側面が凹凸状とされ、前記側面を覆うようにゲート酸化膜を形成したときに、実効的なチャネル長が増加して、ピラー型MOSトランジスタの電流駆動能力が低下するという課題があった。

【解決手段】基板と、前記基板の一面から垂直方向に突出された突出部7とを備え、突出部7の先端側の上部拡散層と、基端側の下部拡散層と、側面7cを覆うゲート絶縁膜14と、ゲート絶縁膜14を覆うゲート電極15と、を有し、チャネルが前記垂直方向となるピラー型MOSトランジスタ51を具備し、突出部7が平面視八角形状であり、突出部7の側面7cが{100}面からなる4つの主表面8a、8b、8c、8dと、{110}面および{111}面からなり、前記主表面8a、8b、8c、8dよりも面積が小さい4つの副表面9a、9b、9c、9dとからなる半導体装置101を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上にヒューズ素子を備える半導体装置において、ヒューズを切断しやすくし、かつヒューズ切断状態を確実に得る。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとヒューズ素子100を備える。ヒューズ素子100は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層34と、シリコン層34の上の少なくとも一部を覆うシリサイド層73と、からなる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離構造の面積を増大させることなく、素子分離構造の表面の後退量を低減させる。

【解決手段】半導体基板11の表面よりも低い位置に埋め込み絶縁層12を埋め込み、埋め込み絶縁層12と材料の異なるキャップ絶縁層13を半導体基板11と埋め込み絶縁層12と間の段差12aの肩の部分にかからないようにして埋め込み絶縁層12上に形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と半導体基板間のリーク位置を、TEG素子を用いて非接触で迅速に測定することができる半導体装置の製造方法を提供する。

【解決手段】

TEG素子101は、絶縁分離溝2により画定さるTEG素子形成領域8上にゲート絶縁膜3を介して形成された一端が半導体基板1に接続されたゲート電極4と、少なくともゲート電極の両側に形成された不純物領域5aと、不純物領域より深い位置に素子形成領域の底全面を塞ぐように設けられ、不純物領域を半導体基板から電気的に絶縁する絶縁分離層7とを有する。荷電粒子ビームを不純物領域5aの一端及び他端に照射したときの内部抵抗R1、R2の差、及び不純物領域5aの両端間の抵抗Robを用いて、リーク位置を決定する。

(もっと読む)

誘電体分離型半導体集積装置、及び半導体集積装置の製造方法

【課題】微細なMOS素子と共存する。

【解決手段】支持基板5と、埋込シリコン酸化膜6と、第1高濃度不純物層9及び低不純物濃度層とからなる活性層15、とで構成されるSOI基板を適用した誘電体分離型半導体集積装置10において、高耐圧半導体素子形成領域を囲んで形成される素子分離領域は、多重溝100と、多重溝の側壁に設けた第1酸化膜105と、第1酸化膜と隣接して多重溝側壁に沿って形成された第2高濃度不純物層110と、第2高濃度不純物層の略上部にLOCOS酸化膜50を介して配設された低抵抗層P2と、前記低抵抗層に積層された第2酸化膜70,75,80と、を備えて構成され、低抵抗層は、第2高濃度不純物層、あるいはドレイン電極と略同電位であり、第2酸化膜の表面でエミッタ電極が前記高耐圧半導体素子形成領域から隣接領域へ引き出されている。

(もっと読む)

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

半導体記憶装置

【課題】縦型トランジスタSGTで構成されたCMOS型6T−SRAMにおいて、小さいSRAMセル面積と安定した動作マージンを実現する。

【解決手段】6個のMOSトランジスタを用いて構成されたスタティック型メモリセルにおいて、前記メモリセルを構成するMOSトランジスタは、基板上に形成され、ドレイン、ゲート、ソースが垂直方向に配置され、ゲートが柱状半導体層を取り囲む構造を有し、前記基板は第1の導電型を持つ第1の活性領域と第2の導電型を持つ第2の活性領域からなり、それらが基板表面に形成されたシリサイド層を通して互いに接続されることにより小さい面積のSRAMセルを実現する。また、基板上に配置される第1のウェルと同一の導電型を持つドレイン拡散層のそれぞれを第1のウェルと反対の導電型を持ち、第1のウェルより浅い第2のウェル及び第3のウェルで囲むことにより、基板へのリークを抑制する。

(もっと読む)

301 - 320 / 1,074

[ Back to top ]