Fターム[5F140BK25]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース、ドレイン電極形成前の処理 (1,173) | コンタクトホールの形成 (1,071)

Fターム[5F140BK25]の下位に属するFターム

エッチング (548)

Fターム[5F140BK25]に分類される特許

61 - 80 / 523

半導体装置及びその製造方法

【課題】LDMOSトランジスタに係る半導体装置の高速動作を可能とする。

【解決手段】P型ウエル層3の表面に形成された複数の素子分離膜4の中央部に開口溝5を形成する。開口溝5の側壁から開口溝5の内側に向かってゲート絶縁膜6を介して延在するゲート電極7を形成する。ゲート電極7をマスクにしてセルフアラインでボロンの斜めイオン注入により開口溝5内のP型ウエル層3にP型ボディ層8を形成する。

ゲート電極7をマスクに砒素のイオン注入によりP型ボディ層8にN+型ソース層9を、同時に2つの素子分離膜4間のP型ウエル層3にN+型ドレイン層10を形成する。素子分離膜4の下方のP型ウエル層3にP型ボディ層8の端部からN+型ドレイン層10に延在するN−型ドリフト層を形成する。この際、P型ボディ層8の端部から開口溝5の側壁下部までの領域AのN−型ドレイン層11の幅をできるだけ小さくなるよう制御する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】金属酸化膜または金属シリケート膜を含む薄膜ゲート絶縁膜を有する半導体装置の製造方法において、VFBを十分に制御し、Vthを十分に制御すること。

【解決手段】基板1上に、第1の金属の酸化膜、または、第1の金属のシリケート膜からなる第1高誘電率ゲート絶縁膜5を形成する第1工程と、第1高誘電率ゲート絶縁膜5上に、第2の金属の酸化膜からなる第2高誘電率ゲート絶縁膜6を形成する第2工程と、第2高誘電率ゲート絶縁膜6上に、ゲート電極膜7を形成する第3工程と、を有し、前記第2工程では、第2の金属元素および炭化水素基からなる主原料と、溶媒材料と、を混合した混合材料を用いて、原子層蒸着法により第2高誘電率ゲート絶縁膜6を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上部拡散層が平面積の狭いものであっても、上部拡散層および上部拡散層上に設けられた配線とのコンタクト抵抗を大きくすることなく、上部拡散層と配線とを接続できる半導体装置を提供する。

【解決手段】柱状半導体5と、柱状半導体5上に形成された上部拡散層15と、上部拡散層15上に形成された接続プラグ24とを備え、上部拡散層15が、平面視島状の複数の島状部を有するものであり、接続プラグ24が、導電材料からなり、前記複数の島状部から選ばれる第1島状部と前記第1島状部に隣接する第2島状部との間の隙間を跨って、前記第1島状部の上面の少なくとも一部から前記第2島状部の上面の少なくとも一部まで連続して配置されている半導体装置とする。

(もっと読む)

ワイドギャップ半導体基板およびワイドギャップ半導体装置の製造方法

【課題】ワイドギャップ半導体基板の位置検出を、可視光を用いて高精度に行う。

【解決手段】一実施形態によれば、ナローギャップ半導体基板(例えばSi基板2)の主面の所定の位置に彫り込み型のアライメントマーク4が形成されたナローギャップ半導体基板のその主面上にワイドギャップ半導体層(例えばGaN層19)をエピタキシャル成長したことにより、基板位置決め用のアライメントマークが予め埋め込まれているワイドギャップ半導体基板を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】素子分離領域13は、溝11に埋め込まれた酸化シリコン膜からなり、上部が半導体基板1から突出しており、半導体基板1から突出している部分の素子分離領域13の側壁上に、窒化シリコンまたは酸窒化シリコンからなる側壁絶縁膜SW1が形成されている。MISFETのゲート絶縁膜は、ハフニウムと酸素と低しきい値化用の元素とを主成分として含有するHf含有絶縁膜5からなり、メタルゲート電極であるゲート電極GEは、活性領域14、側壁絶縁膜SW1および素子分離領域13上に延在している。低しきい値化用の元素は、nチャネル型MISFETの場合は希土類またはMgであり、pチャネル型MISFETの場合は、Al、TiまたはTaである。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

MOSトランジスタおよびその製造方法、半導体集積回路装置

【課題】MOSトランジスタのチャネル領域に、基板上に形成した応力膜からより効率的に応力を印加する半導体装置の構造及びその製造方法を提供する。

【解決手段】MOSトランジスタは、n型またはp型のソース・ドレイン領域21e〜hと、素子分離領域21Iからチャネル領域に向かって延在し、ソース・ドレイン領域21e〜hを覆って形成された、引張応力、圧縮応力のいずれかである応力膜27A、27Bを備える。応力膜27A,27Bは、ゲート電極23A,23Bの側壁面に沿って、ただし側壁面からは隙間32A〜Dを介して形成される。ソース・ドレイン領域21e〜hがn型である場合、応力膜の応力は引張応力であり、ソース・ドレイン領域21e〜hがp型である場合、応力膜の応力は圧縮応力である。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタが設計より低い閾値電圧で動作し始めるという寄生トランジスタ動作を抑制する。

【解決手段】半導体装置100は、基板102の素子形成領域に形成されたトレンチ162、トレンチ162の側壁および底面に形成されたゲート絶縁膜120、トレンチ162を埋め込むようにゲート絶縁膜120上に形成されたゲート電極122、基板102表面のゲート長方向の一方の側に形成されたソース領域112、およびゲート長方向の他方の側に形成されたドレイン領域113、を有するトランジスタを含む。ここで、ゲート電極122は、トレンチ162外部の基板102上にも露出して形成され、ゲート電極122は、ゲート長方向における、トレンチ162の両端部上部が覆われるとともに、中央部に少なくとも一つ深さが基板まで達する凹部が形成されるように設けられている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】規則的に配列した複数の微細な開口部OPを有するフィルタFLを通過したイオンビーム22をレンズ26で収束して半導体ウエハ1Wに照射することにより、チャネルドープイオン注入を行なう。この際、フィルタFLには、イオンビーム22と同じ極性の電圧を印加する。フィルタFLの開口部OPの中央部に向かって入射した不純物イオンは、そのまま直進して開口部OPを通過することができるが、フィルタFLの開口部OPの中央部以外の領域に向かって入射する不純物イオンは、フィルタFLによる電場によって進行方向が曲げられて、開口部OPを通過することができない。このため、半導体ウエハ1Wに注入された不純物イオンは、規則的な配列を有したものとなり、MISFETのしきい値電圧のばらつきを抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】高耐電圧により大電流化が可能で、オン抵抗が低く高速動作が可能で、高集積化と省エネルギーが可能で、素子間分離の容易な、電気熱変換素子駆動用の半導体装置を提供する。

【解決手段】電気熱変換素子とそれに通電するためのスイッチング素子とがp型半導体基体1に集積化されている。スイッチング素子は、半導体基体1の表面に設けられたn型ウェル領域2と、それに隣接して設けられチャネル領域を提供するp型ベース領域6と、その表面側に設けられたn型ソース領域7と、n型ウェル領域2の表面側に設けられたn型ドレイン領域8,9と、チャネル領域上にゲート絶縁膜を介して設けられたゲート電極4とを有する絶縁ゲート型電界効果トランジスタである。ベース領域6は、ドレイン領域8,9を横方向に分離するように設けられた、ウェル領域2より不純物濃度の高い半導体からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】pチャネル型の電界効果トランジスタのしきい値電圧を確実に制御して所望の特性が得られる半導体装置と、その製造方法とを提供する。

【解決手段】温度約700〜900℃のもとで施す熱処理に伴い、素子形成領域RPでは、アルミニウム(Al)膜7a中のアルミニウム(Al)がハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)が添加される。また、チタンアルミニウムナイトライド(TiAlN)膜からなるハードマスク8a中のアルミニウム(Al)とチタン(Ti)とがハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)とチタン(Ti)とが添加される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホール形成時の重ね合わせずれに起因したリークの増大やコンタクト抵抗の上昇が抑制された半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100と、半導体基板100上にゲート絶縁膜101を介して形成されたゲート電極102と、ゲート電極102の側壁上に形成されたサイドウォールスペーサ150と、半導体基板100のうち、ゲート電極102及びサイドウォールスペーサ150を間に挟んで両側に形成されたソースドレイン領域106と、ゲート電極102、サイドウォールスペーサ150、及び半導体基板100の上面を覆う応力絶縁膜110とを備えている。サイドウォールスペーサ150は、少なくとも中央部のゲート長方向膜厚よりも上部のゲート長方向膜厚の方が大きくなっている。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

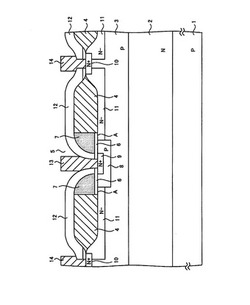

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

半導体装置の製造方法

【課題】ダミーシリコンピラーを用いてゲート電極を延長する場合の、シリコンピラーにおける反り変形の発生を抑制する。

【解決手段】半導体装置の製造方法は、第1及び第2のシリコンピラー3,4の側周面3a,4aに形成されたゲート絶縁膜9を覆うゲート電極材料を成膜する工程を備え、ゲート電極材料の成膜量は、ゲート絶縁膜9を介して側周面3aを覆う第1の部分と、ゲート絶縁膜9を介して側周面4aを覆う第2の部分とが接触しないよう制御され、第1及び第2の部分を覆うとともに第1の部分と第2の部分の間の領域を埋めるマスク絶縁膜を形成する工程と、マスク絶縁膜をマスクとして用いてゲート電極材料をエッチングすることにより、ゲート絶縁膜9を介してそれぞれ側周面3a,4aを覆うゲート電極101,102と、ゲート電極101,102とを電気的に接続する導体膜11とを形成する工程とをさら備える。

(もっと読む)

半導体装置

【課題】本発明は、不純物拡散層と半導体基板との間に形成される空乏層中におけるGIDLを抑制することのできる半導体装置を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成された第2の溝32と、少なくとも第2の溝32の側面32aを覆うゲート絶縁膜38と、ゲート絶縁膜38を介して、第2の溝32の側面32aに形成され、その上端面45aが半導体基板11の表面11aより低い位置にあってゲート電極39となる第1の導電膜45と、第1の導電膜45に形成され、その上端面46aが第1の導電膜45の上端面45bよりも高く、かつ半導体基板11の表面11aより低い位置にあってゲート電極39となる第2の導電膜46と、第1の導電膜45の上端面45b、及び第1の導電膜45の上端面45bから突出した第2の導電膜46を覆うように、第2の溝32内に設けられた第2の絶縁膜と、を有する。

(もっと読む)

61 - 80 / 523

[ Back to top ]