Fターム[5F140BK25]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース、ドレイン電極形成前の処理 (1,173) | コンタクトホールの形成 (1,071)

Fターム[5F140BK25]の下位に属するFターム

エッチング (548)

Fターム[5F140BK25]に分類される特許

41 - 60 / 523

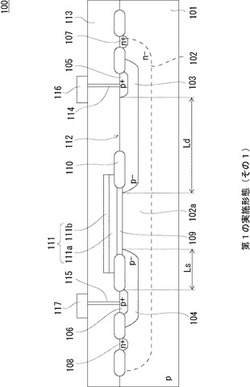

高耐圧電界効果トランジスタ

【課題】高耐圧電界効果トランジスタの素子面積を増大させること無しに、十分に低いオン抵抗を得る。

【解決手段】半導体基板101のn型領域102内に、チャネル形成領域102aを挟んでドレイン低濃度領域103およびソース低濃度領域104を形成し、ドレイン高濃度領域105およびソース高濃度領域106を形成し、ゲート酸化膜109を形成し、該ゲート酸化膜109の端部および低濃度領域103,104を含む領域にフィールド酸化膜110を形成し、さらにゲート酸化膜109からフィールド酸化膜110の端部にかけてゲート電極111を形成した高耐圧pMOSトランジスタにおいて、ゲート電極111とドレイン高濃度領域105との間に、フィールド酸化膜110が形成されていない非酸化領域112を設ける。製造時に、ドレイン低濃度領域103の不純物がフィールド酸化膜110に取り込まれ難くなるので、オン抵抗の増加が抑制される。

(もっと読む)

半導体装置及びその製造方法

【課題】低廉なプロセスにて高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の領域に形成された第1導電型の不純物層及び第1のエピタキシャル半導体層と、第1のエピタキシャル半導体層上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、第1の領域に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、第2の領域に形成された第2導電型の不純物層及び第1のエピタキシャル半導体層とは膜厚の異なる第2のエピタキシャル半導体層と、第2のエピタキシャル半導体層上に第1のゲート絶縁膜と同じ膜厚の第2のゲート絶縁膜を介して形成された第2のゲート電極と、第2の領域に形成された第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MOSトランジスタ及びp型MOSトランジスタのそれぞれに共通のゲート電極材料を用い、且つそれぞれの閾値電圧が適切な値に調整された半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1トランジスタ11及び第2トランジスタ12を備えている。第1トランジスタ11は、第1ゲート絶縁膜131と、第1ゲート電極133とを有し、第2トランジスタ12は、第2ゲート絶縁膜132と、第2ゲート電極134とを有している。第1ゲート絶縁膜131及び第2ゲート絶縁膜132は、第1絶縁層151及び第2絶縁層152を含む。第1ゲート電極133及び第2ゲート電極134は、断面凹形の第1導電層155及び該第1導電層155の上に形成された第2導電層156を含む。第1絶縁層151及び第2絶縁層152は平板状であり、第1ゲート絶縁膜131は、仕事関数調整用の第1元素を含んでいる。

(もっと読む)

半導体装置

【課題】高耐圧MOS型トランジスタなどの高耐圧半導体装置における耐圧を向上させ、またドレインオフセット層などの内部電界強度が経時的に変化し、耐圧が変動することを防止する。

【解決手段】半導体装置、例えば高耐圧MOS型トランジスタは、半導体層2、それと反対導電型の低不純物濃度ソース層3および低不純物濃度ドレイン層4、高不純物濃度ソース層5および高不純物濃度ドレイン層6、ドレイン側オフセット絶縁膜8a、ソース側オフセット絶縁膜8b、ゲート絶縁膜9、ゲート電極10を有する。ゲート電極10の表面には表面絶縁膜20が形成されており、ドレイン側オフセット絶縁膜8a上の、ゲート電極10と隣接する領域には、少なくとも一部が表面絶縁膜20と接する状態で形成された第1導電性プレート11aが設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数やコストを増加させることなく、信頼性の高い高耐圧pチャネル型トランジスタが形成された半導体装置を提供する。

【解決手段】主表面を有し、かつ内部にp型領域を有する半導体基板SUBと、p型領域PSR上であって主表面に配置された、ドレイン電極DRを取り出すための第1のp型不純物領域PRを有するp型ウェル領域PLDと、主表面に沿う方向に関してp型ウェル領域PLDと接するように配置された、ソース電極SOを取り出すための第2のp型不純物領域PRを有するn型ウェル領域NWRと、主表面に沿う方向に関して、第1のp型不純物領域PRと第2のp型不純物領域PRとの間に配置されたゲート電極GEと、n型ウェル領域NWRの上に配置された、主表面に沿って延びるp型埋め込みチャネルPPRとを含んでいる。上記n型ウェル領域NWRとp型ウェル領域PLDとの境界部は、ゲート電極GEの、第1のp型不純物領域PRに近い側の端部よりも、第1のp型不純物領域PRに近い位置に配置される。

(もっと読む)

半導体装置

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有し、第1導電型のバックゲートコンタクト領域を有さない第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】高周波特性を低下させることなくLDMOSFETを有するチップの面積を縮小する。

【解決手段】LDMOSFETのソース領域と基板1の裏面に形成されたソース裏面電極36とを電気的に接続するp型打ち抜き層4を不純物を高濃度でドープした低抵抗のp型多結晶シリコン膜もしくは低抵抗の金属膜から形成する。そして、LDMOSFETの基本セルのソース同士を電気的に接続するソース配線は配線24Aのみとし、ソース配線を形成する配線層数は、ドレイン配線(配線24B、29B、33)を形成する配線層数より少なくする。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】新規なDTMOSトランジスタの製造方法を提供する。

【解決手段】半導体装置の製造方法は、第1領域と、第1領域に接続しこれより幅狭の第2領域と、第2領域に接続しこれより幅狭の第3領域とを含む半導体領域の画定工程、半導体領域に第1導電型不純物でウェル領域を形成する工程、ウェル領域上へのゲート絶縁膜形成工程、第3領域を幅方向に横断する第1部と、第1部から第1領域上に延びた第2部とを含むゲート電極を形成する工程、ゲート電極側面に、第2領域の一部を覆い他の一部を露出させるサイドウォールを形成する工程、第1領域及び第2領域の他の一部にゲート電極及びサイドウォールをマスクとし第2導電型不純物を注入する工程、熱処理による第2導電型不純物拡散工程、サイドウォールの一部を薬液で除去する工程、第1領域及び第2領域の他の一部へのシリサイド層形成工程を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極GE2の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極GE2側に位置する側壁部において、第1の斜面と、第1の斜面と交差する第2の斜面と、を有する。このように、溝g2の形状をΣ形状とすることで、pチャネル型電界効果トランジスタのチャネル領域に加わる圧縮歪みを大きくすることができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極断線の確率を下げる。

【解決手段】半導体装置1の製造方法は、シリコン基板2の主面に絶縁体ピラー6を形成する工程と、絶縁体ピラー6の側面に保護膜12を形成する工程と、シリコン基板2の主面にシリコンピラー4を形成する工程と、シリコンピラー4の側面にゲート絶縁膜10を形成する工程と、それぞれシリコンピラー4及び絶縁体ピラー6の側面を覆い、互いに接する第1及び第2のゲート電極11,13を形成する工程とを備える。本製造方法によれば、ダミーピラーとしての絶縁体ピラー6の側面に保護膜12を形成しているので、チャネル用のシリコンピラー4をトランジスタとして加工する際にダミーピラーが削られてしまうことが防止される。したがって、ゲート電極断線の確率を下げることが可能になる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置の製造方法

【課題】希土類金属を含有するHigh-k膜のエッチング残渣を抑制するための半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に絶縁膜4を形成する工程と、絶縁膜4の上に希土類元素含有酸化膜7、12を形成する工程と、フッ酸、塩酸、硫酸を含む薬液により希土類元素含有酸化膜7、12をエッチングする工程とを有し、これにより希土類元素含有酸化膜7、12のエッチングを良好に行う。

(もっと読む)

半導体装置およびその製造方法

【課題】MOSトランジスタのソース及びドレイン電極に生じる寄生容量を低減する。高速動作が可能な半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタを備える。MOSトランジスタは、1対の第1、第2及び第3の不純物拡散領域を有する。第2の不純物拡散領域は、第1の不純物拡散領域を挟むように半導体基板内に設けられた第1導電型の不純物拡散領域であり、第1の不純物拡散領域よりも第1導電型の不純物濃度が高くなる。第3の不純物拡散領域は、1対の第1の不純物拡散領域に接すると共に第2の不純物拡散領域に接しないように、半導体基板内に設けられた第2導電型の不純物拡散領域である。

(もっと読む)

半導体装置及びその製造方法

【課題】ストレッサ膜を有する半導体装置及びその製造方法に関し、ストレッサ膜からの応力を効率よくチャネル領域に印加してMISFETの電流駆動能力を向上しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に、素子領域を画定する素子分離絶縁膜を形成し、素子領域上に、ゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板内にソース/ドレイン領域を形成し、ゲート電極及びソース/ドレイン領域が形成された半導体基板上に第1の絶縁膜を形成し、素子分離絶縁膜の端部に生じた窪み内に第1の絶縁膜が残存するように第1の絶縁膜をエッチバックし、半導体基板上に、半導体基板の表面に平行な方向に応力を印加する第2の絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】調整用金属を含む高誘電率膜を有するゲート絶縁膜を備えたMISトランジスタを有する半導体装置において、MISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、MISトランジスタnTrを備えている。MISトランジスタは、半導体基板10における素子分離領域11に囲まれた活性領域10aと、活性領域及び素子分離領域上に形成され、高誘電率膜15aを有するゲート絶縁膜16aと、ゲート絶縁膜上に形成されたゲート電極19aとを備えている。ゲート絶縁膜における素子分離領域上に位置する部分のうち、少なくとも一部分には、窒化領域20x,20yが設けられている。窒化領域20x,20yに含まれる窒素の窒素濃度をn1,n2とし、ゲート絶縁膜における活性領域上に位置する部分に含まれる窒素の窒素濃度をnとしたとき、n1>n、且つ、n2>nの関係式が成り立っている。

(もっと読む)

41 - 60 / 523

[ Back to top ]