Fターム[5F140BK29]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極の形成 (2,400) | PVD (795)

Fターム[5F140BK29]に分類される特許

201 - 220 / 795

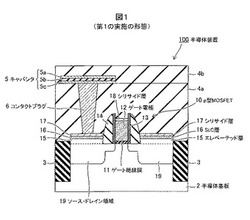

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ分離構造を有する半導体装置においてトランジスタのドレイン電流の減少などを防止する。

【解決手段】半導体基板10の主表面に活性領域11を分離するトレンチ埋込材21を備え、この埋込材の表面を、少なくとも半導体基板10に接する部分で半導体基板10の主表面より所定高さ落ち込むように形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

GaN系電界効果トランジスタ

【課題】低オン抵抗・高耐圧で動作可能なGaN系化合物半導体デバイスを提供する。

【解決手段】基板上に形成されたバッファ層、チャネル層と、前記チャネル層上に形成され、ドリフト層と、前記ドリフト層上に配置されたソース電極およびドレイン電極と、ドリフト層に形成されたリセス部の内表面および前記ドリフト層の表面に形成された絶縁膜と、前記絶縁膜上に形成されたフィールドプレート部を有するゲート電極とを備えたGaN系電界効果トランジスタにおいて、前記ドリフト層は、前記リセス部と前記ドレイン電極との間に、シートキャリア密度が5×1013cm−2以上、1×1014cm−2以下のn型GaN系化合物半導体からなる電界緩和領域を有し、前記ドリフト層の前記電界緩和領域上に形成された前記絶縁膜の厚さが300nm以上であることを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのリーク電流を防止できる電界効果型トランジスタを提供する。

【解決手段】この電界効果型トランジスタによれば、WN/Alドレイン電極109がドレイン電極109の下のn+型領域(拡散領域)112を介してGaNチャネル層104にショットキー接合されている。これにより、従来の熱処理によりドレイン電極にオーミックコンタクトを形成する場合と異なり、ドレイン電極109下へメタルが侵入することを回避できる。よって、このメタル侵入が発生するために生じるリーク電流を低減することが可能であり、電界効果型トランジスタにおける破壊電圧を向上できる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

半導体素子及びその製造方法

【課題】ソース・ドレイン電極及び/又はゲート電極の低抵抗化を図り、微細化・高集積化を損なうことなく、低消費電力で高速操作可能な半導体素子を提供する。

【解決手段】素子分離領域102によりシリコン基板101A表層に画成された素子領域に、チャネル領域を隔てて形成された一対のソース・ドレイン領域106と、ソース・ドレイン領域のそれぞれに導通するソース・ドレイン電極と、チャネル領域上にゲート絶縁膜103を介して形成されたゲート電極と、を備えた半導体素子において、ソース・ドレイン電極及び/又はゲート電極を、ソース・ドレイン領域表面又はゲートを構成するポリシリコン層表面に形成した第1金属膜がシリサイド化されてなるシリサイド層107bと、このシリサイド層上に無電解メッキ法により形成された第2金属膜108と、で構成する。

(もっと読む)

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法を提供する。

【解決手段】シリコンを含む半導体層を有する基板上または基板上に形成されたシリコンを含む導電膜上に、貴金属を含む金属膜を形成する工程(a)と、工程(a)の後、基板に対して熱処理を行って前記貴金属とシリコンとを反応させ、基板上または導電膜上に前記貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて、シリサイド膜のうち未反応の貴金属11の下に位置する部分上に酸化膜12を形成する工程(c)と、第2の薬液を用いて未反応の貴金属を溶解する工程(d)とを備える。

(もっと読む)

オーミック電極およびその形成方法

【課題】Ti3SiC2のオーミック電極層の平滑性が良好でありオーミック特性の良好なp型SiC半導体素子のオーミック電極およびその形成方法を提供する。

【解決手段】p型SiC半導体の表面にTi3SiC2のオーミック電極層が直接積層されているp型SiC半導体素子のオーミック電極、およびp型SiC半導体表面にTiとSiとCとからなる3元混合膜(原子数組成比がTi:Si:C=3:1:2である。)を積層する工程(a)と、得られた積層体を真空中又は不活性ガス雰囲気中で加熱して熱処理する工程(b)とによるp型SiC半導体表面にTi3SiC2のオーミック電極層が直接積層されているp型SiC半導体素子のオーミック電極の形成方法。

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域のエクステンション領域の不純物濃度プロファイルが急峻なp型トランジスタを有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置1aは、半導体基板2上に形成された結晶層13と、結晶層13上にゲート絶縁膜14を介して形成されたゲート電極15と、半導体基板2と結晶層13との間に形成された、ゲート電極15の下方の領域において第1の不純物を含むC含有Si系結晶からなる不純物拡散抑制層12と、半導体基板2、不純物拡散抑制層12、および結晶層13内のゲート電極15の両側に形成され、結晶層13内にエクステンション領域を有する、p導電型を有する第2の不純物を含むp型ソース・ドレイン領域17と、を有し、C含有Si系結晶は第2の不純物の拡散を抑制する機能を有し、第1の不純物は、C含有Si系結晶内の固定電荷の発生を抑制する機能を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極をシリサイド化する際にゲート長方向の体積膨張が生じにくく、ゲート電極とコンタクトプラグ等との短絡不良が生じにくい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10の上にゲート絶縁膜15を介在させて形成され、上部がシリサイド化されたゲート電極17と、ゲート電極17の側面上に形成されたオフセットスペーサ20と、オフセットスペーサ20の側面上を覆う断面L字状のサイドウォール22Aとを備えている。オフセットスペーサ20は、ゲート電極17側に形成された内側オフセットスペーサ20Aと、内側オフセットスペーサ20Aの側面上に形成された外側オフセットスペーサ20Bとを有している。内側オフセットスペーサ20Aと、外側オフセットスペーサ20B及び内側サイドウォール22Aとは、エッチング選択性が異なる材料からなる。

(もっと読む)

GaN系電界効果トランジスタおよびその製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】GaN系電界効果トランジスタ(MOSFET)100は、基板101上に、p−GaNからなるチャネル層104、電子供給層106、電子供給層よりもバンドギャップエネルギーが小さい表面層107を順次積層し、電子供給層および表面層の一部をチャネル層に到る深さまで除去してリセス部108を形成したものである。表面層上には、リセス部を挟んでソース電極109およびドレイン電極110が形成され、表面層上およびチャネル層表面を含むリセス部内表面上にゲート絶縁膜111が形成され、さらにリセス部においてゲート絶縁膜上にはゲート電極112が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】第1領域におけるライナー膜の膜厚と、第2領域におけるライナー膜の膜厚とが互いに異なる半導体装置において、コンタクトホールの形成時に、活性領域及び素子分離領域に削れが形成されることを防止する。

【解決手段】ゲート構造体Gbが密に配置された第1領域におけるライナー膜22b及び層間絶縁膜23に、互いに隣接するゲート構造体同士の間の領域を開口して、底部に第1の膜厚を有するライナー膜が残存する第1のコンタクトホール28rを形成する。次に、ゲート構造体が疎に配置された第2領域におけるライナー膜及び層間絶縁膜に、互いに隣接するゲート構造体同士の間の領域を開口して、底部に第2の膜厚を有するライナー膜が残存する第2のコンタクトホール34rを形成する。次に、第1のコンタクトホールの底部に残存するライナー膜、及び第2のコンタクトホールの底部に残存するライナー膜を除去する。第1の膜厚と第2の膜厚とは、同等である。

(もっと読む)

MISトランジスタ

【課題】ゲート電極とソース/ドレイン電極間で電気的短絡を起こし難いMISトランジスタを得る。

【解決手段】サイドウォール15を二重構造とする。バッファ層13は窒化酸化シリコンで形成され、バッファ層13の上に窒化シリコン層14が形成される。このサイドウォール15をマスクとしてシリサイド膜10を形成する。バッファ層13は窒化酸化シリコンのみならず、酸化シリコンで形成されてもよい。シリサイド膜はコバルトシリサイドでも、ニッケルシリサイドでもよい。窒化シリコン層14はバッファ層13よりも大きい応力を持つ。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とコンタクト配線のショート不良を防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板32上にゲートハードマスク、ゲート電極34及びゲート絶縁膜33を形成する。ゲートハードマスクの線幅をゲート電極よりも狭くした後、S/Dエクステンション36を形成する。全面にシリコン酸化膜を堆積形成し、エッチバックしてゲート電極の側壁から上面の一部上に渡って連続的に残存させた絶縁部材37を形成する。ゲートハードマスクを除去した後、ゲート電極と絶縁部材をマスクにしてコンタクトジャンクション38を形成する。金属シリサイド膜を形成後、シリコン窒化膜40と層間絶縁膜41を順次堆積形成する。層間絶縁膜にコンタクトホールを形成し、続いてシリコン酸化膜との選択比が高い異方性エッチングによってシリコン窒化膜を除去することでコンタクトホールを開孔し、コンタクト配線43を形成する。

(もっと読む)

半導体装置の製造方法および製造装置

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法と、それを実現する半導体装置の製造装置とを提供する。

【解決手段】半導体装置の製造方法は、半導体層を有する基板上または基板上に形成された導電膜上に、貴金属を含む合金膜を形成する工程(a)と、基板に対して熱処理を行って貴金属とシリコンとを反応させ、基板上または導電膜上に貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて未反応記合金膜を除去する工程(c)と、基板を酸化性雰囲気に曝すことによって、貴金属の残渣の下に位置する部分を含むシリサイド膜の上面上にシリコン酸化膜を形成する工程(d)と、第2の薬液を用いて貴金属の残渣を溶解する工程(e)とを備えている。

(もっと読む)

半導体装置とその製造方法

【課題】本発明は、高性能でかつ閾値電圧の低い半導体装置とその製造方法を提供することを目的とする。

【解決手段】基板に形成され、NMOSトランジスタが形成されるNMOS形成領域とPMOSトランジスタが形成されるPMOS形成領域とを絶縁分離する素子分離領域と、該基板上に形成されたHigh−k材料からなるNMOSおよびPMOSのゲート絶縁膜と、該NMOSのゲート絶縁膜上に形成されたNMOSゲート電極と、該PMOSゲート絶縁膜上に形成された第1ニッケルシリサイド層と、該第1ニッケルシリサイド層上に形成され、該第1ニッケルシリサイド層よりも厚くかつ該第1ニッケルシリサイド層よりニッケル密度が大きい第2ニッケルシリサイド層と、を有するPMOSゲート電極と、該NMOSゲート電極および該PMOSゲート電極の側壁に形成されたサイドウォールスペーサとを備える。

(もっと読む)

201 - 220 / 795

[ Back to top ]