Fターム[5F152CD14]の内容

再結晶化技術 (53,633) | 被結晶化層の下方の層 (4,095) | 材料(結晶化直前の状態) (3,330) | 絶縁体 (2,749) | SiN (830)

Fターム[5F152CD14]に分類される特許

21 - 40 / 830

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

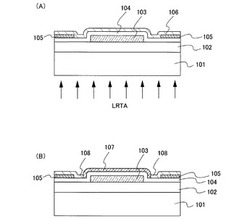

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

半導体装置

【課題】新たな構造の酸化物半導体層を用いた新たな構造の半導体装置を提供することを

目的の一とする。

【解決手段】絶縁表面を有する基板上の、第1の酸化物半導体層の表面から内部に向かっ

て成長させた結晶領域を有する第1の酸化物半導体層と、第1の酸化物半導体層上の第2

の酸化物半導体層と、第2の酸化物半導体層と接するソース電極層およびドレイン電極層

と、第2の酸化物半導体層、ソース電極層、およびドレイン電極層を覆うゲート絶縁層と

、ゲート絶縁層上の、第2の酸化物半導体層と重畳する領域のゲート電極層と、を有し、

第2の酸化物半導体層は、結晶領域から成長させた結晶を有する層である半導体装置であ

る。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

レーザ処理装置

【課題】a−Si膜をポリシリコン膜に改質するアニーリング処理等のレーザ処理を迅速化することができ、タクトタイムの短縮が可能な処理装置を提供する。

【解決手段】複数本のシリンドリカルレンズ12を有するシリンドリカルレンズアレイ2aにより、例えば8個の平板状のレーザビーム4を整形し、これを基板1上のa−Si膜に照射する。そして、基板1をこの照射領域5のギャップGで移動させて、細長い照射領域5をギャップGで基板上に形成する。このギャップGを画素ピッチとすることにより、画素領域において、画素トランジスタの形成予定領域のみを照射領域5とすることができる。

(もっと読む)

ポリシリコン活性層を含む薄膜トランジスタ及びその製造方法とアレイ基板

【課題】ポリシリコン活性層を含む薄膜トランジスタの製造方法を提供する。

【解決手段】前記製造方法は、基板にアモルファスシリコン層を堆積するとともに、前記アモルファスシリコン層に対してパターニングを行うことで、ソース領域とドレイン領域とチャンネル領域とを含む活性層を形成するステップと、前記ソース領域及び前記ドレイン領域に誘起金属を堆積するステップと、前記誘起金属が堆積された前記活性層に対して第1の熱処理を行い、前記活性層が前記誘起金属の作用によって結晶化されるステップと、前記ソース領域及び前記ドレイン領域に、前記誘起金属を集めるための第1の不純物をドープするステップと、ドープされた前記活性層に対して第2の熱処理を行い、前記第1の不純物が前記チャンネル領域に残された誘起金属に対して吸収するステップと、を備える。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

部材の作製方法

【課題】本発明の一態様は、スパッタ法でトランジスタ、ダイオード等の半導体用途に好

適な材料を提供することを課題の一とする。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面か

ら内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を

形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って

第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化

物材料の作製方法である。

(もっと読む)

酸化物半導体膜の形成方法および半導体装置の作製方法

【課題】良好な半導体特性を有する酸化物半導体膜の形成方法を提供する。さらに、該酸化物半導体膜を適用し、良好な電気特性を有する半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜を形成し、酸化物半導体膜上に接して設けられた水素透過膜を形成し、水素透過膜上に接して設けられた水素捕縛膜を形成し、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させる酸化物半導体膜の形成方法である。また、該形成方法を用いて作製する半導体装置の作製方法である。

(もっと読む)

半導体デバイス及び薄膜トランジスタ、並びに、それらの製造方法

【課題】管理コストを低減し、さらに、製造工程を削減して製造原価のコストダウンを図ることの可能な半導体デバイス及び薄膜トランジスタ、並びに、それらの製造方法の提案を目的とする。

【解決手段】所定の材料からなり、活性層41となる半導体と、所定の材料と同じ組成の材料からなり、ソース電極51、ドレイン電極53及び画素電極55の少なくとも一つとなる導電体とを備えた薄膜トランジスタ2の製造方法であって、非晶質の所定の材料からなる被処理体及び導電体(ソース電極51、ソース配線52、ドレイン電極53、ドレイン配線54及び画素電極55)を一括成膜し、さらに一括形成する工程と、形成された被処理体を結晶化させて活性層41とする工程とを有する方法としてある。

(もっと読む)

アモルファスシリコンの結晶化方法

【課題】 基板とシリコン層との間に電極形成用金属膜が設けられてなるボトムゲート型のシリコン複合体を、短時間で、クラックや反りの発生を小さく抑制しながら、アモルファスシリコンを結晶化させてシリコン層を結晶シリコンよりなるものに変質させることができるアモルファスシリコンの結晶化方法の提供。

【解決手段】 アモルファスシリコンの結晶化方法は、基板上にアモルファスシリコンによるシリコン層が形成され、当該基板とシリコン層との間に電極形成用金属膜が形成されてなるシリコン複合体を雰囲気加熱してシリコン層を結晶化度が30〜75%である結晶シリコンからなるものに変質させる予備加熱工程と、予備加熱工程を経たシリコン複合体のシリコン層に対してフラッシュランプからの光を照射して当該シリコン層を結晶化度が80%以上である結晶シリコンからなるものに変質させる光照射加熱工程とを有する。

(もっと読む)

基板上のフィルム領域を処理して、こうした領域内及びその端部領域をほぼ均一にするレーザ結晶化プロセス及びシステム、及びこうしたフィルム領域の構造

【課題】薄膜フィルム試料を処理するシステム、並びに薄膜フィルム構造を提供する。

【解決手段】フィルム試料170の一区画の特定部分の第1部分を融解させるべく照射ビームパルスの第1パルスの第1小ビームで照射して、この第1部分が少なくとも部分的に融解して自ずと再凝固して結晶化し、それぞれの隣接する第1部分どうしの間に第1未照射部分が残る。特定部分の第1小ビームによる照射の後に、この特定部分を、この特定部分の第2部分を融解させるべく照射ビームパルスの第2パルスの第2小ビームで再び照射して、この第2部分が少なくとも部分的に融解して自ずと再凝固して結晶化し、それぞれの隣接する第2部分どうしの間に第2未照射部分が残る。再凝固して結晶化した第1部分及び前記第2部分は、フィルム試料の領域内で互いに間に入り合う。これに加えて、第1部分が第1画素に対応し、第2部分が第2画素に対応する。

(もっと読む)

SOI基板、およびSOI基板の作製方法

【課題】単結晶シリコン膜などの半導体膜が、支持基板から剥がれることを防止するSOI基板の作製方法を提供する。また、当該方法を用いることで、SOI基板作製における歩留まりを向上させ、生産コストを削減する。

【解決手段】半導体基板に絶縁膜を形成し、加速されたイオンを半導体基板に照射することにより、半導体基板中に脆化領域を形成し、半導体基板と支持基板とを、絶縁膜を介して貼り合わせ、脆化領域において、半導体基板を分離して、支持基板上に絶縁膜を介して半導体膜を形成し、半導体膜上にマスクを形成し、半導体膜の一部及び絶縁膜の一部をエッチングすることにより、半導体膜の周端部が、絶縁膜の周端部の内側に位置するように、半導体膜及び絶縁膜を形成する、SOI基板の作製方法である。

(もっと読む)

レーザーアニール装置

【課題】特別な装置或いは部材を新たに設けることなく、再アニールによる基板のクラック発生を防止するレーザーアニール装置を提供する。

【解決手段】レーザーアニール装置は、基板を載置するステージと、レーザー光を発振するレーザーヘッドと、発振されたレーザー光を基板の半導体層の上面に対して概ね垂直な主光軸に沿って集光させるfθレンズとを備え、ステージには載置された基板の半導体層の平均膜厚に対して所定量だけ異なる膜厚を有して半導体層の端部に所定の幅を有して延在する領域に相当する部分に所定の断面形状を有する凹部が形成されている。

(もっと読む)

半導体装置の作製方法

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成する。

(もっと読む)

半導体装置の作製方法

【課題】 光学系を複雑化させることなく、均一なエネルギー密度のレーザ光を被照射体

に照射することができる、レーザ照射装置の提案を課題とする。

【解決手段】本発明のレーザ照射装置は、レーザ発振器と、被照射体の表面における一軸方向に、前記レーザ発振器から発振されたレーザ光によって形成されるビームスポットを繰り返し走査するための光学系と、前記表面において前記一軸方向と交差する方向に向かって、前記レーザ光に対する前記被照射体の相対的な位置を移動させるための位置制御手段とを有することを特徴とする。

(もっと読む)

SOI基板の作製方法

【課題】欠陥の少ない半導体層を得ること、及び信頼性の高い半導体装置を得る。

【解決手段】半導体基板中に、H2O+が水素イオン(H3+)に対して3%以下、好ましくは0.3%以下であるイオンビームを照射することにより、前記半導体基板中に脆化領域を形成し、前記半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、前記半導体基板及び前記ベース基板を貼り合わせ、貼り合わせた前記半導体基板及び前記ベース基板を加熱し、前記脆化領域において分離させることにより、前記ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

SOI基板の作製方法

【課題】照射された水素イオンの単結晶半導体基板からの脱離を抑制する。

【解決手段】半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

SOI基板の作製方法

【課題】膜厚の均一な半導体層を有するSOI基板を得る。

【解決手段】半導体基板の第1の面を研磨して、当該第1の面を平坦化し、当該半導体基板の当該第1の面と反対側の面である第2の面にイオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の第2の面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。当該SOI基板の作製においては、当該半導体層の膜厚の標準偏差をσとし、3σが1.5nm以下である。

(もっと読む)

21 - 40 / 830

[ Back to top ]