Fターム[5F152LL05]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 気相 (1,473) | CVD、VPE (918) | MOCVD、MOVPE (333)

Fターム[5F152LL05]に分類される特許

121 - 140 / 333

光デバイス、半導体基板、光デバイスの製造方法、および半導体基板の製造方法

【課題】高品質な光デバイスをシリコン基板上にモノリシックに形成する。

【解決手段】シリコンを含むベース基板と、ベース基板上に設けられた複数のシード結晶と、複数のシード結晶に格子整合または擬格子整合する複数の3−5族化合物半導体とを備え、複数の3−5族化合物半導体のうちの少なくとも1つに、供給される駆動電流に応じて光を出力する発光半導体、または光の照射を受けて光電流を発生する受光半導体を含む光電半導体が形成されており、複数の3−5族化合物半導体のうち、光電半導体を有する3−5族化合物半導体以外の少なくとも1つの3−5族化合物半導体にヘテロ接合トランジスタが形成されている光デバイスを提供する。

(もっと読む)

センサ、半導体基板、および半導体基板の製造方法

【課題】効率よく光電変換ができる光吸収体を有する半導体基板、半導体基板の製造方法、および当該半導体基板を含む光センサを提供する。

【解決手段】シリコンを含むベース基板と、ベース基板上方に設けられたシード体と、シード体に格子整合または擬格子整合し、光または熱を吸収してキャリアを生成する3−5族化合物半導体からなる光熱吸収体とを備え、光熱吸収体が、光熱吸収体に入射する入射光または光熱吸収体に加わる熱に応じて電気信号を出力するセンサを提供する。また、シリコンを含むベース基板と、ベース基板の上方に形成され、ベース基板の表面を露出する開口を有し、結晶成長を阻害する阻害体と、開口の内部に設けられたシード体と、シード体に格子整合または擬格子整合し、光または熱を吸収してキャリアを生成する3−5族化合物半導体からなる光熱吸収体とを備える半導体基板を提供する。

(もっと読む)

半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法

【課題】半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】シリコンに不純物原子が導入された不純物領域104を有するベース基板102と、不純物領域104に接して設けられている複数のシード体112と、複数のシード体112の各々に接して設けられ、複数のシード体112の各々とそれぞれ格子整合または擬格子整合する複数の化合物半導体114とを備える半導体基板100。当該半導体基板100は、ベース基板102上に設けられ、不純物領域104の少なくとも一部を露出する複数の開口が設けられた阻害体をさらに備えてもよい。

(もっと読む)

窒化物半導体層の剥離方法、半導体装置の製造方法、及び半導体装置

【課題】第1基板から窒化物半導体層を容易に剥離する。

【解決手段】SiC基板101の表面で単層又は複数層のグラフェン層111が成長する工程と、グラフェン層との界面で、共有結合性を有することなく、原子レベルのポテンシャルの規則性のみを用いた結合力を伴って窒化物半導体層114が形成される工程と、窒化物半導体層114とグラフェン層111aとの間、あるいはグラフェン層相互間111a,111b,111cのポテンシャルによる接合力以上の力で、窒化物半導体層がSiC基板から剥離される工程とを備える。また、剥離された窒化物半導体層が第2基板130の表面に接合される。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】同一基板に形成されるHBTとFETとの相互影響を低減する。

【解決手段】第1半導体と、第1半導体の上方に形成された第2半導体とを備え、第2半導体は、P型の伝導型を示す不純物またはN型の伝導型を示す第1不純物原子と、第2半導体が第1不純物原子を有する場合のフェルミ準位を、第2半導体が第1不純物原子を有しない場合のフェルミ準位に近づける第2不純物原子とを有する半導体基板を提供する。一例として、当該第2半導体の多数キャリアは電子であり、第2不純物原子は、第1不純物原子を有する第2半導体のフェルミ準位を下降させる。第2半導体は3−5族化合物半導体であり、第2不純物原子が、ベリリウム、ボロン、炭素、マグネシウム、および亜鉛からなる群から選択された少なくとも1つであってもよい。

(もっと読む)

半導体ウエハの製造方法及び半導体ウエハ

【課題】格子不整合系基板を使用しながら、高品質な単結晶窒化物半導体の結晶成長を実現する半導体ウエハの製造方法を提供する。

【解決手段】半導体基板101の表面にグラフェン層110を設ける工程と、グラフェン層110の炭素原子の配列を示すハニカム構造の中心に、単結晶半導体層の結晶を構成する一の元素を吸着させる工程と、この一の元素に前記結晶を構成する当該元素とは異なる他の元素を結合させ、前記結晶の第1層114を形成する工程と、前記第1層の表面にさらに所定の層数の前記結晶半導体層を結晶成長する工程を備える。

(もっと読む)

GaN単結晶体およびその製造方法、ならびに半導体デバイスおよびその製造方法

【課題】GaN単結晶体を成長させる際および成長させたGaN単結晶体を基板状などに加工する際、ならびに基板状のGaN単結晶体上に少なくとも1層の半導体層を形成して半導体デバイスを製造する際に、クラックの発生が抑制されるGaN単結晶体およびその製造方法ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本GaN単結晶体10は、ウルツ型結晶構造を有し、30℃において、弾性定数C11が348GPa以上365GPa以下かつ弾性定数C13が90GPa以上98GPa以下、または、弾性定数C11が352GPa以上362GPa以下である。

(もっと読む)

基板生産物の製造方法、基板生産物、及び半導体デバイス

【課題】異種基板と貼り合わせた窒化物系化合物半導体基板の一部を異種基板から除去することにより窒化物系化合物半導体層を異種基板上に製造する方法において、窒化物系化合物半導体層におけるリーク電流を低減する。

【解決手段】シリコン基板等の支持基板20上に窒化ガリウム層30を有する基板生産物1を製造する方法であって、窒化ガリウム基板10の表面10aにイオン注入を行う工程と、表面10aを洗浄する工程と、表面10aと支持基板20の表面20aとを互いに接合させる工程と、窒化ガリウム基板10のうち表面10aを含む部分を層状に残して他の部分を除去することにより、窒化ガリウム層30を支持基板20上に形成する工程とを含む。表面10aを洗浄する工程の際、洗浄後の表面10aにおけるFe,Cr,Ni,及びSiの密度を合計で1×1018[cm−3]以下とする。

(もっと読む)

異種基板、それを利用した窒化物系半導体素子及びその製造方法

本発明は、異種基板と、それを利用した窒化物系半導体素子及びその製造方法に関し、異種基板の無極性または半極性面に結晶成長モードを調節し、高品質の無極性または半極性窒化物層を形成するためのものである。無極性または半極性面のうち1つを有するベース基板を準備し、用意したベース基板の面に窒化物系結晶成長核層を形成する。結晶成長核層の上に第1バッファー層を成長させ、且つ、水平方向に比べて垂直方向にさらに速く成長させる。第1バッファー層上に水平成長層を成長させ、且つ、垂直方向に比べて水平方向にさらに速く成長させる。また、水平成長層上に第2バッファー層を成長させる。この際、第1バッファー層上の水平成長層と第2バッファー層との間に複数の孔を有する窒化シリコン層をさらに形成することができる。  (もっと読む)

(もっと読む)

III族窒化物半導体成長用基板、III族窒化物半導体エピタキシャル基板、III族窒化物半導体素子およびIII族窒化物半導体自立基板、ならびに、これらの製造方法

【課題】成長温度が1050℃以下のAlGaNやGaNやGaInNだけでなく、成長温度が高い高Al組成のAlxGa1-xNにおいても結晶性の良いIII族窒化物半導体エピタキシャル基板、III族窒化物半導体素子、III族窒化物半導体自立基板およびこれらを製造するためのIII族窒化物半導体成長用基板、ならびに、これらを効率よく製造する方法を提供する。

【解決手段】少なくとも表面部分がAlを含むIII族窒化物半導体からなる結晶成長基板と、前記表面部分上に形成されたスカンジウム窒化物膜とを具えることを特徴とする。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】熱を効率的に外部に放出することができるとともに、製造コストを抑えることができる半導体デバイスおよび半導体デバイスの製造方法を提供する。

【解決手段】半導体層と、半導体層上に設置されたヒートシンクとを備え、ヒートシンクは、高熱伝導率層と低熱膨張率層と高熱伝導率層とがこの順序で積層された積層構造体、または低熱膨張率層と高熱伝導率層と低熱膨張率層とがこの順序で積層された積層構造体を含み、積層構造体の厚み方向の中央部から上方の部分と積層構造体の厚み方向の中央部から下方の部分とが積層構造体の厚み方向の中央部に関して対称となっている半導体デバイスとその製造方法である。

(もっと読む)

III族窒化物半導体層貼り合わせ基板およびその製造方法、ならびにIII族窒化物半導体デバイス

【課題】光の取り出し効率が高い半導体デバイスが得られる安価なIII族窒化物半導体層貼り合わせ基板およびその製造方法ならびにIII族窒化物半導体デバイスを提供する。

【解決手段】本III族窒化物半導体層貼り合わせ基板1は、III族窒化物半導体層20aと、III族窒化物半導体層20aと化学組成が異なる基礎基板10と、が貼り合わせられた基板であって、III族窒化物半導体層20aは、基礎基板10と接合する主面20nを有し主面20nに平行な2次元方向に屈折率が周期的に変化するフォトニック結晶構造層20pを含む。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】単一半導体基板上にHBTおよびFETのような複数異なる種類のデバイスを形成するに適した半導体基板を製造する方法を提供する。

【解決手段】半導体を結晶成長させる反応容器内に第1不純物原子を構成要素として有する単体または化合物を含む第1不純物ガスを導入する段階を含む複数の段階を繰り返して、複数の半導体基板を製造する方法であって、第1不純物ガスを導入する段階の後に、製造された半導体基板を取り出す段階と、反応容器内に第1半導体を設置する段階と、反応容器内に、第1半導体内で第1不純物原子と反対の伝導型を示す第2不純物原子を構成要素として有する単体または化合物を含む第2不純物ガスを導入する段階と、第1半導体を第2不純物ガスの雰囲気中で加熱する段階と、加熱した前記第1半導体上に第2半導体を結晶成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置

【課題】低コストの立方晶炭化ケイ素(3C−SiC)単結晶薄膜を得るための立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置を提供する。

【解決手段】立方晶炭化ケイ素単結晶薄膜の製造方法において、基板101の表面に犠牲層102を形成する第1の工程と、犠牲層の表面に少なくとも表面層が立方晶構造である立方晶半導体層103を形成する第2の工程と、立方晶半導体層の表面に立方晶炭化ケイ素単結晶層104を形成する第3の工程と、犠牲層をエッチング除去して、立方晶半導体層と立方晶炭化ケイ素単結晶層との積層体を剥離する第4の工程とを備える。

(もっと読む)

基板から分離された窒化ガリウムの膜をエピタキシーにより製造する方法

【課題】本発明は、欠陥密度レベルの減少した、エピタキシーによる窒化ガリウム膜の製造に関する。それは、GaNのエピタキシャル付着により窒化ガリウム(GaN)膜を製造するための方法に関する。

【解決手段】本発明は、それが少なくとも1ステップのエピタキシャル横方向成長を含んでなり、それがGaN基板への直接的イオン注入による脆化でその基板からGaN層の一部を分離させるステップを含んでなることで特徴付けられる。本発明は、上記方法で得られる膜、並びに該窒化ガリウム膜を備えた光電子および電子部品にも関する。

(もっと読む)

III族窒化物半導体成長用基板、III族窒化物半導体エピタキシャル基板、III族窒化物半導体素子およびIII族窒化物半導体自立基板、ならびに、これらの製造方法

【課題】成長温度が1050℃以下のAlGaNやGaNやGaInNだけでなく、成長温度が高い高Al組成のAlxGa1-xNにおいても結晶性の良いIII族窒化物半導体エピタキシャル基板、III族窒化物半導体素子、III族窒化物半導体自立基板およびこれらを製造するためのIII族窒化物半導体成長用基板、ならびに、これらを効率よく製造する方法を提供する。

【解決手段】少なくとも表面部分がAlを含むIII族窒化物半導体からなる結晶成長基板と、前記表面部分上に形成されたスカンジウム窒化物膜とを具えることを特徴とする。

(もっと読む)

発光サイリスタ、発光素子アレイ、発光装置および画像形成装置

【課題】 ベース層のキャリア濃度および厚み寸法を大きく設定することなく、発光強度に対する電流増幅率βの影響を抑制することのできる発光サイリスタ、発光素子アレイ、発光装置および画像形成装置を提供することである。

【解決手段】 発光サイリスタは、基板上に第1半導体層、第1半導体層と反対導電型の第2半導体層、第1半導体層と同じ導電型の第3半導体層、および第1半導体層と反対導電型の第4半導体層がこの順に積層されており、第3半導体層のバンドギャップは、第2半導体層のバンドギャップと略同一、かつ、第1および第4半導体層のバンドギャップより狭幅であり、第3半導体層は、基板側の第1領域と基板と反対側の第2領域とからなり、かつ、第1領域の不純物濃度は1×1016(cm−3)未満である。

(もっと読む)

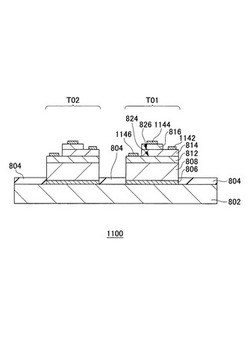

半導体基板、半導体基板の製造方法、電子デバイス、および電子デバイスの製造方法

【課題】結晶薄膜を有する半導体基板の設計および上記結晶薄膜の膜質および膜厚の制御を容易にできる半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に、一体にまたは分離して設けられ、化合物半導体の結晶成長を阻害する阻害層とを備え、阻害層は、ベース基板まで阻害層を貫通する複数の開口を有する複数の第1開口領域を有し、複数の第1開口領域のそれぞれは、内部に同一の配置で設けられた複数の第1開口を含み、複数の第1開口の一部は、電子素子が形成されるべき第1化合物半導体が設けられている第1素子形成開口であり、複数の第1開口の他の一部は、電子素子が形成されない第1ダミー開口である半導体基板を提供する。

(もっと読む)

半導体素子

【課題】バッファ層を介した電極間のリーク電流を抑制した半導体素子を提供する。

【解決手段】本半導体素子は、基板10に形成された第1のAlXGa1−XN層14a及び第1のAlXGa1−XN層14aよりAl組成Xの大きい第2のAlXGa1−XN層14bが交互に積層して形成された超格子バッファ層14を有する。そして、第1のAlXGa1−XN層14a及び第2のAlXGa1−XN層14bのAl組成Xは共に0.3より大きく、かつ第1のAlXGa1−XN層14a及び第2のAlXGa1−XN層14bのAl組成Xの差は0より大きく0.6より小さい。この構成によれば、バッファ層を介したリーク電流を低減することができる。

(もっと読む)

貼り合わせ基板の製造方法

【課題】接合強度を十分に維持できると共に、短時間で分離することができる、貼り合わせ基板の製造方法を提供する。

【解決手段】この貼り合わせ基板の製造方法は、III族窒化物半導体基板及び第1支持基板のうち少なくとも一方上に、表面粗さRrmsが0.1〜10000nmの表面を有する第1緩衝膜を形成する工程と、第1緩衝膜を介して、第1支持基板にIII族窒化物半導体基板を貼り合わせる工程とを含む。

(もっと読む)

121 - 140 / 333

[ Back to top ]