Fターム[5F152MM04]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,408) | 電子素子 (1,201) | トランジスタ (962) | MOSFET (619)

Fターム[5F152MM04]に分類される特許

41 - 60 / 619

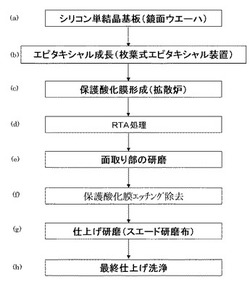

エピタキシャルウェーハの製造方法

【課題】エピタキシャル層表面の付着パーテイクルが少なく、平滑な面取り部の形状を持ち、かつ酸素析出特性にも優れた、先端CMOSに好適なエピタキシャルウェーハを、安定的にかつ低コストで製造することができる方法を提供することを目的とする。

【解決手段】シリコン単結晶基板上にエピタキシャル層を成長させることによりエピタキシャルウェーハを製造する方法において、前記シリコン単結晶基板上に、エピタキシャル層を成長させる工程と、該エピタキシャル層を成長させたシリコン単結晶基板を、650〜800℃の温度で1時間以上保持した後に850℃以上の温度に昇温して、前記エピタキシャル層の表面に保護酸化膜を形成する工程と、該保護酸化膜を形成したシリコン単結晶基板の面取り部を研磨する工程と、その後、前記保護酸化膜を除去して、仕上げ洗浄を行う工程とを含むエピタキシャルウェーハの製造方法。

(もっと読む)

真性半導体層を備えたウェーハ

【課題】ウェーハを製造するための新規な方法を提供する。

【解決手段】本発明は、ウェーハを製造するための方法に関し、この方法は、半導体基板上にドープト層を設けるステップと、ドープト層上に第1の半導体層を設けるステップと、第1の半導体層上に埋込み酸化物層を設けるステップと、埋込み酸化物層上に第2の半導体層を設けるステップと、を備える。

(もっと読む)

歪吸収中間層遷移モジュールを有するIII族窒化物半導体構造

【課題】歪み吸収III族窒化物中間層モジュールを有する種々の半導体構造を提供する。

【解決手段】基板および当該基板の上方の第一遷移本体を有する。前記第一遷移本体は、第一表面において第一の格子パラメータを有し、前記第一表面とは反対側の第二表面において第二の格子パラメータを有する。前記典型的な実施では、遷移モジュール等の第二遷移本体をさらに有し、この第二遷移本体は前記第一遷移本体の前記第二表面に重層する下表面においてより小さい格子パラメータを有し、前記第二遷移本体の上表面においてより大きい格子パラメータを有し、前記第二遷移本体の上方のIII族窒化物半導体層も同様である。前記第二遷移本体は2以上の遷移モジュールからなっていてもよく、各遷移モジュールは2以上の中間層を有していてもよい。前記第一遷移本体および前記第二遷移本体は前記半導体構造の歪みを減少させる。

(もっと読む)

SOI基板、およびSOI基板の作製方法

【課題】単結晶シリコン膜などの半導体膜が、支持基板から剥がれることを防止するSOI基板の作製方法を提供する。また、当該方法を用いることで、SOI基板作製における歩留まりを向上させ、生産コストを削減する。

【解決手段】半導体基板に絶縁膜を形成し、加速されたイオンを半導体基板に照射することにより、半導体基板中に脆化領域を形成し、半導体基板と支持基板とを、絶縁膜を介して貼り合わせ、脆化領域において、半導体基板を分離して、支持基板上に絶縁膜を介して半導体膜を形成し、半導体膜上にマスクを形成し、半導体膜の一部及び絶縁膜の一部をエッチングすることにより、半導体膜の周端部が、絶縁膜の周端部の内側に位置するように、半導体膜及び絶縁膜を形成する、SOI基板の作製方法である。

(もっと読む)

半導体装置

【課題】トランジスタ領域におけるゲート間距離などのレイアウトに依存することなく、半導体層のチャネル領域に有効に応力を作用させることができる半導体装置を実現する。

【解決手段】MOSトランジスタを備える半導体装置の構成として、素子分離層4で素子分離されたトランジスタ領域を有する半導体層3と、トランジスタ領域で半導体層3の第1の面上にゲート絶縁膜5を介して形成されたゲート電極6と、トランジスタ領域で半導体層3の第1の面と反対側の第2の面上に形成された応力膜31とを備え、応力膜31は、シリサイド膜を用いて形成されている。

【選択図】図13  (もっと読む)

(もっと読む)

トレンチ埋め込みエピタキシャル成長条件の最適化方法

【課題】トレンチ埋め込みエピタキシャル成長の制御パラメータを変更した際にエピタキシャルの成長反応の変化傾向を簡便に知ることができ、結果として、最適な成長条件を簡便に見つけ出すことが可能な、トレンチ埋め込みエピタキシャル成長条件の最適化方法を提供する。

【解決手段】シリコンソースガスにエッチングガスを混合した混合ガスを原料ガスとし、この原料ガスをH2キャリアガスで流通させることにより、シリコン基板表面に形成したトレンチ内部にエピタキシャル層を成長させてトレンチ内部をエピタキシャル層で埋め込む工程を含む半導体基板の製造方法における、トレンチ内部をエピタキシャル層で埋め込む際のエピタキシャル成長の最適条件を求める方法であって、ある特定のアスペクト比のトレンチ内部を埋め込む際のエピタキシャル成長の最適条件をエピタキシャル成長速度のH2キャリアガスの流量依存性により求めることを特徴とする。

(もっと読む)

半導体基板、半導体装置、および半導体基板の製造方法

【課題】GaN系半導体は、面方位が(111)のシリコン基板上にエピタキシャル成長される。GaNの格子定数と、とシリコン(111)面の格子定数の差が、約17%と大きいのでめ、成長されたGaNには1010cm−2を超える転位が導入される。転位により、GaNを用いたトランジスタのリーク電流が増大する。また、トランジスタの移動度が低下する。

【解決手段】シリコン基板と、シリコン基板の(150)面上に、エピタキシャル成長された窒化物半導体層と、を備える半導体基板を提供する。

(もっと読む)

SOI基板の作製方法

【課題】欠陥の少ない半導体層を得ること、及び信頼性の高い半導体装置を得る。

【解決手段】半導体基板中に、H2O+が水素イオン(H3+)に対して3%以下、好ましくは0.3%以下であるイオンビームを照射することにより、前記半導体基板中に脆化領域を形成し、前記半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、前記半導体基板及び前記ベース基板を貼り合わせ、貼り合わせた前記半導体基板及び前記ベース基板を加熱し、前記脆化領域において分離させることにより、前記ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

SOI基板の作製方法

【課題】照射された水素イオンの単結晶半導体基板からの脱離を抑制する。

【解決手段】半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

SOI基板の作製方法

【課題】膜厚の均一な半導体層を有するSOI基板を得る。

【解決手段】半導体基板の第1の面を研磨して、当該第1の面を平坦化し、当該半導体基板の当該第1の面と反対側の面である第2の面にイオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の第2の面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。当該SOI基板の作製においては、当該半導体層の膜厚の標準偏差をσとし、3σが1.5nm以下である。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

炭化珪素半導体基板、炭化珪素半導体装置、炭化珪素半導体基板の製造方法および炭化珪素半導体装置の製造方法

【課題】縦型の半導体素子の形成が可能で、かつ高品質な単結晶SiC基板の使用量を減らすことが可能であるSiC半導体基板を提供する。

【解決手段】支持基板1と、支持基板1の表面に接合されることにより支持基板1と一体化された単結晶SiC層2と、を有するSiC半導体基板において、支持基板1を、単結晶SiCより比抵抗が低い材料を用いて構成された基板1aと、当該基板1aを被覆するSiC組成薄膜1bとを備えたものとする。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製

方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を

有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけら

れた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとし

て機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向

に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向

と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面

を有するディスプレイを実現するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して貼り合わせられ、島状に絶縁分離されたGe層8(第2の半導体層)が設けられ、このGe層8に高濃度のソースドレイン領域(14、15)が形成されたPチャネルのMISFETと、Si基板1上にシリコン窒化膜2及び一部に空孔5を有するシリコン酸化膜3を介して、空孔5直上の歪みSi層7を挟み、左右にSiGe層6を有する構造からなるエピタキシャル半導体層(第1の半導体層)が島状に絶縁分離されて設けられ、歪みSi層7には概略チャネル領域が形成され、SiGe層6には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成されたNチャネルのMISFETとから構成したCMOS。

(もっと読む)

裏面照射型固体撮像素子用エピタキシャル基板およびその製造方法

【課題】裏面照射型固体撮像素子をより高い歩留まりで製造することが可能なエピタキシャル基板およびその製造方法を提供する

【解決手段】本発明の裏面照射型固体撮像素子用エピタキシャル基板100は、炭素、または、炭素および窒素が添加され、抵抗率が100Ω・cm未満であるp型シリコン基板1と、該p型シリコン基板上のp型第1エピタキシャル層2と、該第1エピタキシャル層上のp型またはn型第2エピタキシャル層3と、を有し、前記第1エピタキシャル層2は、p型不純物のピーク濃度が2.7×1017atoms/cm3以上1.1×1019atoms/cm3未満であることを特徴とする。

(もっと読む)

発光装置の作製方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。

【解決手段】基板上に金属層を形成する工程と、前記金属層上に酸化物層を形成する工程と、前記酸化物層上に絶縁層を形成する工程と、前記絶縁層上に薄膜トランジスタを形成する工程と、前記薄膜トランジスタ上に発光素子を形成する工程と、人間の手又は前記薄膜トランジスタを引き剥がす装置を用いることにより、前記酸化物層の層内または界面において前記基板から前記薄膜トランジスタを剥離する工程とを有する。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

MOSゲート型炭化珪素半導体装置の製造方法

【目的】チャネル移動度を大きくし、チャネル抵抗を低減できるMOSゲート型炭化珪素半導体装置の提供。

【構成】トレンチの側壁に接するゲート酸化膜とチャネル反転層表面との間に他導電型シリコン半導体層が形成されるMOSゲート型炭化珪素半導体装置であって、他導電型シリコン半導体層がアモルファスシリコン層で形成し、レーザー光を前記アモルファスシリコン層に対して前記MOSゲート型炭化珪素半導体装置のチャネル電流が流れる方向と交差しない方向へスキャンしてアモルファスシリコン層をポリシリコンに変換する。

(もっと読む)

半導体基板の製造方法

【課題】表面保護膜の剥離ムラやウォーターマークの発生、及びSi基板への不純物吸着等の問題を抑制することにより、固体撮像装置を作製した場合に暗電流の白傷欠陥の発生を効果的に防止可能なエピタキシャル基板の製造方法を提供する。

【解決手段】SiからなるCZ基板11上に、アクリル樹脂をベースポリマーとする有機膜12を形成する。有機膜12を介してCZ基板11に炭素イオンを注入し、CZ基板11中に炭素注入領域13を形成する。その後、有機膜12を比較的強い酸化剤であるSPM(硫酸過酸化水素水)の溶液によるウェットエッチング、若しくは水素ガスを用いたドライエッチングで洗浄して除去する。その後はCZ基板11の表面にSi材料を用いてSiエピタキシャル層14を形成し、エピタキシャル基板を得る。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】 水分に起因するTFT特性の変化を抑制した薄膜トランジスタおよびその製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタは、基板上に、少なくともゲート電極、ゲート絶縁膜、活性層、ソース電極、およびドレイン電極が設けられ、活性層上にソース電極およびドレイン電極が設けられたものである。活性層は、アモルファス酸化物半導体により構成されており、ゲート絶縁膜内に存在する第1の水分量が活性層に存在する第2の水分量よりも少ない。

(もっと読む)

41 - 60 / 619

[ Back to top ]