Fターム[5F152MM04]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,408) | 電子素子 (1,201) | トランジスタ (962) | MOSFET (619)

Fターム[5F152MM04]に分類される特許

101 - 120 / 619

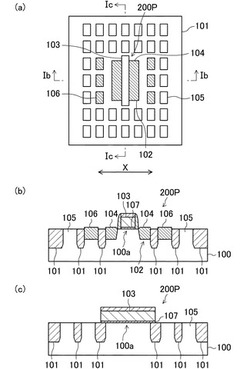

半導体装置

【課題】Si混晶層における選択成長用マスクの開口率の違いによりエピタキシャル成長が不均一となることを防止すると共に、半導体素子のキャリア移動度を向上できるようにする。

【解決手段】半導体装置は、半導体基板100の上部に形成された素子分離膜101と、素子分離膜に囲まれてなる素子活性領域102と、該素子活性領域102に形成され正孔をキャリアとするチャンネル領域100aとを有するP型MIS−FET200Pと、素子分離膜における素子活性領域102の周辺部に形成された複数のダミー活性領域105とを備えている。複数のダミー活性領域105のうち、正孔の移動方向と対向する位置に形成されたダミー活性領域のみをシリコンとゲルマニウムとを含むSiGe付きダミー活性領域106としている。

(もっと読む)

半導体素子、および半導体素子の製造方法

【課題】高移動度と高耐圧を両立し、かつ大電流動作が可能なIII族窒化物半導体を用い

た半導体素子を提供する。

【解決手段】半導体素子は、III族窒化物系化合物半導体からなり、シートキャリア密度

が、1×1012cm−2以上5×1013cm−2以下である半導体動作層と、前記半

導体動作層上に形成された第1の電極及び第2の電極とを備え、前記半導体動作層におけ

る転位密度が1×108cm−2以上、5×108cm−2以下であることを特徴とする

。

(もっと読む)

エピタキシャルウェーハ製造方法

【課題】エピタキシャルウェーハにミスフィット転位が発生するか否かを適切に判断できるエピタキシャルウェーハの製造方法を提供する。

【解決手段】ウェーハの抵抗率及び成長させるエピタキシャル層の厚さと、ミスフィット転位の発生有無との関係を特定し、所望する抵抗率及びエピタキシャル層の厚さの指定を受け付け(ステップS1)、ミスフィット転位が発生するか否かを判定し(ステップS2)、発生すると判定した場合に、ゲルマニウムと赤燐をドープすることにより所望の抵抗率となるウェーハのためのシリコンインゴットを生成し(ステップS4)、ウェーハを切り出し(ステップS7)、受け付けたエピタキシャル層の厚さ以下のエピタキシャル層を形成する(ステップS9)。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体装置の製造方法

【課題】特性を十分に向上することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、SiC膜11を形成する工程と、このSiC膜11の表面にSiを供給した状態で、このSiC膜11を熱処理する熱処理工程と、熱処理工程によってSiC膜11の表面に得られたファセットをチャネル16とする工程とを備えている。このようにすれば、Siを供給した状態でSiC膜11を熱処理することにより、SiC膜11をエネルギ的に安定な表面状態に再構成させることができる。その結果、一周期が100nm以上のファセットが得られ、ファセットの平坦部分の長さを従来に比べて長くすることができる。したがって、界面準位の密度を減少することによりキャリアの移動度を向上することができ、半導体装置の特性を十分に向上することができる。

(もっと読む)

半導体基板の製造方法および半導体デバイスの製造方法

【課題】シリコンデバイス等耐熱性の低い部位がSi基板に設けられた場合でも、Ge結晶に熱アニールを施し、十分な結晶品質のGe結晶薄膜を得る。

【解決手段】表面がSiであるベース基板と、前記ベース基板の上に形成され、組成がCxSiyGezSn1−x−y―z(0≦x<1、0≦y<1、0<z≦1、かつ、0<x+y+z≦1)である第1結晶層と、前記第1結晶層が形成された部分以外の前記ベース基板の上に形成された第1半導体素子と、を有する半導体基板の製造方法であって、前記第1半導体素子には電磁波を照射することがなく、前記第1結晶層の一部または全部に電磁波を照射する工程を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】格子定数が異なる複数種類の半導体素子やスピン機能素子を同一の基板上の同一の層上に混載することが可能な半導体装置の製造方法を提供しようとする。

【解決手段】シリコン基板上に絶縁膜を形成する工程と、前記絶縁膜に開口部を設け、前記シリコン基板の一部を露出させる工程と、前記露出したシリコン基板及び前記絶縁膜上にGeを含むアモルファスの第1の半導体層を形成する工程と、前記第1の半導体層を第1の方向に延伸した構造に加工する工程と、前記第1の方向に延伸した第1の半導体層に熱処理を加えて、前記開口部から離れるにしたがってSiの濃度が減少する第1のSi1-xGex(0≦x≦1)層を形成する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】基板の材質に関係なく半導体回路部分への高熱処理が可能な半導体装置の製造方法を提供する。

【解決手段】樹脂基板2上にシリコーン樹脂で密度が0.7g/cm3以下の多孔質構造体層4を設ける。ここでシリコーン樹脂は95質量%以上がシルセスキオキサンまたはシロキサンからなり、シルセスキオキサンはメチルシルセスキオキサンまたはフェニルシルセスキオキサンであることが好ましい。この多孔質構造体層上に半導体素子層3を設け、この半導体素子層側からのみ間欠的に光または電子線により加熱する。

(もっと読む)

半導体素子の製造方法

【課題】ピッティング不良が抑制され、簡単な工程を通じて形成することができる高性能の半導体素子の製造方法を提供する。

【解決手段】半導体基板にゲート電極を形成する段階と、ゲート電極に側壁スペーサを形成する段階と、側壁スペーサの両側の半導体基板を一部エッチングしてトレンチを形成する段階と、トレンチ内にSiGe混晶層を形成する段階と、SiGe混晶層上にシリコン層を形成する段階と、シリコン層の面の結晶方向に従って、エッチング率が異なるエッチング液を利用してシリコン層の一部をエッチチングすることによって111傾斜面を有するシリコンファセット(Si facet)を含むキャッピング層を形成する段階と、を有する。キャッピング層を含むことによって半導体素子でホールの移動度が高まる。キャッピング層内のピッティング不良が減少することによって半導体素子の特性が良好になる。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加しつつ、基板やソース/ドレイン領域においてリーク電流の発生が効果的に抑制された半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の不純物を含み、素子形成領域170を有する半導体基板101と、素子形成領域170上にゲート絶縁膜132を挟んで形成されたゲート電極125と、ゲート電極125の両側方に形成され、第2導電型の不純物を含むソース/ドレイン領域150とを備える。素子形成領域170のうちゲート電極の両側方に位置する領域には、半導体基板101の主面に対して傾いた半導体単結晶のファセット面を露出させる側壁を有し、コーナー部が丸められたリセス130が形成されており、ソース/ドレイン領域150は、リセス130に埋め込まれたシリコン混晶で構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】上部拡散層上にコンタクトパッドを別途形成することなく、コンタクト合わせマージンを向上させる縦型トランジスタ構造を提供する。

【解決手段】本発明の半導体装置は、基板上に、柱状の半導体からなるボディ部(5)と、ボディ部の側面にゲート絶縁膜(10)を介して設けられるゲート電極(11)と、ボディ部の下部に接続される第1の拡散層(9)と、ボディ部の上面に接続される第2の拡散層(16)とを備える縦構造トランジスタを含む半導体装置であって、第2の拡散層(16)は、ボディ部の上面の面積以下の基板平面方向の断面を有する第1部分(14)と、第1部分の上部にボディ部の上面の面積以上の基板平面方向の断面を有する第2部分(15)とを備え、少なくとも第2部分がエピタキシャル成長層であり、隣接する縦型トランジスタ間に第2部分が接触することを防止する絶縁膜(17)を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域の寄生抵抗の上昇を抑えつつ短チャネル効果の発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2中のゲート電極12の両側に形成され、ゲート電極12側にエクステンション領域161を有し、導電型不純物を含むソース・ドレイン領域16と、ソース・ドレイン領域16のエクステンション領域161のゲート電極12側の側面のみに接し、導電型不純物の半導体基板2中での拡散を抑制する性質を有する拡散抑制不純物を含む拡散抑制層15と、を有する。

(もっと読む)

半導体素子の製造方法

【課題】第1導電型半導体層にトレンチを形成し、その中に第2導電型半導体層をエピタキシャル成長させて並列pn接合構造を形成する際に、MOSFET等の形成時に利用されるマスク合わせ用のアライメントマークを形成すること。

【解決手段】n型半導体層12に第1のアライメントマーク1を形成し、その上全面にトレンチパターンを有する絶縁膜13を形成する。絶縁膜13をマスクとしてトレンチ2を形成し、p型半導体層14をエピタキシャル成長させる。絶縁膜13を研磨ストッパとしてp型半導体層14を研磨した後、残った絶縁膜13をマスクとしてエッチングを行い、p型半導体層14の上端面を後退させる。表面に残った絶縁膜13を除去する。表面に絶縁膜21を形成し、絶縁膜21の一部を除去してマスクとし、第2のアライメントマーク3を形成する。絶縁膜21を除去した後、半導体表面を鏡面状に研磨する。

(もっと読む)

共通基板上にカラムIII−VトランジスタとともにシリコンCMOSトランジスタを有する半導体構造

半導体構造は、ある結晶方位を有するシリコン基板(12)と、シリコン基板(12)の上方に配置された絶縁性層(18/22)と、絶縁性層の上方に配置され、基板の結晶方位とは異なる結晶方位を有するシリコン層(20)と、シリコン基板上に配置され、基板と同じ結晶方位を有するカラムIII−Vトランジスタデバイス(34)とを有する。一実施形態では、カラムIII−Vトランジスタデバイスが、基板と接触する。別の実施形態では、デバイスは、GaNデバイスである、または基板の結晶方位が<111>であり、シリコン層の結晶方位が<100>である。一実施形態では、CMOSトランジスタが、シリコン層内に配置される。一実施形態では、カラムIII−Vトランジスタデバイスが、カラムIII−Nデバイスである。一実施形態では、カラムIII−Asデバイス、カラムIII−Pデバイス、またはカラムIII−Sbデバイスが、<100>シリコン層の上面上に配置される。  (もっと読む)

(もっと読む)

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】単一のシリコン基板上に種類の異なる半導体結晶層をエピタキシャル成長させる場合に、表面の平坦性を向上し、半導体デバイスの信頼性を高める。

【解決手段】第1窪みおよび第2窪みが形成されたシリコン結晶を表面に有するベース基板と、第1窪みの内部に形成され、露出されている第1のIVB族半導体結晶と、第2窪みの内部に形成された第2のIVB族半導体結晶と、第2窪みの内部の第2のIVB族半導体結晶上に形成され、露出されているIII−V族化合物半導体結晶とを備える半導体基板を提供する。

(もっと読む)

単結晶ゲルマニウムまたはシリコンゲルマニウムを形成する方法

【課題】基板中に形成されたトレンチ中に、単結晶のゲルマニウムまたはシリコンゲルマニウムを形成する改良された方法を提供する。

【解決手段】誘電体分離3(例えばSTI)を有する基板1を準備する工程と、基板材料1(例えばSi)のトレンチエッチング4を行う工程と、トレンチ4内への充填層5(例えばGe)の選択成長を行う工程と、略溶融温度での充填層6の加熱により、充填層5(例えばGe)の再結晶化7により達成される。

(もっと読む)

CMOS用歪トランジスタの集積化

【課題】n型MOSデバイス(NMOS)の電子の移動度の向上、およびp型MOSデバイス(PMOS)のホールの移動度の向上した半導体装置および製造方法の提供。

【解決手段】(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

半導体装置

【課題】様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】強磁性材料からなるシートを支持体とし、前記強磁性材料からなるシートに接する接着材と、該接着材に接する絶縁膜上に素子とを備える。上記構成において、前記素子は、薄膜トランジスタ、有機化合物を含む層を有する発光素子、液晶を有する素子、メモリー素子、薄膜ダイオード、シリコンのPIN接合からなる光電変換素子、またはシリコン抵抗素子であってもよい。また、上記各構成において、前記強磁性材料からなるシートは、軟質磁性粉体と合成樹脂とを混合して形成され、着磁されたものであってもよい。

(もっと読む)

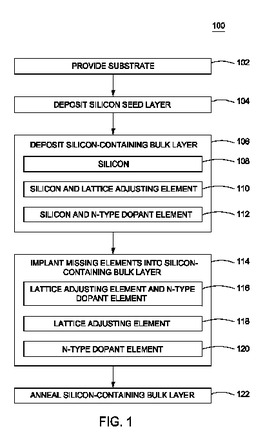

NMOSエピ層の形成方法

制御されたチャネル歪みおよび接合抵抗を有するNMOSトランジスタ、およびその製造方法が、本明細書で提供される。いくつかの実施形態において、NMOSトランジスタを形成するための方法は、(a)p型シリコン区域を有する基板を準備すること、(b)p型シリコン区域の上にシリコンシード層を堆積すること、(c)シリコン、シリコンおよび格子調整元素またはシリコンおよびn型ドーパントを備えるシリコン含有バルク層をシリコンシード層の上に堆積すること、(d)(c)で堆積されたシリコン含有バルク層に欠けている格子調整元素またはn型ドーパントのうちの少なくとも1つをシリコン含有バルク層の中に注入すること、(e)(d)の注入の後、シリコン含有バルク層をエネルギービームを用いてアニールすることを含むことができる。いくつかの実施形態において、基板は、その中に画定されたソース/ドレイン区域を有する、部分的に製造されたNMOSトランジスタデバイスを備えることができる。  (もっと読む)

(もっと読む)

SOI基板の作製方法

【課題】低温での固相エピタキシャル成長法を用いて、単結晶半導体層の膜厚の厚いSOI基板を提供することを課題の一とする。その際に、予めシード層となる単結晶半導体層の結晶欠陥を修復しなくとも、良好にエピタキシャル成長が進む方法を提供することを課題の一とする。また、シード層の結晶欠陥を修復する工程を別に設けなくとも、固相エピタキシャル成長によりシード層である単結晶半導体層の結晶性が回復したSOI基板を提供することを課題の一とする。

【解決手段】絶縁層を介して基板に設けられた第1単結晶半導体層上に、非晶質半導体層を形成する。非晶質半導体層は、成膜温度100℃以上275℃以下、シラン系ガスを希釈しないで用いるCVD法により形成する。熱処理を行って、非晶質半導体層を固相エピタキシャル成長させて、単結晶半導体層の膜厚の厚いSOI基板を作製する。

(もっと読む)

101 - 120 / 619

[ Back to top ]