Fターム[5H006CA02]の内容

Fターム[5H006CA02]に分類される特許

1 - 20 / 796

空気調和機

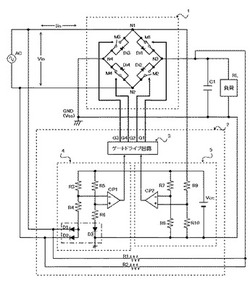

同期整流回路

【課題】部品点数の少ない同期整流型全波整流回路を提供する。

【解決手段】第1ノードおよび第2ノードに交流電圧が入力され、第3ノードから整流電圧が出力され、第4ノードがグランドとなるようにブリッジ構成された同期整流素子M1〜M4と、平滑コンデンサC1を含む全波整流回路における同期整流素子のオン/オフを制御する制御回路であって、タイミング制御回路2は、同期整流用素子M3、M4の電圧降下を検出し、該検出値に応じて同期整流用素子M1〜M4をオン・オフする制御信号を出力する電流検出回路4と、第4ノード電位を基準にして交流電圧の極性を検出し極性信号を出力する極性検出回路5とを備え、ゲートドライブ回路3は、電流検出回路4からのオン・オフ制御信号と、交流電圧の極性検出回路5の検出信号により各ノード間に接続された同期整流用素子M1〜M4のうち1対の素子を選択してオン・オフ駆動することを特徴とする。

(もっと読む)

スイッチング電源装置

【課題】入力に帰還する同相ノイズが小さく、小型化・高効率化が容易なブリッジレス・ブースト・コンバータ方式のスイッチング電源装置を提供する。

【解決手段】インダクタンスが略等しい第一及び第二昇圧インダクタ12,14と、マイナス端子が制御グランド20に接続された平滑コンデンサ16を備える。制御回路30によってオン・オフされる第一及び第二スイッチング素子22,26、及びそれらと相補的にオン・オフする整流素子24,28を備える。同じ巻数の3巻線を有する入力線インダクタ42を備え、第一巻線48の出力端48bが第一昇圧インダクタ12の入力端12aに接続され、第二巻線50の出力端50bが第二昇圧インダクタ14の入力端14aに接続される。第三巻線52の入力端52aが制御グランド20に接続され、出力端52bが交流遮断コンデンサ44を介して第二昇圧インダクタ14の入力端14aに接続される。

(もっと読む)

三相整流装置

【課題】力率を向上させつつ、入力電流に重畳する高周波スイッチングノイズを低減できる三相整流装置を提供する。

【解決手段】整流回路における各直列回路の両ダイオードの相互接続点と同整流回路の負側出力端との間を、三相交流電源からの入力電流が正レベルとなる位相の前縁側で回数N1だけ断続的に短絡し、同位相の後縁側で回数N2だけ断続的に短絡する。整流回路における各直列回路の両ダイオードの相互接続点と同整流回路の正側出力端との間を、三相交流電源からの入力電流が負レベルとなる位相の前縁側で回数N1だけ断続的に短絡し、同位相の後縁側で回数N2だけ断続的に短絡する。そして、回数N1,N2の比率N1/N2を入力電力に応じて切換える。

(もっと読む)

並列に接続された複数の制御電流源を備える電力変換器

【課題】整流器電流が特に大きい場合であっても、整流器電流の形状の制御を可能にする電力変換器を提案する。

【解決手段】電力変換器は整流器段(REC)と整流器電流(I)が流れるDC電源バスとを備える。前記変換器はさらに、そのDC電源バスにおいて並列に接続された少なくとも2つの制御電流源を備える。各制御電流源は、直列に接続されたインダクタ(L1、L2)および可変電圧源を備える。さらに、前記整流器電流(I)を前記第1の制御電流源内を流れる第1の電流(I1)と前記第2の制御電流源内を流れる第2の電流(I2)とに分配するように構成され、前記整流器電流(I)を成形し、かつ、前記第1の可変電圧源の端子における電圧(Ve1)と前記第2の可変電圧源の端子における電圧(Ve2)とを調整するように構成されている制御ユニット(3)を備える。

(もっと読む)

照明用電源および照明装置

【課題】調光器による出力電流の制御を安定化し、かつ消費電力を低減した照明用電源及び照明装置を提供する。

【解決手段】整流回路と、平滑コンデンサと、波形成形回路と、DC−DCコンバータと、を備えた照明用電源が提供される。前記整流回路は、入力される交流電圧を整流する。前記波形成形回路は、前記整流回路と前記平滑コンデンサとの間に接続され、前記整流回路から出力される電圧が相対的に高いときオンの状態とオフの状態とを繰り返すスイッチング動作をし、前記整流回路から出力される電圧が相対的に低いときオンの状態を継続して前記整流回路に電流を流す。前記DC−DCコンバータは、前記平滑コンデンサに充電された電圧を変換する。

(もっと読む)

照明用電源および照明装置

【課題】調光器により出力電流を連続的に変化できる照明用電源及び照明装置を提供することを目的とする。

【解決手段】整流回路と、平滑コンデンサと、基準電圧生成回路と、DC−DCコンバータと、を備えた照明用電源が提供される。前記整流回路は、入力される交流電圧を整流する。前記平滑コンデンサは、前記整流回路の出力を平滑化する。前記基準電圧生成回路は、前記整流回路の出力電圧及び前記平滑コンデンサの電圧の少なくともいずれかに基づいて基準電圧を生成する。前記DC−DCコンバータは、出力素子と定電流素子とを有し、前記平滑コンデンサの電圧を変換する。前記出力素子は、前記平滑コンデンサの電圧を供給され、前記基準電圧が相対的に高いときオンの状態とオフの状態とを繰り返すスイッチング動作をして発振し、前記基準電圧が相対的に低いときオンの状態を継続する。前記定電流素子は、前記出力素子に直列に接続され、前記基準電圧で制御された定電流を流す。

(もっと読む)

スイッチング電源装置

【課題】コンパクトで組み立て易く、トランス及び二次巻線側の不要な寄生インダクタンス成分や損失を小さくすることができるスイッチング電源装置を提供する。

【解決手段】トランス22は互いに同じ巻数の二次巻線28を複数個備える。二次巻線28は、磁性コア26に巻回されたコイル部32とその両端部を外に引き出す一対の引出部34を備える。整流回路36は、各々に主スイッチング素子20のオン・オフによる高周波電流が流れる高周波電流ライン44を有する。高周波電流ライン44は対応する二次巻線28ごとに設けられ、二次巻線28の一対の引出部34の間に接続され、引出部34と高周波電流ライン44とで高周波電流ループ46を形成する。複数の整流回路36が磁性コア26の近傍に配置され、個々の高周波電流ループ46が、他の整流回路36の高周波電流ループ46の形状と同様の形状に形成されている。

(もっと読む)

半導体装置

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

電源装置

【課題】 同期整流方式のスイッチング電源において、効率を低下させることなくオン抵抗の低いスイッチング素子を用いて正しく動作する。

【解決手段】 入力されたパルス電圧を整流する整流手段と、整流手段に対してパルス電圧が入力される側に設けられた電圧電流変換手段と、電圧電流変換手段の出力電流を電圧に変換する電流電圧変換手段と、電流電圧変換手段の電圧と基準電圧の差を比較する比較手段とを備え、比較手段からの出力によって整流手段の動作を制御する電源装置。

(もっと読む)

フォワード形直流−直流変換装置

【課題】フォワード形直流−直流変換器の同期整流回路の制御には、種々の方式があるが、一次回路の信号を受け取ることなく、簡単な制御で損失を低減することは難しかった。

【解決手段】変圧器の一次側回路からの信号を受け取ることなく、変圧器の二次巻線電圧、直流出力電圧、及び直前のオン時間幅又はオフ時間幅を組合せて把握することにより、同期整流用MOSFETのオン時間幅及びオフ時間幅を演算で求め、同期整流時にダイオードに電流が流れる時間を最少時間に抑制する。

(もっと読む)

セミブリッジレス力率改善回路とセミブリッジレス力率改善回路の駆動方法

【課題】小型化が可能になるとともにコストも低減されたセミブリッジレス力率改善回路とセミブリッジレス力率改善回路の駆動方法とを実現することを目的とする。

【解決手段】AC入力電源と、整流ブリッジ部と、第一のブーストコンバータと第二のブーストコンバータと、第一のブーストコンバータまたは第二のブーストコンバータをパルス駆動するパルス生成部とを備え、AC電源の入力に対応して第一のブーストコンバータと第二のブーストコンバータとを選択的に駆動し、整流ブリッジ部を構成する四つの回路素子のうち、第一または第二のブーストコンバータからの帰還電流が流れる二つの回路素子の少なくともいずれか一方は、帰還タイミングに合わせて導通するMOSFETで構成されるセミブリッジレス力率改善回路とする。

(もっと読む)

力率改善のための回路

【課題】体積が小さく、コストが低く、更にトータル圧力が90〜264V入力で設計でき、PFが0.90以上で制御ができる力率改善のための回路を提供する。

【解決手段】力率改善のための回路は、主に整流ユニットの出力端の両極の間に低周波フィルタリングユニットを設置してパルス幅変調制御ICの電圧と電流へ入力調整して同相するのに用い、更にパルス幅変調制御ICの電流補償ポート及び電圧補償ポートに第一、第二補償ネットワークを設置して第一、第二補償ネットワークで該位相調整ユニットの電流ゲイン(Gain)値を下げ、該パルス幅変調制御ICに不必要な動作が発生するのを防止し、トータル圧力が90〜264V入力下で設計して、PFを0.90以上に制御する目的を達成する。

(もっと読む)

AC/DCインバータ装置、および、AC/DCインバータ装置の制御方法

【課題】製造コストを削減することが可能なAC/DCインバータ装置を提供する。

【解決手段】AC/DCインバータ装置100は、直流電源が出力する直流電力を交流電力に変換し、且つ、交流電源が出力する交流電力を直流電力に変換するAC/DCインバータ装置であって、第1、第2の入出力端子T1、T2間に交流電源PSが接続され且つ第3、第4の入出力端子T3、T4間に外部負荷Rが接続され、交流電力を直流電力に変換する場合、制御回路3は、第1のスイッチ素子Q1および第3のスイッチ素子Q3をオフに固定し、且つ、第2のスイッチ素子Q2と第4のスイッチ素子Q4とのオン/オフを同期して切り替える。

(もっと読む)

鉄道車両用電力変換装置

【課題】鉄道車両の走行風によって冷却を行うようにした鉄道車両用電力変換装置におけるコンバータおよびインバータの冷却体の全体の温度分布が均一になるようにして、コンバータおよびインバータ双方の半導体素子を冷却効果を高めることにより全半導体素子の温度上昇がほぼ均等になるようにすることを課題とする。

【解決手段】鉄道車両の床下に設置され、半導体素子変換回路により交流電力を直流電力に変換するコンバータと、半導体素子変換回路により前記コンバータから出力される直流電力を三相交流電力に変換するインバータと、前記コンバータおよび前記インバータの変換回路を構成する半導体素子を冷却する、複数の冷却フィンを有する冷却体とを備え、前記鉄道車両の走行によって発生する走行風を前記冷却フィンに当てて前記半導体素子の冷却を行うようにした鉄道車両用電力変換装置において、前記コンバータの変換回路を構成する半導体素子と前記インバータの変換回路を構成する半導体素子を冷却する冷却体を熱的に一体化した共通の冷却体とする。

(もっと読む)

交流直流変換器

【課題】回路を流れる電流の経路にある半導体素子の数を減らすことにより、導通損失を低減する交流直流変換器を提供する。

【解決手段】

本発明に係る交流直流変換器は、交流電源から出力された交流電圧を直流電圧に変換する交流直流変換器であって、前記交流電圧を整流して前記直流電圧を出力する整流手段と、リアクトルと、キャパシタと、前記交流電源に接続されたスイッチング整流手段とを備え、前記スイッチング整流手段のスイッチングにより、前記キャパシタの端子間に直流電圧を出力する。

(もっと読む)

高圧電源装置及び画像形成装置

【課題】画像形成装置の高圧供給の機能を維持しつつ、高圧電源の数を削減して、高圧電源を小型化する。

【解決手段】所定の極性の高電圧を出力する第1の高圧出力部と、前記第1の高圧出力部の出力部に接続された複数の整流部と、前記複数の整流部のうちの1つに接続され、前記所定の極性とは逆極性の高電圧を出力する第2の高圧出力部と、前記複数の整流部のうちの他の1つに接続され、前記所定の極性とは逆極性の高電圧を出力する第3の高圧出力部と、を有し、前記複数の整流部は、前記第2の高圧出力部に流れる電流経路と前記第3の高圧出力部に流れる電流経路を分離する。

(もっと読む)

スイッチング電源、およびスイッチング電源におけるAC波形生成方法

【課題】トランスなどの直流遮断素子を使用せず交流電圧の極性判定と電圧検出とができる、PFCスイッチング電源を実現する。

【解決手段】入力部に入力された交流電圧を整流し、負荷に直流出力を出力するとともに力率の改善を行う力率改善部と、入力部の正極電圧および負極電圧に対応して正極検出電圧および負極電圧を出力する入力電圧検出部と、正極および負極検出電圧に基づいて力率改善部の動作を制御するスイッチング制御部とを備え、スイッチング制御部のAC波形生成部は、正極および負極検出電圧極に基づいてAC波形を生成し、スイッチング制御部は、AC波形情報に応じて周期およびデューティ比が変化する駆動パルスを生成し、力率改善部が有する1または複数のスイッチ素子を駆動して、力率改善部の直流出力を所定の直流出力に維持するとともに、力率の改善を行うこととした。

(もっと読む)

電力変換装置及びその制御方法

【課題】複数台のチョッパ回路とDC/DCコンバータとが並列に接続される電力変換装置では,内部インピーダンスが異なることによってコンバータの出力電流間に不均等が生じる。このため,コンバータごとに出力定電圧制御を行おうとすると,構成や制御が複雑になる等の課題があった。そこで,本発明は,簡単な回路構成で並列運転時のDC/DCコンバータ間の出力電流の分担を均等にすることを目的とする。

【解決手段】本発明に係る電力変換装置は,複数のチョッパ回路の出力側にそれぞれDC/DCコンバータが接続され,チョッパ制御回路は,チョッパ回路出力電圧検出値にチョッパ回路電流検出値の電圧換算値を重畳した値が基準値よりも高い場合はチョッパ回路の出力電圧を減らす方向に,前記基準値よりも低い場合はチョッパ回路の出力電圧を増やす方向に,チョッパ回路内のスイッチング素子を制御する。

(もっと読む)

電源装置

【課題】力率を改善するため、オン抵抗が小さく、スイッチング速度が速いスイッチング素子を用いた電源装置において、スイッチング素子のソース−ドレイン間に寄生容量があると、スイッチング損失が発生する。スイッチング損失がない、効率を改善した電源装置を提供する。

【解決手段】電源装置は、整流回路に接続されるインダクタと正極端子との間に接続される第1整流素子と、前記第1整流素子の入力端子と負極端子との間に接続される第1スイッチング素子と、前記第1スイッチング素子に並列に接続される第2スイッチング素子及びトランスと、前記第2スイッチング素子と前記トランスの接続部と、前記正極端子との間に接続され、前記接続部から前記正極端子に向かう整流方向を有する第2整流素子と、前記トランスと前記正極端子との間に接続され、前記トランスから前記正極端子に向かう整流方向を有する第3整流素子を有する。

(もっと読む)

1 - 20 / 796

[ Back to top ]