Fターム[5H730AS19]の内容

DC−DCコンバータ (106,849) | 用途 (11,272) | 電子計算機用 (222)

Fターム[5H730AS19]に分類される特許

101 - 120 / 222

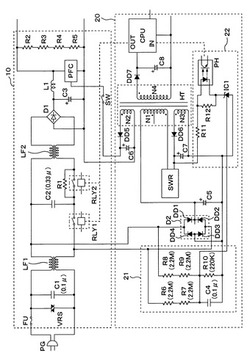

電源装置

【課題】残留電圧を小さくするための放電抵抗による電力消費を小さくする電源装置を提供する。

【解決手段】アクロスコンデンサC1と、アクロスコンデンサC1よりも容量値が大きいアクロスコンデンサC2とを備える。また、アクロスコンデンサC1とアクロスコンデンサC2との間配されるラインフィルタLF1と、アクロスコンデンサC1とアクロスコンデンサC2との接続を導通または切断とするリレーRLY1とを備える。また、待機時においてリレーRLY1を切断するように制御するシーピーユーCPUを備える。また、少なくとも待機時において、アクロスコンデンサC1からの電流が流れる放電抵抗(抵抗R6、抵抗R7、抵抗R8、抵抗R9)を備えるようにした。

(もっと読む)

コンピュータによって実現される方法、コンピュータ読取可能な媒体、およびコンピュータシステム

【課題】電源の設計のためのコンピュータによって実現される方法が開示される。

【解決手段】電源設計変数の複数のリストが提供される。当該方法は、変数についてのこれらの複数のリストから選択された電源設計変数に応じて第1の電源設計をシミュレートするステップを含む。当該方法はさらに、第1の電源設計のスコアを計算し、当該スコアが電源設計の組に含まれるいずれかの電源設計のスコアよりも優れているかどうかを判断する。優れていると判断された場合、当該方法は、前記電源設計の組のうち最低のスコアを有する電源設計を当該第1の電源設計と置換える。

(もっと読む)

DC−DCコンバータの制御回路、DC−DCコンバータ、およびDC−DCコンバータの制御方法

【課題】出力電圧を安定化することが可能なDC−DCコンバータ等を提供すること。

【解決手段】電流モードの降圧DC−DCコンバータ1の制御回路11は、スロープ補償回路SCとオフセット回路IF1とを備える。スロープ補償回路SCは、スイッチSW1のオン期間Tonが動作周期Tの1/2を超える範囲において、コイル電流波形Vsenseの増加傾きに、スロープ補償による増加傾きm2を加える。オフセット回路IF1は、オン期間Tonの動作周期Tの1/2からの超過時間に応じて小さくなるオフセット電圧Voffsetを、コイル電流波形Vsenseに付与する。

(もっと読む)

スイッチング電源装置

【課題】1つの電源回路からなる単一出力のスイッチング電源装置において、スイッチング電源装置への入力電圧の、遮断または低下時に、スイッチング電源装置からの出力電圧を停止または低下させるスイッチング電源装置を提供する。

【解決手段】1つの電源回路からなる単一出力のスイッチング電源装置100は、スイッチング電源装置100への入力電圧の、遮断または低下から所定時間経過後に、スイッチング電源装置100からの出力電圧を、停止させるスイッチSW1、SW3、およびスイッチSW5と過電流保護バイアス抵抗19との直列回路を備える。

(もっと読む)

電力コンバータの監視および制御

デジタルコントローラは、電力コンバータの調節を促進するデジタルフィードバック経路に信号を注入し、対応する位相、ゲイン、または周波数を測定するように構成される。デジタルコントローラはまた、測定値に部分的に基づき、電力コンバータの動作属性を調整するための適応同調コントローラを含んでもよい。例示的実施形態では、適応同調コントローラは、デジタルフィードバック信号を調整するように、位相、ゲイン、および/または周波数測定値を使用する。例示的実施形態では、適応同調コントローラは、動作測定値を所望の値と比較し、調整された動作属性を生成する。例示的実施形態によれば、デジタルフィードバック信号の監視および調整は、デジタルコントローラが電力コンバータの中の電力信号を調節している間に生じる。  (もっと読む)

(もっと読む)

電源システム

【課題】 従来よりも力率および電力損失を改善し、トランスの小型化を図ることができる電源システムを提供することを目的とする。

【解決手段】 電源システム100は、AC100VをAC24Vに変換する電源トランス110と、電源トランス110に接続された複数の電源ユニット200−1〜200−nとを有する。電源ユニット200−1は、AC24Vを同期整流型ブリッジにより整流する整流回路210と、整流された電圧の力率を改善する力率改善回路220と、直流電圧を出力する出力回路230とを有する。力率改善回路220は、インダクタLと、FET1と、FET2と、FET1およびFET2のスイッチングを制御する制御回路222とを含み、制御回路222は、FET1とFET2のデューテイ比を調整し、所望の直流電圧を出力回路230から出力させる。

(もっと読む)

スイッチング電源制御回路

【課題】スイッチング電源の消費電流を削減する。

【解決手段】スイッチング電源制御回路は、入力電圧から目的レベルの出力電圧を生成するために、入力電圧が印加された負荷の導電状態を変化させる第1トランジスタのオンオフを制御する制御回路と、入力電圧に応じた電圧が制御電極に印加され、入力電圧が抵抗を介して入力電極に印加され、出力電極に対する制御電極の電圧が所定のしきい値電圧より高くなるとオンして抵抗の抵抗値に応じた第1電流を出力電極から出力する第2トランジスタからの第1電流によって、第1電流の電流値に応じたレベルの制御回路に対する電源電圧を生成する電圧生成回路と、を備え、電圧生成回路は、制御回路が電源電圧によって起動されると、負荷に流れる電流に応じた第2電流を生成する電流生成回路からの第2電流によって、電源電圧を第2電流の電流値に応じたレベルにするとともに、第2トランジスタをオフすべく、第2電流の電流値に応じたレベルの電圧を出力電極に印加する。

(もっと読む)

電子機器

【課題】オン状態で電源回路の平滑コンデンサに充電された電荷を、効率よく、オフ状態での待機電力の供給に利用する。

【解決手段】電源がオン状態の電子機器1をオフ状態にする際に、負荷スイッチ31を開いて負荷回路40を電源回路20から切断した状態で、メイン電源から切断された電源回路20の平滑コンデンサ22,29に残留している電荷の少なくとも一部を降圧コンバータ50から蓄電素子80に充電させる。この際、蓄電素子80の充電電圧をオン状態での蓄電素子80の充電電圧よりも高くする。

(もっと読む)

電源電圧降圧回路、半導体装置および電源電圧回路

【課題】昇圧回路にて生じたノイズの影響を低減できる、出力段としてNchトランジスタが用いられる電源電圧降圧回路を提供する。

【解決手段】電源電圧降圧回路は、一端に第1電圧の電源電圧が供給され、他端が出力端子として機能する出力用Nチャネルトランジスタと、第1電圧を昇圧して、第1電圧よりも高い第2電圧を生成する昇圧回路と、第2電圧を降圧して、第1電圧よりも高く、かつ、第2電圧よりも低い、第3電圧を生成する降圧回路と、第3電圧を電源電圧として用いて、基準電圧と出力端子に生じる電圧との差を増幅して第4電圧を生成し、第4電圧を出力用Nチャネルトランジスタのゲートに供給するアンプと、を含む。

(もっと読む)

降圧形コンバータ

【課題】 電力効率が高く、より降圧比率の大きな低電圧を出力するのに適した降圧形コンバータを提供すること。

【解決手段】 二つの入力端子1、2間に互いに直列に接続されたスイッチ素子4とインダクタ6とコンデンサ7と、コンデンサ7と閉回路を構成するよう接続されたスイッチ素子8と電流循環用素子9と、電流循環用素子9と閉回路を構成するよう接続されたインダクタ10とコンデンサ11と、スイッチ素子4とインダクタ6とが接続される点Aと、スイッチ素子8とインダクタ10と電流循環用素子9とが接続される点Bとの間に接続されたコンデンサ16と、制御回路17とを備え、コンデンサ16はスイッチ素子4がオンのときに充電され、スイッチ素子4のオフの期間にスイッチ素子4の両端に印加される電圧は、二つの入力端子1、2の間の電圧とコンデンサ16の充電電圧との差の電圧であることを特徴とする降圧形コンバータ。

(もっと読む)

電源装置および半導体集積回路装置

【課題】PFCコントローラを用いた電源装置の軽負荷時における効率を大幅に向上させる。

【解決手段】PFCコントローラ10には、電圧/電流変換部17が設けられている。電圧/電流変換部17は、出力電圧の電圧レベルを検出する誤差増幅器11から出力された信号の電圧を任意の電流値に変換し、補正電流として出力する。電圧/電流変換部17は、誤差増幅器11が軽負荷時と検出した際に大きな電流値の補正電流を出力し、PFCコントローラ10が出力電圧を下げる制御を行う。

(もっと読む)

電源装置および半導体集積回路装置

【課題】スイッチングレギュレータにおける軽負荷時の出力電圧の変動を改善し、安定した電源を提供する。

【解決手段】コンパレータ12は、エラーアンプ11の電流指示値と基準電圧STOPREFとを比較し、電流指示値が基準電圧STOPREFより低くなるとHiレベルの信号を出力してPWM制御を行い、電流指示値が基準電圧STOPREFよりも高くなると、Loレベルの信号を出力し、トランジスタ10のスイッチング動作を停止させてPWM制御を停止させる。負荷電流量が少ない軽負荷時には、トランジスタ10のONタイミングが電流指示値によって制御されることになり、出力電圧Voのリップルを抑えたスイッチング制御を行うことができる。

(もっと読む)

電源装置および半導体集積回路装置

【課題】軽負荷時のスイッチングロスを大幅に低減し、出力電圧の精度を向上させる。

【解決手段】軽負荷時において、コイル電流ILが0Aよりも低くなり逆電流が発生すると、逆流検出回路7は、逆流検出信号RCP_DETを出力する。PFM制御回路2は、逆流検出信号RCP_DETを受けてPFMパルスを生成する。ロジック回路3は、PFM制御回路2が生成するPFMパルス信号のHiレベル期間がPWM信号のHi期間よりも長くなると、PFMパルス信号を出力する。また、出力電圧VOUTが上昇し、エラーアンプ8の誤差信号EAOの電圧レベルが低下して三角波SLOPEの電圧レベルよりも低くなり、PWM信号がHiレベルとならない期間が発生すると、ロジック回路3のパルススキップ回路がスキップ信号を出力し、PWM信号の出力を停止する。

(もっと読む)

電圧比較装置、電子システム

【課題】入力電圧の電圧降下に対応した電圧比較装置を提供する。

【解決手段】本発明の電圧比較装置は、所定の基準電圧VREFと入力電圧VCCINとを比較して、入力電圧VCCINが基準電圧VREFよりも低い場合に第1状態になり、入力電圧VCCINが基準電圧VREFよりも高い場合に第2状態になる検知信号VCCOKを出力する比較器2と、入力電圧VCCINの候補となる複数の候補電圧V1〜V5を出力可能とし、検知信号VCCOKが第1状態の場合に入力電圧VCCINよりも低い候補電圧を入力電圧VCCINとして比較器2へ出力し、検知信号VCCINが第2状態の場合に入力電圧VCCINよりも高い候補電圧を入力電圧VCCINとして比較器2へ出力する入力電圧生成回路3とを備える。

(もっと読む)

スイッチング電源回路

【課題】交流スイッチの無い電子機器に備えられ制御回路を備えるスイッチング電源回路において、二次側回路の電源がオフの場合に制御回路への給電を維持しつつ消費電力を削減する。

【解決手段】一次側回路が、交流電源からの交流電圧が全波整流された直流電圧を平滑するコンデンサC1から出力された直流電力が抵抗R2、R3、R4を介して制御IC53へと供給される第一の経路の他に、交流電源からの交流電圧を半波整流するダイオードD1から出力された直流電力が抵抗R1を介して制御IC53へと供給される第二の経路と、補助電源監視回路51とを備える。補助電源監視回路51が、補助電源55に電圧が発生している場合に、第一の経路を通電し且つ第二の経路を電気的に遮断し、補助電源55に電圧が発生していない場合に、第一の経路を電気的に遮断し且つ第二の経路を通電する。

(もっと読む)

モバイル機器の電源回路装置

【課題】バッテリを複数個搭載したモバイル機器において、それぞれのバッテリ放電容量を効率よく使用することのできる電源回路装置を提供する。

【解決手段】ユーザー交換不可能な複数の内蔵バッテリ1、2あるいはユーザー交換可能な複数の交換バッテリ1、2と、前記おのおののバッテリ出力に対して内部寄生ダイオードのアノードを向かい合わせるようにそれぞれ1個ずつバッテリ側および回路側とに配置されたMOSFET16〜19と、これらのMOSFET16〜19のオンオフ制御端子11〜14とを備え、内部寄生ダイオードを用いたバッテリ間の逆流電流を防止するようにMOSFET16〜19を制御することで、バッテリ残容量を効率よく使用できるモバイル機器を提供することができる。

(もっと読む)

昇圧型スイッチングレギュレータおよびその制御回路

【課題】昇降圧動作の停止時に流れる電流を遮断するとともに、ソフトスタートを実現する。

【解決手段】第1トランジスタM1は、同期整流トランジスタSW2の一端と、そのバックゲートとの間に、ボディダイオードのカソードが出力端子204側となる向きで設けられる。第2トランジスタM2は、同期整流トランジスタSW2の他端と、そのバックゲートとの間に、ボディダイオードのカソードがスイッチング端子108側となる向きで設けられる。スイッチ制御部12は、スイッチングレギュレータ200の昇圧停止状態から昇圧動作状態に遷移する間の第1期間に、スイッチングトランジスタSW1をオフ、第1トランジスタM1をオン、第2トランジスタM2をオフした状態で、同期整流トランジスタSW2をスイッチングさせる。

(もっと読む)

電源供給回路

【課題】電源装置を備えた装置の信頼性の向上を図りつつ、装置自体の小型化、低コスト化を図ること。

【解決手段】複数の電源供給対象装置と、当該各電源供給対象装置に対応してそれぞれ電源を供給する各電源装置と、を備え、上記電源供給対象装置のうち特定の電源供給対象装置と、この特定の電源供給対象装置に対応する特定の電源装置とは異なる他の電源装置と、を接続すると共に、この接続間に、特定の電源供給対象装置に供給される電源の電圧降下に応じて当該特定の電源供給対象装置に他の電源装置から電源を供給する電源供給手段を備えた。

(もっと読む)

チャージポンプ回路

【課題】昇圧電圧を目標電位までに立ち上げる時間を短縮することができると共に、消費電力のコストダウンを図ることができるようにしたチャージポンプ回路を提供する。

【解決手段】第2のドライバ回路75用の電源回路80を設け、電源回路80の構成を、第2のドライバ回路75に電圧(VOUT−|Vthp101|)を供給するだけでなく、入力電圧VINの投入後、ポンピング開始前に、電圧入力端子51から電源回路80内のPMOSトランジスタ100のソースとNウェルとのPNジャンクションを通して昇圧電圧出力端子52に電荷を供給することができる構成とする。

(もっと読む)

電源装置、電力接続回路、コンピュータ及び電気機器

【課題】並列接続した複数の電力変換器が電力変換効率を向上できるようにし、また、構造を簡単にして製造コストを低減する。

【解決手段】直流電力を負荷20に供給する電源装置10であって、入力された電力を所定電圧の直流電力に変換して出力する第1から第nの電力変換器101〜103と、第2から第nの電力変換器102、103を、負荷20の消費電力に応じて、第1電力変換器101に、順次並列接続する接続手段とを備えた。

(もっと読む)

101 - 120 / 222

[ Back to top ]