Fターム[5H730BB57]の内容

DC−DCコンバータ (106,849) | 主変換部の型式 (20,669) | 非共振型 (4,027) | 他励型(発振器を用いるもの) (3,815)

Fターム[5H730BB57]に分類される特許

81 - 100 / 3,815

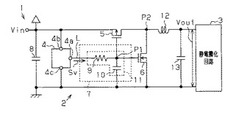

DC/DCコンバータ、イオン発生装置及び静電霧化装置

【課題】例えば専用ICやドライバICを使用せずに、同期整流化を実現することができるDC/DCコンバータ、イオン発生装置及び静電霧化装置を提供する。

【解決手段】DC/DCコンバータ2は、コントローラ4、メインスイッチング素子5及び同期整流用スイッチング素子6を備える。コントローラ4と両スイッチング素子5,6との間に、CR回路11からなるデッドタイム生成回路7を接続する。CR回路11は、自身の時定数から決まる電圧勾配を持つ駆動電圧により、スイッチング素子5,6をオンオフ制御する。これにより、スイッチング素子5,6のオンタイミングがずれ、スイッチング素子5,6の間にデッドタイムが生成される。

(もっと読む)

ソフトスタート回路

【課題】ソフトスタート回路において、スイッチング素子にストレスを加えることなく、より安全に、かつ、出力電圧の立ち上がり時間を最適に早くする 。

【解決手段】電流モード方式のスイッチング電源装置の制御回路のソフトスタート回路は、カウンタ部とDAコンバータ部、ブランキング部、抵抗R1、R2及び制御回路の基準電源Regからなる。カウンタ部からのカウント出力はデコーダDECを介してDAコンバータに入力し、過電流保護回路の基準電圧VOCPとする。基準電圧VCOPを徐々に増加させることにより、スイッチング素子Qのドレイン電流Idを抑制しながら起動させることができる。

(もっと読む)

電力変換装置

【課題】リセット信号の生成に関連する手段が故障したり誤動作したりしてもスイッチング素子の過熱による故障を抑えられ、入力電圧が急激に上昇しても出力電圧の上昇を抑えられる電力変換装置を提供する。

【解決手段】リセット信号の生成に関連する、マイクロコンピュータ170内のブロック等が故障したり誤動作したりしても、制限信号生成部170lと信号選択回路173が駆動信号のパルス幅を制限する。そのため、IGBT10をオフできる。従って、過電流に伴って発生するIGBT10の過熱による故障を抑えられる。また、制限信号生成部170lと信号選択回路173は駆動信号のパルス幅を入力電圧に基づいて制限する。そのため、入力電圧が上昇しても、マイクロコンピュータ170内のブロック等やコンパレータ171の応答遅れの影響を受けることなく駆動信号を即座に調整できる。従って、入力電圧が急激に上昇しても出力電圧の上昇を抑えられる。

(もっと読む)

故障検出装置および方法

【課題】スイッチのオープン故障を検出することを可能とする故障検出装置および方法を提供する。

【解決手段】本発明による故障検出装置(10)は、電源と負荷との間に接続されたスイッチ(Q2)と並列接続された電圧降下素子(D2)と、前記スイッチの開閉を制御するスイッチ制御部(13)と、前記スイッチ制御部が前記スイッチを開または閉に制御した状態で前記電圧降下素子の端子間の相対電圧を検出する電圧検出部(11)と、前記電圧検出部により検出された相対電圧と前記スイッチ制御部による前記スイッチの制御状態とに基づき前記スイッチの故障を判定する故障判定部(12)とを備える。

(もっと読む)

DC/DCコンバータ

【課題】トランス3によって一次側と二次側とが絶縁されたDC/DCコンバータにおいて、トランス3の二次側に発生するサージ電圧を容易な構成で抑制すると共に、サージエネルギを確実に有効利用する。

【解決手段】トランス3の二次巻線両端にそれぞれアノードが接続された第1、第2のダイオード9a、9bおよび整流回路4の共通カソード端4Aにアノードが接続された第3のダイオード9cと、抵抗11とコンデンサ10とを直列接続した直列回路とから成るスナバ回路8を備え、第1〜第3のダイオード9a〜9cのカソードを、抵抗11とコンデンサ10との接続点に接続して、トランス3の二次側に発生するサージ電圧をコンデンサ10の電圧でクランプし、コンデンサ10に蓄電されたサージエネルギを抵抗11を介して負荷7に回生する。

(もっと読む)

電力変換装置および該電力変換装置における過電圧保護方法

【課題】トランスの絶縁破壊に起因した過電圧を抑制することを可能とする電力変換装置および過電圧保護方法を提供すること。

【解決手段】本発明による電力変換装置は、直流入力をトランス(T)の1次巻線に断続的に供給することにより該トランスの2次巻線に電圧を誘起させ、前記2次巻線に誘起された電圧を整流して所望の直流出力を第1出力端子と第2出力端子との間に発生させる電力変換装置(1)であって、前記トランスの2次巻線の一端と前記第1出力端子との間の第1電流経路と、前記2次巻線の他端と前記第2出力端子との間の第2電流経路との間に現れる過電圧を検出する検出部(10)と、前記検出部が前記過電圧を検出した場合、前記第1電流経路と前記第2電流経路との間を短絡する短絡部(20)と、前記検出部が前記過電圧を検出した場合、前記トランスの1次巻線への前記直流入力の供給を遮断する遮断部(30)とを備える。

(もっと読む)

スイッチング制御装置

【課題】スイッチング回路全体の導通損失を低減しつつ、スイッチング回路を構成するスイッチング素子の損傷を防止する。

【解決手段】スイッチング制御装置10は、ハイ側スイッチング回路21又はロー側スイッチング回路22を非導通状態から導通状態に遷移させる際には、ユニポーラ型半導体素子をオフからオンに切り替えた後にバイポーラ型半導体素子をオフからオンに切り替え、導通状態から非導通状態に遷移させる際には、バイポーラ型半導体素子をオンからオフに切り替えた後にユニポーラ型半導体素子をオンからオフに切り替える。ハイ側スイッチング回路21又はロー側スイッチング回路22の導通状態において、ユニポーラ型半導体素子(SiC)の温度検出値TSiCが高温判定閾値Th以上である場合には、バイポーラ型半導体素子をオンに維持しつつユニポーラ型半導体素子をオンからオフに切り替える。

(もっと読む)

スイッチング電源装置及び現金自動預け払い装置

【課題】起動時間を短縮しながらも交流電圧の瞬断時に備えた充電電圧を確保することができるスイッチング電源装置及び現金自動預け払い装置を提供する。

【解決手段】DC/DC変換回路36から出力された直流電圧の大きさが予め定められた大きさ未満の場合に、配線34Aから電圧がコンデンサC2,C3に印加されないように配線34AとコンデンサC2,C3とを電気的に切断し、DC/DC変換回路36から出力された直流電圧の大きさが予め定められた大きさ未満の場合に、配線34Aから電圧がコンデンサC2,C3に印加されるように配線34AとコンデンサC2,C3とを電気的に接続するようにスイッチング動作を行うリレー回路RL1を備える。

(もっと読む)

スイッチング電源装置

【課題】ノイズを減少させて安定的に動作するスイッチング電源装置。

【解決手段】トランスTの一次巻線P1とスイッチング素子Q1との直列回路、Q1をオンオフさせる制御回路、トランスの二次巻線S1に発生した電圧を整流平滑する整流平滑回路D、C1、整流平滑回路の出力電圧と基準電圧との誤差電圧を制御回路に出力する誤差増幅回路OPを備え、制御回路は、Q1をオンオフさせる信号を生成する信号生成部OSC、OSCの出力信号からパルス数をカウントし、カウント値が所定値に達する毎に発振周波数を減算させる周波数減算器を備え、かつ、周波数を減算させた時のパルス信号が遅延されるように遅延時間を切り替えてQ1のオン時間を制御する遅延時間切替回路22を備える。

(もっと読む)

チャージポンプ及びこれを用いた電源装置

【課題】プリント配線基板上の実装面積削減やコスト削減を実現することのできるチャージポンプを提供する。

【解決手段】チャージポンプ100は、フライングキャパシタ120の充放電用スイッチとして、半導体装置110に集積化されたフローティングNMOSFET111及び112のボディダイオード111d及び112dを用いる。

(もっと読む)

ロボットシステム

【課題】モータの駆動を制御する駆動制御手段の制御内容を変更することなく、高トルク運転時にモータに対して十分な電力を供給可能とするか、または減速動作時にモータから生じる回生エネルギーを有効利用可能とする。

【解決手段】昇降圧回路29は、入力電圧を昇圧して出力する昇圧動作、入力電圧を降圧して出力する降圧動作および入力電圧をそのまま出力する非昇降圧動作のいずれかの動作を実行する。電源制御部26は、エコモードに設定されると、モータMの動作状態にかかわらず、降圧動作を実行するように昇降圧回路29の動作を制御する。電源制御部26は、トルク重視モードに設定されると、バス電圧の検出値に基づいてモータMが加速動作されていると考えられる期間に昇圧動作を実行するとともに、その期間を除く期間には非昇降圧動作を実行するように昇降圧回路29の動作を制御する。

(もっと読む)

スイッチング装置及びその制御方法

【課題】出力端子の数よりもコイルの数の少ないスイッチング装置を提供する。

【解決手段】メインスイッチング素子24のオンオフに伴って整流回路30に電流が流れ、第1サブスイッチング素子42及び第2サブスイッチング素子52のうちオンである方に整流回路30から電流が流れる。そして、第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御して第1出力回路40及び第2出力回路40のいずれに整流回路から電流が流れるかを切り替えることで、第1出力回路40を流れる電流に応じて直流電源を変圧した電圧が第1出力端子21から出力され、第2出力回路50を流れる電流に応じて直流電源を変圧した電圧が第2出力端子22から出力される。したがって、1つの整流回路30を共用することにより、出力端子の数よりもコイルの数を少なくすることができる。

(もっと読む)

DC/DCコンバータ

【課題】フィードフォワード制御方式のDC/DCコンバータにおいて、従来よりも電力変換効率を向上させる。

【解決手段】DC/DCコンバータ1において、制御回路20は、負荷電流Iloadおよび入力直流電圧Vinに基づいてインダクタ電流ILの上限値を決定し、検出したインダクタ電流ILがこの上限値を超えないようにスイッチング素子n_drのオン時間およびオフ時間の少なくとも一方を変化させる。

(もっと読む)

電源コントローラ

【課題】電源の出力の適切な制御を可能にしつつ、望ましくない可聴周波数の範囲内での有効スイッチング周波数を避けるための1次側コントローラを、低コストで実現する。

【解決手段】電源コントローラが開示される。例示的な電源コントローラは、電源の出力を表わす検知信号に応じて、フィードバック信号を生成するように結合された信号分離回路を含む。誤差信号生成器は、フィードバック信号と参照信号とに応じて、誤差信号を生成するように結合される。制御回路は、誤差信号と電流検知信号とに応じて駆動信号を生成するように結合される。駆動信号は、前記電源のスイッチのスイッチングを制御するように結合される。多重サイクル変調回路が制御回路に含まれて、スタートスキップ信号と、ストップスキップ信号と、スキップマスク信号とに応じてスキップ信号を生成するように結合される。

(もっと読む)

半導体装置及びこれを備える情報処理装置

【課題】安定したチャージポンプ動作を行う。

【解決手段】ノードA,Bを有するコンデンサC1と、VDDレベルからVSSレベルの間で振幅するポンピング信号PUMP1をコンデンサC1のノードAに供給するポンピング回路110と、コンデンサC1のノードBをVPPextレベルにプリチャージし、ポンピング信号PUMP1がVSSレベルからVDDレベルに変わった時に、コンデンサC1のノードBをVPPextレベルよりも高いレベルに駆動する出力回路120とを備える。本発明によれば、コンデンサC1のノードAをポンピングするための電圧と、コンデンサC1のノードBをプリチャージするための電圧が異なっていることから、昇圧電圧を効率よく生成することできる。

(もっと読む)

スイッチング電源装置

【課題】負荷への過電圧保護のためのラッチ停止機能を利用し、負荷が待受状態とされる無負荷時における省電力化を図るとともに、スイッチングトランスの鳴きを防止して静粛性を高める。

【解決手段】負荷1が待受状態とされる無負荷時に、負荷を制御する主制御部2から電圧上昇回路43への制御により、制御IC420の電源端子P420cに印加される端子電圧を負荷への過電圧保護に必要な閾値電圧と比較して上昇させることにより、トランジスタ41のスイッチング動作をラッチ停止する。また、負荷を制御する主制御部からラッチ解除回路44への制御により、制御IC420の電源端子に印加される端子電圧を、制御IC420が動作する最低動作電圧と比較して電圧降下させることにより、ラッチ停止を解除し、トランジスタ41のスイッチング動作を再開する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】デカップリング容量素子の信頼性と、フラッシュメモリの動作モードに対応した供給電流の補償を損なわずに、フラッシュメモリの面積増加を抑制する。

【解決手段】本発明に係る半導体集積回路10は、フラッシュメモリ部12と、フラッシュメモリ部12に電圧を供給する昇圧回路13と、昇圧回路13の出力に一端が接続されたデカップリング容量素子15と、フラッシュメモリ部12の動作モードに応じて、デカップリング容量素子15の他端の電位を制御する制御回路14とを備える。

(もっと読む)

電源装置及び発光素子駆動装置

【課題】デジタル回路からの出力信号のライン数を増やすことなく、簡単な回路構成で、同じ周波数の駆動信号を従来よりも低い周波数の動作クロックを生成する。

【解決手段】ADC11からのデジタル値に基づいて、CPU14が一定時間毎に制御指令値を算出する。この制御指令値に基づいて、PWMユニット15がパルス信号S3のデューティ比を決定し、出力電圧Voutの安定化を図る。マイクロプロセッサ4からは、単独のパルス信号S3の出力ラインだけがあればよい。また、駆動信号S5の周波数はランプ信号S2と同一で、クロック信号S1に同期する。したがって、クロック信号S1ひいては駆動信号S5の周波数は、コンバータ2の仕様を考慮して決定できる。一方、パルス信号S3の周波数は、ランプ信号S2の周波数よりも低くてもよい。

(もっと読む)

電源装置および照明装置

【課題】簡単な構成で、負荷の出力を一定に保ちながら、雑音強度を低減できる電源装置を提供する。

【解決手段】電源装置10は、交流電源Eを整流する整流回路15と、電源電圧変換部16とを備える。電源電圧変換部16は、整流回路15とそれぞれLED素子11a,11bが接続される複数の出力部13a,13bとの間に設けられた複数の電源電圧変換回路16a,16bを有している。各電源電圧変換回路16a,16bには整流回路15で整流された電源電圧を変換して各LED素子11a,11bに供給するスイッチング素子Q1,Q2を設ける。各電源電圧変換回路16a,16bのスイッチング素子Q1,Q2は、少なくとも2つ以上の異なるスイッチング周波数であるとともにそれぞれのスイッチング周波数を一定としてオンオフ動作する。

(もっと読む)

定電流出力制御型スイッチングレギュレータ

【課題】電流検出用の抵抗器が不要になり、部品点数の削減を図ることができ、該抵抗器に流れる電流による損失をなくすことができる、入力電圧を所望の出力電流に変換して出力する定電流出力制御型スイッチングレギュレータを得る。

【解決手段】クロック信号CLKがハイレベルのときに、スイッチングトランジスタM1に初期電流値i0の電流が流れたときの電流センス電圧VSNSをサンプリングし、クロック信号CLKがローレベルのときに、第1基準電圧VREF1とサンプリングした電流センス電圧VSNSとの電圧差ΔVSを第1基準電圧VREF1に加算して生成した第2基準電圧VREF2と、電流センス回路2の電流センス電圧VSNSとの電圧比較結果を示す信号CPOUTによって、PWM制御時におけるスイッチングトランジスタM1及び同期整流用トランジスタM2の各動作を制御するようにした。

(もっと読む)

81 - 100 / 3,815

[ Back to top ]