Fターム[5J022CB06]の内容

アナログ←→デジタル変換 (13,545) | 基準電圧・バイアス系 (1,329) | 加減算制御 (575)

Fターム[5J022CB06]の下位に属するFターム

基準電圧切換動作制御 (53)

Fターム[5J022CB06]に分類される特許

21 - 40 / 522

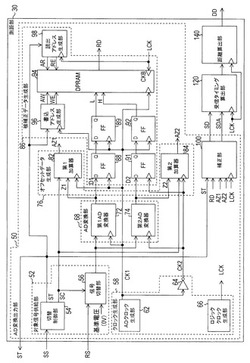

信号処理装置

【課題】複数のAD変換器を用いて同一のアナログ信号をAD変換する信号処理装置において、個々のAD変換器の特性のばらつきによって生じる同一のアナログ信号のAD変換精度の低下を抑制する。

【解決手段】クロック生成部58はπ[rad]位相の異なる二つのクロックを生成し、対象信号供給部52は受信信号RSまたは0VのいずれかをAD変換部68の二つのAD変換器72、74に供給する。被補正データ生成部86は、AD変換部68が受信信号RSをAD変換した結果に基づき、読出データRDを生成する。オフセットデータ生成部76は、AD変換部68が基準電圧をAD変換した結果に基づき、AD変換器72、74毎の測定誤差を表すオフセットデータAZ1、AZ2を生成する。補正部100は、読出データRDからオフセットデータAZ1、AZ2分を除去する補正処理を実行し、サンプリングデータSDを生成する。

(もっと読む)

アナログユニット

【課題】コストアップを抑制しつつ、温度ドリフトに対する出力値を補正することが可能なアナログユニットを提供する。

【解決手段】入力値を出力値に変換する変換回路12と、前記変換回路の温度が初期状態から定常状態に至る間の2つの時点における前記入力値と出力値との関係を示す設定値を記憶する記憶部14と、前記記憶部に記憶された設定値に基づいて、前記変換回路の出力値を校正する校正部13とを備え、時間経過に基づいて設定値を補間する。

(もっと読む)

逐次比較型AD変換器および無線受信機

【課題】容量DA変換器を駆動するドライバを低消費電力化しつつ、低誤差のAD変換を行う。

【解決手段】バイナリ重み型容量DA変換器は、アナログ入力信号と、参照電圧とに基づき、Nビットの各ビットに対応するサイクル毎に、残差信号を生成する。第1比較器は、前記サイクル内の第1の時点における前記残差信号を、所定電圧と比較して、論理値を表す第1比較結果を得る。レジスタは、前記第1比較結果を保持する。第2比較器は、前記サイクル内における前記第1の時点より後の第2の時点における前記残差信号を、前記所定電圧と比較して、論理値を表す第2比較結果を得る。誤り判定回路は、前記第1比較結果が前記第2比較結果と異なるとき、誤り検出信号を発生させる。誤り訂正回路は、前記誤り判定回路により前記誤り検出信号が発生させられたとき、前記レジスタから読み出し第1比較結果を反転して出力する。

(もっと読む)

データ処理装置、データ処理システム及び電力量計

【課題】増幅回路を用いてAD変換の分解能を拡大するAD変換技術において増幅回路のゲインに対する校正精度を向上させる。

【解決手段】目的ゲイン2n(nは正の整数)に対する前記増幅回路の実際のゲインを実測ゲインとして計測するゲインキャリブレーション処理を行い、アナログ信号を増幅回路で増幅してからAD変換回路で変換してビット拡張された変換データを取得する拡張AD変換処理において、前記増幅回路で増幅してから前記AD変換回路で変換して得られるデータに前記実測ゲインに対する前記目的ゲイン2nの比に応じた操作を施すことによってゲインに起因する誤差を相殺する。前記ゲインキャリブレーション処理では、デジタル的に既知の校正データに応ずる校正信号を目的ゲイン2n倍した信号のAD変換結果に対して、上記校正データをN倍した信号を増幅せずにAD変換して当該変換結果の1/Nの値を用いて、前記実測ゲインを求める。

(もっと読む)

歪み補正装置

【課題】小面積および低消費電力な、A/D変換器の歪み補正装置を提供する。

【解決手段】本発明の一態様としての歪み補正装置は、第一A/D変換器と、第二A/D変換器と、べき乗器と、適応相関制御手段と、歪み除去手段とを備える。前記第一A/D変換器は、第一入力信号をA/D変換して第一変換信号を得る。前記第二A/D変換器は、第二入力信号をA/D変換して第二変換信号を得る。前記第二入力信号は、前記第一入力信号の振幅を低減した信号、または前記第一入力信号は、前記第二入力信号の振幅を増大した信号である。前記べき乗器は、前記第二変換信号をn乗(nは2以上の整数)することにより、べき乗信号を得る。前記適応相関制御手段は、前記べき乗信号と、前記第二変換信号に基づき適応相関制御を行うことにより、前記べき乗信号に含まれるn乗成分である歪み信号を生成する。前記歪み除去手段は、前記第一変換信号から、前記適応相関制御手段で生成された歪み信号を除去する。

(もっと読む)

半導体集積回路装置

【課題】レベル変換回路のレイアウト面積の縮小を図る。

【解決手段】半導体集積回路装置(10)は、レベル変換回路(14)と、D/A変換回路(12)とを備える。このとき、パラレル形式のデジタル信号をシリアル形式に変換して上記レベル変換回路に供給するためのパラレル・シリアル変換回路(15)と、上記レベル変換回路の出力をパラレル形式のデジタル信号に変換して上記D/A変換回路に供給するためのシリアル・パラレル変換回路(13)とを設ける。上記レベル変換回路は、シリアル形式のデジタル信号に対応するレベル変換機能を備えていれば良く、パラレル形式のデジタル信号に対応させる場合に比べて、レベル変換回路のレイアウト面積を縮小することができる。

(もっと読む)

テスト回路

【課題】アナログデジタル変換器の微分直線性を小規模な回路構成に基づいて検査できるようにすること。

【解決手段】テスト回路は、アナログデジタル変換器から出力された第1のデジタル値を格納する第1のレジスタと、アナログデジタル変換器から出力された第2のデジタル値を格納する第2のレジスタと、第1のレジスタに格納された第1のデジタル値と第2のレジスタに格納された第2のデジタルとの差分値を算出する差分算出器と、差分値が所定の上限値と所定の下限値との間に含まれる否かを判定し、判定結果を出力する比較判定器と、を備えている。

(もっと読む)

ADC

【課題】アナログ入力信号に対する周波数の制限を抑制したバックグランドキャリブレーションを行うADCとその補正回路を提供する。

【解決手段】アナログ入力信号をサンプリング周波数(以下fs)でサンプリングしてデジタル出力信号に変換するADCであって,アナログ入力信号をタイムインタリーブでデジタル出力信号に変換するN個のアナログデジタル変換(以下ADC)チャネルと,N個のADCチャネルがそれぞれ出力するチャネルデジタル信号を合成して前記デジタル出力信号を生成するチャネル合成器と,N個のADCチャネルの少なくとも一つの出力に設けられた適応フィルタと,デジタル出力信号に応じて前記適応フィルタの係数を生成する補正回路とを有し,補正回路は,デジタル出力信号に含まれるアナログ入力信号成分と誤差に対応するイメージ信号成分のうち,イメージ信号成分の直流成分を演算し,直流成分に基づいて当該直流成分が抑制されるように前記係数を演算する。

(もっと読む)

電流制御用半導体素子およびそれを用いた制御装置

【課題】ゲインa、およびオフセットbの変動を動的に補正することで、1チップのIC内で高精度な電流検出が可能な電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】

同一半導体チップ上に、トランジスタ4と、電流−電圧変換回路22とADコンバータ23とを有する。参照電流生成回路6,6’は、負荷2の電流に電流パルスIcを重畳して、ADコンバータが出力する電圧デジタル値を変動させる。ゲインオフセット補正部8は、参照電流生成回路6,6’による電圧デジタル値の変動を信号処理して、ADコンバータ23が出力する電圧デジタル値と負荷の電流デジタル値の線形関係式におけるゲインa,a’及びオフセットb,b’を動的に取得する。電流デジタル値演算部12は、ゲインオフセット補正部8により取得されたゲイン及びオフセットを用いて、ADコンバータが出力する電圧値を補正する。

(もっと読む)

確率的A/D変換器及び確率的A/D変換器を用いる方法

【課題】高精度で低電力のアナログ−デジタル変換器回路を提供する。

【解決手段】アナログ−デジタル変換器回路は、アナログ入力信号1を受信し、変換ビットの第1のセット3と第1の完了信号7とアナログ入力信号及び変換ビットの第1のセットにより表された信号の間の差を表す残差アナログ出力信号4とを発生する第1の変換器ステージ2と、第1の完了信号を受信しクロック信号を発生するクロック発生回路8と、各々が残差アナログ出力信号及び共通参照電圧を受信するよう構成されクロック信号により動作されて複数の比較器決定を出力する複数の比較器と、複数の比較器決定を受信し変換ビットの第2のセットを発生するデジタル処理ステージとを備える第2の変換器ステージ9と、変換ビットの第1及び第2のセットを組み合わせることにより、アナログ入力信号のデジタル表現を発生する手段とを備える。

(もっと読む)

逐次比較型AD変換方法および装置

【課題】システム全体でのオフセット補償とダイナミックレンジの確保を可能とするAD変換装置を提供する。

【解決手段】ブリッジセンサB1から非測定検出信号が入力するとき、第1のサイクルにおいて、高利得差動増幅器2の基準電圧VCOMとして初期値をセットして、逐次比較型AD変換本体部3でAD変換データを求める。・・・。第m(mは3以上の正の整数)のサイクルにおいて、第m−1のサイクルで得られたAD変換データの最上位ビットに応じて、AD変換データが零値に近づくように、基準電圧VCOMとして、第m−1の電圧を所定電圧だけ上昇又は下降させた第mの電圧をセットする。センサB1から実測定検出信号が入力するとき、基準電圧VCOMとして第mの電圧をセットしてAD変換データを求める。

(もっと読む)

データ処理システム

【課題】比較的簡単な構成により分解能を向上させ回路特性の誤差の影響を縮減してDA変換を行う。

【解決手段】夫々に校正データを与えた複数個のDA変換回路(DAC1,DAC2)の出力を所定の重みをつけて前記加算回路(2)で加算し、前記加算回路の出力を前記AD変換回路でデジタル値に変換し、変換されたデジタル値に基づいて所定の重みに許容外の誤差があることを判別したときは、当該誤差の影響を縮小する方向に変換対象のデジタル信号を補正するための補正係数を取得する校正処理を制御する。変換対象のデジタル信号を高精度にアナログ信号に変換するときは、変換対象のデジタル信号を前記補正係数を用いて補正して前記複数個のDA変換回路に与え、これによるDA変換出力を前記加算回路で加算する。

(もっと読む)

信号入力回路の診断方法および装置

【課題】入力信号の電圧と基準電圧を選択してデジタル値に変換し、このデジタル値から故障箇所を特定する信号入力回路の診断装置では、診断項目を増やすと構成が複雑になり、かつ異常箇所を特定できなかった。本発明は簡単な構成で異常箇所を特定できる診断装置を提供することを目的にする。

【解決手段】マルチプレクサを用いて入力信号電圧、基準電圧、基準電圧を極性反転した電圧、同じ信号の差電圧を測定し、これらの電圧値から異常を診断するようにした。簡単な構成で種々の異常を検出でき、また故障箇所を特定できる。

(もっと読む)

AD変換回路および撮像装置

【課題】アナログ信号の減算を行うことができるAD変換回路および撮像装置を提供する。

【解決手段】ランプ部19は、時間の経過とともに増加または減少する参照信号を生成する。比較部109は、AD変換の対象となるアナログ信号と参照信号とを比較し、参照信号が前記アナログ信号に対して所定の条件を満たしたタイミングで比較処理を終了する。主カウント部18はカウントを行い、カウント値を出力する。ラッチ部108は、第1のアナログ信号に係る比較処理の終了に応じた第1のタイミングで第1のカウント値をラッチした後、第2のアナログ信号に係る比較処理の終了に応じた第2のタイミングで第2のカウント値をラッチする。列カウント部103は、ラッチ部108に保持された第1のカウント値を構成する各ビットの値に基づいて初期値を設定した後、ラッチ部108に保持された第2のカウント値を構成する各ビットの値を順次カウントする。

(もっと読む)

DA変換装置

【課題】より高精度でビット拡張ができるDA変換装置を提供する。

【解決手段】DA変換装置12は、2m個のnビットのDAコンバータ14と、このDAコンバータ14からの出力を加算する演算器16と、前記DAコンバータに入力するnビットの中間データを生成するデータプロセッサ12と、を備えている。データプロセッサは、各DAコンバータ14の中間データとして、入力データの上位nビットデータに、補正値を付加したデータを生成する。補正値は、その総和が、入力データの下位mビットデータが示す値に等しくなるように設定される。

(もっと読む)

ADコンバータ、及び、電子装置

【課題】変換精度の高いADコンバータ、及び、電子装置を提供する。

【解決手段】ADコンバータは、第1ビット数分の第1キャパシタで保持するデジタル信号をアナログ変換して得る残差信号を出力する第1DA変換部10と、第2ビット数分の第2キャパシタで保持するデジタル信号をアナログ変換して得る残差信号を出力する第2DA変換部150と、第1DA変換部が出力する残差信号を増幅して第2DA変換部に転送する増幅部140と、第1DA変換部が出力する残差信号と所定の基準レベルとの第1比較結果と、第2DA変換部が出力する残差信号と所定の基準レベルとの第2比較結果とを表す二値信号を出力する比較部120と、第1比較結果を表す二値信号を第1DA変換部に入力するとともに、第2比較結果を表す二値信号を第2DA変換部に入力する逐次制御部130とを含み、第2DA変換部の第2キャパシタは、増幅部のキャパシタと共用である。

(もっと読む)

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

AD変換装置および信号処理システム

【課題】ダイナミックレンジが歪みで制限されるAD変換の特性を大幅に改善することが可能なAD変換装置および信号処理システムを提供する。

【解決手段】アナログ信号をデジタル信号に変換する第1のAD変換器と、係数αでα倍したアナログ信号をデジタル信号に変換する第2のAD変換器と、制御変数信号に応じて第1のAD変換器の第1の出力信号の非線形性歪みを補償する第1の非線形補償部と、制御変数信号に応じて第2のAD変換器の第2の出力信号の非線形性歪みを補償する第2の非線形補償部と、非線形性歪みを曲率として、第1の非線形補償部による第1の信号および第2の非線形補償部による第2の信号の変化の割合に基づき入力アナログ信号の信号強度に依存する曲率を推定し、曲率部分を打ち消すように制御変数信号を生成して第1の非線形補償部および第2の非線形補償部に出力する非線形検出部とを有する。

(もっと読む)

試験測定装置及び信号デジタル化方法

【課題】ノイズを減らしながら広帯域入力信号をデジタル化する。

【解決手段】スプリッタ10は、特定帯域幅を有する入力信号12を複数の分配信号14及び16へと分配する。高調波ミキサ18及び24は、分配信号14及び16の夫々を、関連する高調波信号20及び26と混合し、関連する混合信号22及び28を生成する。デジタイザ30及び32は、夫々の混合信号22及び28をデジタル化する。高調波ミキサ18及び24に関する高調波信号の少なくとも1つの1次高調波は、デジタイザ30及び32の少なくとも1つの有効サンプル・レートと異なっている。

(もっと読む)

AD変換装置および信号処理システム

【課題】ダイナミックレンジが歪みで制限されるAD変換の特性を大幅に改善することが可能なAD変換装置および信号処理システムを提供する。

【解決手段】アナログ信号をデジタル信号に変換する第1のAD変換器と、係数αでα倍したアナログ信号をデジタル信号に変換する第2のAD変換器と、制御変数信号に応じて第1のAD変換器の第1の出力信号の非線形性歪みを補償する第1の非線形補償部と、制御変数信号に応じて第2のAD変換器の第2の出力信号の非線形性歪みを補償する第2の非線形補償部と、非線形性歪みを曲率として、第1の非線形補償部による第1の信号および第2の非線形補償部による第2の信号の差分に基づき入力アナログ信号の信号強度に依存する曲率を推定し、曲率部分を打ち消すように制御変数信号を生成して第1の非線形補償部および第2の非線形補償部に出力する非線形検出部とを有する。

(もっと読む)

21 - 40 / 522

[ Back to top ]