Fターム[5J034AB00]の内容

半導体素子を用いたパルス発生器 (1,143) | 目的、効果 (486)

Fターム[5J034AB00]の下位に属するFターム

温度補償 (6)

電源変動補償 (15)

低消費電力 (134)

高速化 (94)

集積化、小型化 (61)

ノイズ(α線を含む)対策 (46)

出力レベルの安定化 (38)

振幅制御 (4)

波形なまり除去 (1)

入力感度の向上 (4)

他の回路機能を共用 (13)

ヒステリシス特性を有するもの

セット優先/リセット優先 (10)

初期動作設定 (21)

レーシング防止 (1)

Fターム[5J034AB00]に分類される特許

1 - 20 / 38

ラッチ回路および表示装置

【課題】ドレインアバランシェ効果を抑圧し、信頼性を向上させることが可能となるラッチ回路を提供する。

【解決手段】ゲートに前記走査電圧が入力されたときに、「0」あるいは「1」のデータに対応する電圧を取り込む入力トランジスタと、他端に容量制御信号が入力されるとともに、一端が前記入力トランジスタの第2電極に接続され、前記入力トランジスタで取り込まれた電圧を保持する保持容量と、ゲートが前記入力トランジスタの第2電極に接続され、第2電極が第1出力端子に接続されるとともに、第1電極に第1ラッチ制御信号が入力される第1導電型の第1トランジスタと、ゲートが前記第1トランジスタの第2電極に接続され、第2電極が第2出力端子に接続されるとともに、第1電極に第2ラッチ制御信号が入力される第2導電型の第2トランジスタとを備える。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバI

Cの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化

を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジス

タを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電

位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック

信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力

することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給

する。

(もっと読む)

ラッチ回路、分周回路、フリップフロップ回路、PLL回路、マルチプレクサ及び半導体集積回路

【課題】CMLレベルのデータを出力するラッチ回路を使用した分周回路の出力をCMOSレベルで扱うためにはレベル変換が必要となる。そのため、CMLレベルのクロックを受け付け、CMOSレベルのデータを出力することで、回路規模及び消費電力の抑制を実現するラッチ回路が望まれる。

【解決手段】ラッチ回路では、差動入力データを受け付けるNチャンネル型MOSトランジスタのドレイン端子とPチャンネル型MOSトランジスタのゲート端子にクロスして接続している。このようにして、CMLレベルのデータをCMOSレベルのデータに変換する。

(もっと読む)

ラッチ回路及び半導体装置

【課題】新規のラッチ回路を提供すること。

【解決手段】ラッチ回路は、酸化物半導体(OS)によってチャネル領域が形成されるトランジスタ10を有し、出力端子(Q端子)並びにトランジスタ10のソース及びドレインの一方に電気的に接続され、且つトランジスタ10がオフ状態となることによって浮遊状態となるノード11においてデータを保持する。なお、当該酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。このような酸化物半導体によってトランジスタのチャネル領域が形成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。

(もっと読む)

ラッチ回路およびラッチ回路を用いた表示装置

【課題】比較的短い時間間隔で、ラッチ情報をラッチすることが可能で、より低コスト化を図ることが可能となる単チャンネルラッチ回路を提供する。

【解決手段】入力トランジスタと、前記入力トランジスタの第2電極と第1ラッチ制御線との間に接続される保持容量と、第1電極が前記第1ラッチ制御線に接続され、ゲートが前記入力トランジスタの第2電極に接続される第1トランジスタと、ゲートが前記第1トランジスタの第2電極に接続され、第1電極が第2ラッチ制御線に接続される第2トランジスタと、ゲートが前記第1トランジスタの第2電極に接続され、第1電極が前記第2トランジスタの第2電極に接続されると共に、第2電極が出力端子に接続される第3トランジスタと、前記第1トランジスタの第2電極と前記第2トランジスタの第2電極との間に接続される容量と、前記第1トランジスタの第2電極と前記第1ラッチ制御線との間に接続されるダイオードとを有する。

(もっと読む)

低漏出のデータ保持回路を有する集積回路およびその方法

【課題】本発明は、低漏出のデータ保持回路のためのシステム及び方法を提供する。

【解決手段】集積回路は、第1の回路と、スリープトランジスタ回路とを有する。第1の回路は、入力信号を受信して、その入力信号を処理する。第1の回路は、また、漏れの少ないスリープ状態でデータを保持する。スリープトランジスタ回路は、第1の回路へ結合されており、負の電圧を有するスリープ信号を受信する。スリープ回路は、第1の回路でデータを保持している間、スリープ信号に基づいて、漏れが少なくなるようスリープ状態で第1の回路の電力消費を低減する。

(もっと読む)

設計装置

【課題】消費電力を低減し、誤動作を防止することができるフリップフロップ回路を設計するための設計装置を提供することを課題とする。

【解決手段】第1の入力信号、第1のイネーブル信号及び第1のクロック信号を入力する第1のフリップフロップ回路の第1の設計データに対して、第1のクロック信号の周波数の2倍以上の周波数のクロック信号で第1の静的タイミング解析を行う第1の静的タイミング解析部(S11)と、第1の静的タイミング解析の結果が合格の場合には、第1の設計データを入力し、第1のフリップフロップ回路を第2のフリップフロップ回路に変換した第2の設計データを生成する第1の変換部(S13)とを有し、第1のフリップフロップ回路はクロックゲーティング回路を有さず、第2のフリップフロップ回路はクロックゲーティング回路を有する設計装置が提供される。

(もっと読む)

差動論理回路、分周回路、及び周波数シンセサイザ

【課題】動作電流を変えても直流出力電圧の変わらない差動論理回路及び分周回路、さらには、周波数シンセサイザにおける動作電流の調整方法を提供する。

【解決手段】複数対の差動論理信号を入力し論理演算を行ってその結果を一対の差動信号出力端子から出力する差動論理部と、差動論理部に電流を供給する電流源回路であって前記電流の大きさが制御可能な電流源回路と、差動信号出力端子に接続された負荷回路と、負荷回路に接続され、一対の差動信号出力端子の直流出力電圧が一定の電圧になるように負荷回路の負荷を制御する負荷制御回路と、を備える。

(もっと読む)

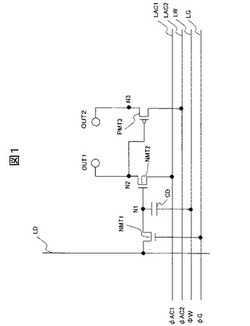

データ取込保持装置

【課題】入力データの取り込みを誤りなくできるデータ取込保持装置を提供する。

【解決手段】パルス発生手段20からのラッチ用パルスPLSのパルス幅区間で入力データを取り込んで保持する第1のデータ取込記憶部を備える保持手段を備える。パルス発生手段20は、第1のデータ取込記憶部と同じあるいは同等の構成の第2のデータ取込記憶部231を備え、クロック信号CLKから、第2のデータ取込記憶部231における入力データの取込時間分のパルス幅区間のパルス信号PLSを生成し、ラッチ用パルスとして、第1のデータ取込記憶部に供給する。

(もっと読む)

半導体集積回路装置

【課題】小さい面積で十分な遅延時間を確保する。

【解決手段】 入力に基づいて充電点に充電を行う第1のトランジスタと前記入力に基づいて放電点から放電を行う第2のトランジスタとにより構成される第1のインバータ(PT21,NT21)と、前記充電点と前記放電点との間に、ドレイン・ソース路が並列に設けられたP型の第3のトランジスタ及びN型の第4のトランジスタ(PT22,NT22)と、前記充電点又は前記放電点の電位を反転させて前記第3及び第4のトランジスタのゲートに供給して、前記充電点又は前記放電点から前記入力の遅延信号を得る第2のインバータ(INV21)とを具備したことを特徴とする。

(もっと読む)

リセットセットフリップフロップ回路

【課題】出力信号に発生するスキューを防止することができるリセットセットフリップフロップ回路を提供すること

【解決手段】本発明にかかるリセットセットフリップフロップ回路は、電源110と出力端子310の間に設けられたスイッチ101と、接地111と出力端子310の間に設けられたスイッチ102と、電源110と前記出力端子311の間に設けられたスイッチ103と、接地111と出力端子311の間に設けられたスイッチ104を備える。各スイッチは、制御回路200のセット入力に入力される信号がハイレベルでありかつリセット入力に入力される信号がロウレベルである場合は、スイッチ101とスイッチ104をオン状態に制御する。セット入力に入力される信号がロウレベルでありかつリセット入力に入力される信号がハイレベルである場合は、スイッチ102とスイッチ103をオン状態に制御する。

(もっと読む)

多数決回路付きフリップフロップ回路

【課題】ソフトエラーに対する耐性向上と回路規模の縮小を両立させることができない。

【解決手段】クロック調整回路7は、入力クロック信号CLKのハイ状態とロウ状態の比

率を、1つのマスタラッチ1のデータ保持時間帯を狭めるように調整し、ハイ状態(マスタラッチ1のデータ保持時間)を可及的に狭めて出力する。インバータ6はクロック調整回路7の出力を極性反転する。マスタラッチ1のトランスファーゲート4およびスレーブラッチ2−1〜2−3のトランスファーゲート5−1〜5−3は、クロック調整回路7およびインバータ6の出力により、データの通過を制御する。スレーブラッチ2−1〜2−3の出力は3入力多数決回路3で多数決をとられた後に出力信号Qとなる。

(もっと読む)

スキャン・テスト・サポートを有する低電力デュアル・エッジ・トリガ型記憶セル及びそのためのクロック・ゲーティング回路

【課題】SET回路用の既存の設計及びテストツール内で容易に使用することができ、スキャン・テストをサポートし、プロセッサチップ上で小さいスペースしか占有せず、使用時に少ない電力しか消費しない、DET記憶セルを提供すること。

【解決手段】パルス発生器(5)と記憶素子(6)とを有する記憶セル(1)が提供される。記憶素子入力(7)は、データ入力信号(DIN)を受信するように接続される。記憶素子出力(9)は、データ出力信号(DOUT)を提供するように接続される。記憶素子(6)は、パルス発生器(5)から受信した記憶制御信号(SC)に応答して、データ保持状態及びデータ転送状態のうちの一方で動作可能である。パルス発生器(5)は、立ち上がり及び立ち下がりクロック信号エッジ(13、14)を有するクロック信号(CK)を受信するように接続され、かつ、記憶制御信号(SC)内に制御パルス(15、16)を提供するように構成される。各制御パルス(15、16)は、リーディング・エッジ(17)及びトレーリング・エッジ(18)を有する。制御パルス(15、16)は、そのリーディング・エッジ(17)上でデータ転送状態を起動するのに適した極性を有する。新規な特徴は、パルス発生器(5)が、立ち上がりクロック信号エッジ(13)を受信したときに立ち上がりエッジ制御パルス(15)を始動し、立ち下がりクロック信号エッジ(14)を受信したときに立ち下がりエッジ制御パルス(16)を始動するように構成されたことである。このようにすることで、組合せ論理回路、及び、1つのレベル型又はシングル・エッジ・トリガ型記憶素子(6)のみを用いて、デュアル・エッジ・トリガ型フリップフロップを作ることができる。記憶セル(1)は、低電力消費であり、スキャン・テストを容易にし、広範囲な設計ツール及びテスト装置で用いることができる。

(もっと読む)

ラッチ回路及びデータの読み出し方法

【課題】不揮発であってデータ読み出し動作の信頼性の向上が図れるラッチ回路を提供する。

【解決手段】ラッチ回路は、インバーター回路110,120と、インバーター回路110の出力とインバーター回路120の入力とを接続するスイッチ162と、インバーター回路120の出力とインバーター回路110の入力とを接続するスイッチ164と、インバーター回路110の入力に一端が接続されかつインバーター回路110の出力に他端が接続された強誘電体キャパシター132と、インバーター回路120の入力に一端が接続されかつインバーター回路120の出力に他端が接続された強誘電体キャパシター134と、インバーター回路110の入力と強誘電体キャパシターの一端との間のノードに一端が接続されたキャパシター142と、インバーター回路120の入力と強誘電体キャパシター134の一端との間のノードに一端が接続されたキャパシター144とを含む。

(もっと読む)

ラッチ型コンパレータ及びこれを用いた多値論理復調回路

【課題】製造プロセスのマージンを削ることなく、オフセットの補正が可能なラッチ型コンパレータ、及びこれを用いた、オフセットの補正が可能な多値論理の復調回路を提供する

【解決手段】本発明によるラッチ型コンパレータは、クロスカップルされた2つのCMOSインバータからなるフリップフロップを含み、フリップフロップの4個のトランジスタの各々のソースと電源/接地間には伝達トランジスタを介して抵抗と設定電流可変の定電流源が接続され、フリップフロップの差動出力は各々伝達トランジスタを介して差動入力に接続され、全ての伝達トランジスタのゲートは、差動クロック入力のいずれかに接続されていることを特徴とする。

(もっと読む)

改良クロック・ゲーティング・セルを用いるシステム、及び方法

【解決手段】クロック・ゲーティング・セルは、入力イネーブル・ロジック及び出力ロジック回路と接続しているラッチを備え、ラッチは、出力ロジック回路の入力ノードでプル・アップ及び/またはプル・ダウン回路、及びクロック・ゲーティングセルが有効である場合、プル・アップ及び/またはプル・ダウン回路によって、出力ロジック回路入力ノードの早期充電または早期放電を防止する回路を備えている。 (もっと読む)

信号シフト装置、シフトレジスタ、電子機器及び信号シフト装置の駆動方法

【課題】信号シフト装置、シフトレジスタ及び電子機器において、安定した動作制御を行う。

【解決手段】シフト回路21_kは、電圧適正化回路22を備える。閾値電圧検出部32は、トランジスタT14のゲート閾値電圧Vthを検出し、閾値電圧保持部33は、このゲート閾値電圧Vthを保持する。電圧加算部34は、(N+1)端子に供給されたS(N+1)信号によってコンデンサC21,C22の容量に応じた電圧をゲート閾値電圧Vthに加算してトランジスタT14がオンするためのゲート電位を生成する。

(もっと読む)

ラッチ構造、周波数分周器、及びそれらを動作させる方法

ラッチは、3つの回路を含んでいる。第1の回路は、第1の入力(D)及び第1のクロック位相(CK)がともにロウであるときに第1の出力(QB)を第1のレベルに、D及びCKがともにハイであるときに第2のレベルに駆動し、異なったロジックレベルがD及びCKに印加されたときにハイインピーダンス(HI−Z)を与える。第2の回路は、第3の入力(DB)及び相補的クロック位相(CKB)がともにロウであるときに第2の出力(Q)を第1のレベルに、DB及びCKBがともにハイであるときに第2のレベルに駆動し、異なったロジックレベルがDB及びCKBに印加されたときにHI−Zを与える。第3の回路は、第1及び第2の回路がQ及びQBにHI−Zを与えるときにQ及びQBの電圧を維持する。そのようなラッチで構成された奇数ドライバは、出力パルス幅を入力期間の整数倍に限定することなく、50%デューティサイクル動作を生成する。  (もっと読む)

(もっと読む)

フリップフロップ回路

【課題】遅延時間の非対称性を無くし且つ入力から出力までの遅延時間を短縮したフリップフロップ回路を提供する。

【解決手段】フリップフロップ回路は、差動入力信号及び差動クロック信号に応じて互いに相補関係にある第1の信号及び第2の信号と互いに相補関係にある第3の信号及び第4の信号とを出力するマスターラッチであるクロックドアンプと、第1乃至第4の信号に応じて2つの出力信号を出力するシンメトリックスレーブラッチとを含むことを特徴とする。

(もっと読む)

フリップフロップ回路、フリップフロップ回路を用いた周波数分周器、周波数分周器を用いた通信装置や電子機器

【課題】電流論理型のフリップフロップ回路を利用した周波数分周器において、装置において、高速動作と広い動作周波数範囲のトレードオフ関係を緩和する。

【解決手段】ラッチペア部Lを第1ラッチペア部L1と第2ラッチペア部L2に分ける。第2ラッチペア部L2に対しては、動作電流制御部CCを設ける。動作電流制御部CCは、クロック CLKの周波数が低いほど第2ラッチペア部L2に対する動作電流を増やすように制御する。第3のスイッチSW3がオフ時には、この電流制御による変動分を相殺するように、動作電流均衡制御部BCは、第1ラッチペア部L1やサンプルペア部Sに対する動作電流を低減することで、データの出力振幅が一定となるようにする。

(もっと読む)

1 - 20 / 38

[ Back to top ]