Fターム[5J039KK15]の内容

Fターム[5J039KK15]に分類される特許

1 - 20 / 27

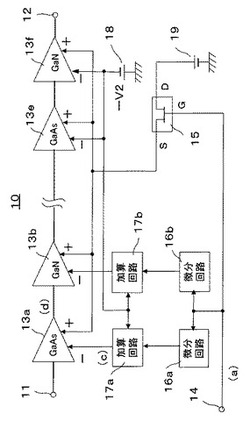

パルス電力増幅装置

【課題】熱時定数による増幅利得の時間的な変化を補償でき、良好な直線性を有するパルス増幅装置を提供する。

【解決手段】パルス電力増幅装置10は、高周波信号を変調するパルス信号を入力され、前記パルス信号を入力され第1の増幅器の熱時定数に対応する時定数を有する第1の微分回路と、前記パルス信号を入力され第2の増幅器の熱時定数に対応する時定数を有する第2の微分回路と、励振回路及び最終段増幅器の入力側の負バイアス端子に供給される負バイアス電圧を出力する負バイアス電源18と、この負バイアス電源の出力する負バイアス電圧に前記第1の微分回路の出力を加算して前記第1の増幅器の入力側の負バイアス端子に供給する第1の加算回路と、前記負バイアス電源の出力する負バイアス電圧に前記第2の微分回路の出力を加算して前記第2の増幅器の入力側の負バイアス端子に供給する第2の加算回路と、を有する。

(もっと読む)

動作クロック生成装置、動作回路、及び、画像形成装置

【課題】少なくとも動作クロックの立ち上がりまたは立ち下がりのタイミングが所望のスペクトラム拡散クロックの周波数である動作クロックを生成する動作クロック生成装置、並びに、その動作クロック生成装置を用いた動作回路及び画像形成装置の提供。

【解決手段】基準クロックを計数したカウンタ値の増加に応じて、その基準クロックの立ち上がりタイミングを(A)に示す遅延量tr0〜tr23で遅延補正し、立ち下がりタイミングを(B)に示す遅延量tf0〜tf23で遅延補正した動作クロックを出力する。カウンタ値が1つ増加する間の遅延量trの各増減幅が、EMIを十分に抑制可能な所望の第1スペクトラム拡散クロックにおいて各クロックの立ち上がりタイミングが取る各周波数にそれぞれ相当する値となるように、遅延量tr0〜tr23を設定している。遅延量tf0〜tf23も、所望の第2スペクトラム拡散クロックに応じて設定している。

(もっと読む)

TDC回路

【課題】解像度が小さく測定精度が高い時間測定を行うことができるTDC回路を提供する。

【解決手段】TDC回路1は、共通の構成を有する32個の単位セル110〜1131がリング状に接続されたリング部10等を備える。単位セル11は、第1インバータ回路111,第2インバータ回路112,スイッチSW0,スイッチSW1およびスイッチSW2を含む。第1インバータ回路111のPMOSトランジスタのゲート幅は、第2インバータ回路112のPMOSトランジスタのゲート幅のαp倍である。第2インバータ回路111のNMOSトランジスタのゲート幅は、第1インバータ回路112のNMOSトランジスタのゲート幅のαn倍である。αpおよびαnの双方が1より大きいか又は双方が1より小さい。

(もっと読む)

多相クロック生成回路

【課題】N相から2N相に切り替わったときに位相関係が不適切にならないようにする。

【解決手段】多相クロック生成回路は,基準クロックに同期して0°,90°の位相の中間クロックを生成する第1の分周器と,0°の中間クロックに同期して0°,90°の位相の第1群の出力クロックを生成する第2の分周器と,90°の中間クロックに同期して45°,135°の位相の第2群の出力クロックを生成する第3の分周器と,第1の分周器と第3の分周器との間に設けられ,切替信号に応じて,90°の中間クロックまたは固定値のいずれかを第3の分周器に供給するセレクタとを有する。さらに,切替信号が2N相モードのときに,第1群の出力クロックと第2群の出力クロックの位相関係にエラーがあるか否かを検出するエラー検出回路と,エラー検出回路がエラーを検出したときに基準クロックと非同期のタイミングで2N相モードの切替信号をセレクタに出力する再リセット回路とを有する。

(もっと読む)

パルス生成回路およびミュート装置

【課題】 矩形波信号の立ち上がりエッジおよび立ち下がりエッジを検出し、一方のレベルのパルス信号を生成するパルス生成回路において、トランジスタの数を削減すること。

【解決手段】 立ち下がりエッジ検出部2は、矩形波信号の立ち下がりエッジを検出し、所定時間だけ、トランジスタQ1をオン状態に制御する。立ち上がりエッジ検出部は、矩形波信号の立ち上がりエッジを検出し、所定時間だけ、トランジスタQ2をオン状態に制御する。トランジスタQ1は、立ち下がりエッジ検出部2が矩形波信号の立ち下がりエッジを検出した時から所定時間、および、トランジスタQ2がオン状態である期間に、オン状態になり、ハイレベルのパルスを出力する。

(もっと読む)

周波数−電圧変換回路及び半導体集積回路装置

【課題】リニアリティ(直線性)の良好な周波数−電圧変換回路を提供すること。

【解決手段】周波数−電圧変換回路は、クロック信号を受信する微分回路と、微分回路の出力を受けてパルス波として出力するバッファ回路と、バッファ回路から出力されたパルス波を直流電圧に変換する積分回路と、クロック信号をゲート端子で受信するとともに、ソース端子が接地端子に接続され、ドレイン端子が微分回路の出力端子に接続されたMOSトランジスタと、を備えている。

(もっと読む)

デジタル信号入力装置

【課題】動作が安定するとともに、後段に接続されるCMOSのLSIの安定な動作を実現するデジタル信号入力装置を提供する。

【解決手段】外部から入力された信号を増幅する増幅部と、前記増幅部で増幅された信号を波形整形する波形整形部と、オフセット電圧を保持するコンデンサと、前記波形整形部の出力をハイレベル状態に固定するように、前記コンデンサの充電と放電を制御して前記オフセット電圧を決定する制御部とを備える。

(もっと読む)

発振停止検出回路

【課題】保護継電器や監視制御機器の発振回路が停止したときに、発振停止検出回路を安価に構築する。

【解決手段】本発明の発振停止検出回路は、発振回路がクロックの供給の停止を検出するために、クロック信号の変化を検出する微分回路と、微分回路からの信号を立ち上がりに限定するダイオードと、前記出力信号を整形する、パルス整形回路とインバータ回路と、充放電回路と、充放電回路の出力電圧レベルと所定の基準値を比較して、基準値を超えたときに信号出力をすることを特徴とする。

(もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

周波数逓倍遅延ロックループ

【課題】周波数逓倍回路を提供する。

【解決手段】周波数逓倍回路(100)は、遅延ラインとクロック合成回路(TOG)を備える。遅延ラインは、その一端でリファレンスクロック(102)を受けて、一周期に一致した複数の遅延素子(101)からクロックタップ出力を発生させる。クロック合成回路(TOG)は、一対のタップ出力に応答して、各タップ出力から出力クロックパルスの立ち上がり及び立ち下がりエッジを発生させる。出力クロックの周期は入力クロックの周期よりも短い。遅延ラインは、遅延素子(101)の周期に一致するように遅延ロックループに含まれてもよい。所定数の遅延段タップ出力に接続された入力を有し、相補出力を供給する、複数の合成回路セル(TOG)が設けられる。セレクタ(106)は、位相検出器(112)からの選択制御信号に応答して、合成セルの1つに係る一対の相補出力のうちの一方から出力を選択する。

(もっと読む)

電子回路、表示装置、及び電子機器、並びに電子回路の駆動方法。

【課題】順序回路の入力信号及び出力信号の状態を制御し、電子回路の動作不良を抑制する。

【解決手段】順序回路及び制御回路を有する電子回路であり、順序回路は、スタート信号として第1の信号、クロック信号として第2の信号、リセット信号として第3の信号が入力され、入力された第1の信号、第2の信号、及び第3の信号の状態に応じて設定された状態の第4の信号を出力信号として出力し、制御回路は、順序回路に入力される第3の信号の状態を制御する。

(もっと読む)

位相検出回路

【課題】位相ロックループ周波数シンセサイザ設計における、大きな電圧制御発振器範囲(例えば、487MHz)、(例えば)1.2V電力供給電圧、および低い電力消費の要求を達成する。

【解決手段】位相検出回路は、参照信号を受信するように構成された参照入力と、フィードバック経路においてディバイダ回路からの分周信号を受信するように構成されたフィードバック入力と、参照信号と分周信号の間の周波数及び位相関係に従って位相ロックループ内のチャージポンプを制御するための制御パルスを生成するように構成されたパルス生成回路と、を有し、分周信号は、分周信号の周期の半分よりも短い長さを具備するパルスを有し、且つ、パルス生成回路は、分周信号のエッジ及び参照信号のエッジから制御パルスのエッジを定義するように、分周信号のパルスをマスクとして使用して参照信号をマスキングすることにより、制御パルスを生成するように構成されている。

(もっと読む)

光電センサ

【課題】例えば一定の速度で搬送される被検出体の前端部と後端部と区別して、更には被検出体の搬送方向の長さを検出することのできる簡易な構成の光電センサを提供する。

【解決手段】受光器による受光量を微分する微分演算手段と、この微分演算手段にて求められた微分量を第1の閾値と比較して受光量の増大変化の大きい立ち上がりエッジを検出する立ち上がりエッジ検出手段と、前記微分量を第2の閾値と比較して受光量の減少変化の大きい立ち下がりエッジを検出する立ち下がりエッジ検出手段と、前記各エッジ検出手段の出力によってセット・リセットされて立ち上がりエッジの検出時点から立ち下がりエッジの検出時点に至る出力信号、または立ち下がりエッジの検出時点から立ち上がりエッジの検出時点に至る出力信号を生成する出力信号生成手段とを備える。

(もっと読む)

電圧比較器

【課題】消費電流を増加することなく高速化することが可能な電圧比較器の提供。

【解決手段】この発明は、差動増幅回路11、微分回路12、および出力増幅回路13を備えている。差動増幅回路11は、差動入力された信号を差動増幅して出力する。微分回路12は、差動増幅回路11の出力を微分し、この微分出力を出力増幅回路13の定電流トランジスタM7のバイアス電圧に加算する。

(もっと読む)

デジタル制御発振器及びこれを用いた位相同期回路

【課題】発振周波数を線形に近くかつきめ細やかに制御可能なデジタル制御発振器を提供する。

【解決手段】正相発振信号を出力する正端子213と、逆相発振信号を出力する負端子214と、センタータップ210とを有し、正端子とセンタータップとの間の任意の位置に第1の接点211を備え、負端子とセンタータップとの間の第1の接点に対応する位置に第2の接点212を備える差動インダクタ200と、正端子と負端子との間に接続され、第1のデジタル制御コードによってキャパシタンスを2値に変化させる第1の可変キャパシタを複数含む第1の可変キャパシタバンク220と、第1の接点と第2の接点との間に接続され、第2のデジタル制御コードによってキャパシタンスを2値に変化させる第2の可変キャパシタを複数含む第2の可変キャパシタバンク240と、正端子と負端子との間に接続される負性抵抗230とを具備する

(もっと読む)

ドライバ回路

【課題】複雑、大規模な回路構成を必要とすることなく簡単な回路構成で、所望の高域強調信号及び低域強調信号を生成することができ、任意の伝送損失を模擬することができるドライバ回路を提供する。

【解決手段】入力信号に応じた波形の出力信号を出力するドライバ回路10において、入力信号が入力され、入力信号と同一波形の信号を出力信号として出力するメインドライバ14と、入力信号が入力され、入力信号と同一波形の非反転信号と、入力信号を反転した波形の反転信号とからなる差動信号を出力するサブドライバ16と、抵抗28、32(34、38)及び可変容量コンデンサ32(38)により構成され、非反転信号を微分した信号を出力し、反転信号を微分した信号を出力する微分回路と、メインドライバ14の出力信号と非反転信号を微分した信号とを加算した高域強調信号又はメインドライバ14の出力信号と反転信号を微分した信号とを加算した低域強調信号を出力信号として出力する加算部26とを有している。

(もっと読む)

半導体集積回路

【課題】消費電流をあまり増加させることなく、トリミング用保持回路の内容を適時にリフレッシュすることができる半導体集積回路を提供する。

【解決手段】この半導体集積回路は、製造後にトリミングを必要とする回路ブロックを内蔵した半導体集積回路であって、回路ブロックをトリミングするために用いられるトリミングデータを格納する格納回路と、格納回路から読み出されたトリミングデータを保持する保持回路と、保持回路に保持されているトリミングデータの変化を検出して検出信号の論理レベルを変化させる検出回路と、検出回路から出力される検出信号の論理レベルが変化したときに、格納回路から読み出されるトリミングデータによって、保持回路に保持されているトリミングデータを更新するリフレッシュ回路とを具備する。

(もっと読む)

クロック同期システム及び半導体集積回路

【課題】クロック同期システムにおいて、LSIチップの大規模化・高集積化・高密度化に因る物理現象の複雑化に伴いギガ・ヘルツ級の高い周波数を持つ被分周クロックあるいは分周クロックをLSIチップ全面に渡り長距離配線を分配し且つシグナルインテグリティを確保することが困難である。

【解決手段】基準クロックに基づき逓倍クロックを生成する位相同期回路と、逓倍クロックに基づき分周クロックを生成する分周回路と、基準クロックを分周してフレームパルスを生成するフレームパルス生成回路とを備え、前記分周クロックは前記フレームパルスにより位相同期化がなされることを特徴とする。

(もっと読む)

パルス幅検出回路、直流成分キャンセル回路及び受信回路

【課題】受信電流のパルス幅に応じたほぼ正確なパルス幅を持つ受信信号を出力する受信回路を提供すること。

【解決手段】第1フィルタ回路24は、電圧信号VA1を高域通過フィルタを通した第1の成分と、前記電圧信号VA1の低周波成分もしくは直流成分に基づく第2の成分を含む第1の処理信号S1を生成する。第2フィルタ回路25は、第1の処理信号S1を増幅した電圧信号VA2を高域通過フィルタを通した成分からなる第2の処理信号S2を生成する。そして、2値化回路26は、第2の処理信号S2を増幅した電圧信号VA3を2値化して受信信号RXを生成する。

(もっと読む)

逓倍パルス生成装置、逓倍パルス生成方法、画像形成装置、及び画像読取装置

【課題】 駆動対象の一定量駆動が検出される毎に逓倍パルスを生成して出力するにあたり、一定量駆動の検出前後での逓倍パルス周期の不連続性が抑制された、信頼性の高い逓倍パルスを生成することを目的とする。

【解決手段】 エンコーダエッジが検出される度にR個の逓倍パルスを生成する。エンコーダエッジが検出されると、直前のエンコーダエッジ間の実周期を含む過去m個の実周期に基づき、次にエンコーダエッジが検出されるまでの時間間隔(予測周期Te)を予測する。そして、この予測周期Teと、直前のエンコーダ周期間における最終の逓倍パルスの逓倍周期tpRとに基づき、この逓倍周期tpRから今回生成する最終の逓倍パルスの逓倍周期まで、逓倍周期が直線的に変化するように、各逓倍パルスを生成する。これにより、エッジ検出前後での不連続性が抑制され、滑らかに変化する逓倍パルスが得られる。

(もっと読む)

1 - 20 / 27

[ Back to top ]