Fターム[5J039LL00]の内容

パルスの操作 (9,993) | 素子 (83)

Fターム[5J039LL00]の下位に属するFターム

ツェナーダイオード (11)

エサキ(トンネル)ダイオード

その他の特殊なダイオード (3)

TRIAC、SCR、PUT、UJT

特殊なトランジスタ (10)

有接点リレー

超電導素子

パルストランス (4)

その他の特殊な素子 (13)

Fターム[5J039LL00]に分類される特許

1 - 20 / 42

半導体集積回路装置

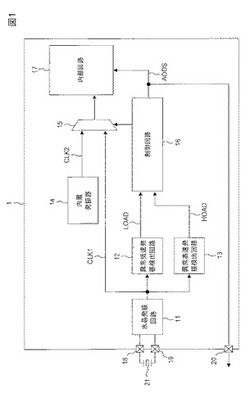

【課題】半導体集積回路装置の内部回路に供給されるクロック信号の周波数が、正常時よりも高くなった場合の上記内部回路の暴走を回避する。

【解決手段】半導体集積回路装置(1)において、内部回路(17)と、水晶振動子を用いた発振動作によりクロック信号を形成する水晶発振回路(11)と、上記内部回路が正常に動作可能な周波数のクロック信号を形成する内蔵発振器(14)とを設ける。また上記水晶発振回路で形成されたクロック信号の周波数が、上記内部回路の正常動作の周波数範囲よりも上昇したことを検出可能な異常高速発振検出回路(13)を設ける。さらに上記異常高速発振検出回路での検出結果に基づいて、上記水晶発振回路で形成されたクロック信号に代えて、上記内蔵発振器で形成されたクロック信号を上記内部回路に供給するための制御回路(16)を設けることで、内部回路の暴走を回避する。

(もっと読む)

時間計測回路およびデジタル位相同期回路

【課題】発振器の周期を基準として発振器の出力信号と基準信号との位相のずれを検出する。

【解決手段】多相化回路2は、差動発振信号P1、P2をM(Mは2以上の整数)分周することにより、位相が互いに180/M度ずつ異なる多相化信号S1〜SNを生成し、フリップフロップF1〜FNは、基準信号RCKの入力に同期して多相化信号S1〜SNをそれぞれ取り込み、デコーダ3は、フリップフロップF1〜FNの出力信号Q1〜QNをデコードする。

(もっと読む)

TDC回路

【課題】解像度が小さく測定精度が高い時間測定を行うことができるTDC回路を提供する。

【解決手段】TDC回路1は、共通の構成を有する32個の単位セル110〜1131がリング状に接続されたリング部10等を備える。単位セル11は、第1インバータ回路111,第2インバータ回路112,スイッチSW0,スイッチSW1およびスイッチSW2を含む。第1インバータ回路111のPMOSトランジスタのゲート幅は、第2インバータ回路112のPMOSトランジスタのゲート幅のαp倍である。第2インバータ回路111のNMOSトランジスタのゲート幅は、第1インバータ回路112のNMOSトランジスタのゲート幅のαn倍である。αpおよびαnの双方が1より大きいか又は双方が1より小さい。

(もっと読む)

位相同期回路、CDR回路及び受信回路

【課題】基準クロックの周波数を低くして消費電力を抑制することのできる位相同期回路を提供する。

【解決手段】第1の位相比較器と第2の位相比較器とに、それぞれ帰還クロックの少なくとも1周期分異なる位相差をつけた分周クロックを入力して基準クロックとの位相比較を行い、受信信号と帰還クロックとの位相比較の結果で第1と第2の位相比較器の出力の重みづけを行い、重みづけされた出力により帰還クロックの位相調節を行う。

(もっと読む)

パルス生成回路およびミュート装置

【課題】 矩形波信号の立ち上がりエッジおよび立ち下がりエッジを検出し、一方のレベルのパルス信号を生成するパルス生成回路において、トランジスタの数を削減すること。

【解決手段】 立ち下がりエッジ検出部2は、矩形波信号の立ち下がりエッジを検出し、所定時間だけ、トランジスタQ1をオン状態に制御する。立ち上がりエッジ検出部は、矩形波信号の立ち上がりエッジを検出し、所定時間だけ、トランジスタQ2をオン状態に制御する。トランジスタQ1は、立ち下がりエッジ検出部2が矩形波信号の立ち下がりエッジを検出した時から所定時間、および、トランジスタQ2がオン状態である期間に、オン状態になり、ハイレベルのパルスを出力する。

(もっと読む)

A/D変換器

【課題】Tr.補間型比較器列を構成要素とし、プリアンプ列が出力する複数の差電圧を補間しつつAD変換するA/D変換器において、前記Tr.補間型比較器列を構成する複数個のTr.補間型比較器のオフセットをキャンセルする。

【解決手段】複数の抵抗R1〜Rmは複数の参照電圧を発生する。複数のサブ抵抗R11〜Rm4は、前記各参照電圧を更に分解する複数のサブ参照電圧を発生させる。キャリブレーション期間では、キャリブレーション対象となるTr.補間型比較器を選択すると共に、この選択されたTr.補間型比較器の閾値電圧に等しいサブ参照電圧をスイッチSW11〜SWm4により選択し、この選択したサブ参照電圧をスイッチSWAIN1、SWAIN2によりアナログ入力信号AINに代えてプリアンプ列102の各プリアンプA1〜Amに入力し、この状態でキャリブレーションを行う。

(もっと読む)

デジタルノイズ保護用回路及び方法

【課題】コンパレータによって生成されたデジタル信号をノイズからの保護方法を提供する。

【解決手段】コンパレータ1によって生成されたデジタル信号(Vcomp)のロジック状態の第1スイッチングにおいて第1ロジック状態から第2ロジック状態へと切り替える出力信号(Vout)の生成ステップと、前記出力信号(Vout)の第1ロジック状態から第2ロジック状態への変更の検出ステップと、第1ロジック状態から第2ロジック状態への変更後の第1時間間隔に対する前記出力信号(Vout)のさらなる切り替えの禁止ステップとにより前記デジタル信号(Vcomp)をノイズから保護する。

(もっと読む)

ラッチ機能付きコンパレータおよびそれを用いた試験装置

【課題】高速な応答性を有するラッチ機能付きのコンパレータを提供する。

【解決手段】比較増幅部20は、正側ラインLPの信号および負側ラインLNの信号のレベルを比較し、比較結果をラッチする。第1インバータ22は、その入力端子が正側ラインLPと接続され、その出力端子が負側ラインLNと接続される。第2インバータ24は、その入力端子が負側ラインLNと接続され、その出力端子が正側ラインLPと接続される。

活性化スイッチ26は、共通接続されたインバータ22、24の他方の電源端子に、電源電圧Vddを出力して比較増幅部20を不活性化する状態と、接地電圧VGNDを出力して比較増幅部20を活性化する状態と、を選択的に切りかえる。コンパレータTCは、比較増幅部20が活性化された後のタイミングにおける正側ラインLPの信号OPと負側ラインLNの信号ONの少なくとも一方に応じた信号を出力する。

(もっと読む)

受信回路

【課題】消費電力を低減し誤動作の少ない受信回路を提供する。

【解決手段】プリアンブルを含む変調されたディジタル信号を受信する受信装置210と、検波回路220によるベースバンド信号S1と基準信号Vrefを比較するコンパレータ250と、ベースバンド信号S1の積分回路240と、積分回路240からの平均値信号S2に基づく信号S3を生成する下側ヒステリシス電圧生成回路260と、平均値信号S2に基づく信号S4/S5を生成する上側ヒステリシス電圧生成回路270と、コンパレータ250からのディジタル信号Doutに基づき、信号S3または信号S4/S5を選択しこれを基準信号Vrefとする選択回路280と、コンパレータ250からのディジタル信号のパルス数を計数し信号Qを出力するパルス検出カウンタ290と、信号Qに基づく信号S4/S5の電圧レベルを可変する電圧と、信号を処理するディジタル回路とを有する。

(もっと読む)

コンパレータ回路

【課題】

MOSトランジスタの閾値電圧の差によって発生するオフセット電圧の影響を軽減させ、比較精度の高いコンパレータ回路を提供する。

【解決手段】

各スイッチがオンにされているキャリブレーションモードにおいて、第1のキャパシタCaおよび第2のキャパシタCbに、出力部5におけるプラス側とマイナス側の出力電圧を記憶させる。各スイッチがオフに切り替わり比較モードに移行すると、第1のMOSトランジスタM6および第2のMOSトランジスタM7のゲートに、キャパシタCaおよびCbが記憶したそれぞれの電圧が印加されて補正電圧を基準としたラッチ動作の準備が整う。電流ラッチ回路2は、入力電圧と基準電圧の差を増幅させてHIGHまたはLOWを出力する判定を行う。出力部5では、HIGHまたはLOWに応じた電圧差が生じ、これに応じた電流が流れる。

(もっと読む)

周波数検出回路

【課題】回路構成が簡単で、省電力化および小面積化を図りながら、確実に周波数を検出することが可能な周波数検出回路を提供する。

【解決手段】入力クロック信号の周波数に応じて等価抵抗が変更するものとなされたスイッチトキャパシタ回路と抵抗素子とを直列に接続し、電源電圧を前記スイッチトキャパシタ回路の等価抵抗と抵抗素子の抵抗とで分圧し、その分圧された電圧をシュミット回路に入力する。シュミット回路は、入力された分圧電位がしきい値電位を超えると高電位信号を出力し、しきい値電位未満であると低電位信号を出力する。これにより、入力クロック信号の周波数に応じて高電位信号または低電位信号が出力され、周波数を検出することができる。

(もっと読む)

相補信号生成回路

【課題】 容量素子のみによるこれまでのスキュー調整方法よりもスキューの微調整を可能にした相補信号生成回路を提供する。

【解決手段】 本発明による相補信号生成回路は、複数のインバータ(901、904、905、906)を含む第1の信号伝達経路と、インバータ(901、907、908)と抵抗素子903を含む第2の伝達経路とを有する。

(もっと読む)

コンパレータ回路

【課題】フォールデッドカスコード接続の差動増幅段を有するコンパレータにおいて、オフセットの温度依存性を減らし検出精度を向上させる。

【解決手段】ソース共通接続された一対の差動MOSトランジスタを有する差動入力段(11)と、差動MOSトランジスタのドレイン端子にフォールデッドカスコード接続されたカスコード段(12)と、差動入力段とカスコード段に共通に接続された電流回路(Mn11〜Mn13,Mn21〜Mn23)と、カスコード段の出力ノードに接続された出力段(13)とを備えたコンパレータ回路において、前記電流回路は、カスコード段のMOSトランジスタのキャリア移動度の温度特性に起因する動作点の変動をキャンセルするような温度特性を付与された電流を流すように構成した。

(もっと読む)

パルス発生回路及び通信装置

【課題】簡単な回路でかつ低消費電力で帯域制限された正確な短パルスの発生回路を具現し、フィルタを使用せずに目的のパルスを得る。

【解決手段】起動信号に基づき所定形状のパルスを出力端子から出力するパルス発生回路において、起動信号の位相が変化した時点から所定量の時間差で位相が順次変化するn+1個の信号(nは2以上の整数)を発生するタイミング発生回路と、所定の電位を供給する第1の電源及び第2の電源と、n個のインピーダンス素子と、n+1個の信号に基づく論理関数値によって所定順序で出力端子と第1の電源または第2の電源とをインピーダンス素子を介して交互に切り替えて接続するスイッチ回路と、を含むパルス発生回路。

(もっと読む)

パワーデバイスドライブ装置

【課題】ソフトシャットダウン機能を有するパワーデバイスドライブ装置の出力端子とパワーデバイスを接続する信号線を短縮化する。

【解決手段】パワーデバイスドライブ装置50には、光結合部1とパワーデバイスドライブ回路部2が設けられる。パワーデバイスドライブ回路部2には、ドライバ部21、ディセイブル回路22、I/V変換回路23、サンプルホールド回路24、ソフトシャットダウン回路25、制御端子PDisb、Vcc端子PVcc、Vo端子PVo、及びVss端子PVssが設けられる。IGBT4の短絡等の異常事態が発生したとき、制御信号Ssetがディセイブル状態となる。ディセイブル状態の制御信号Ssetがディセイブル回路22に入力され、出力部から出力される信号がHz状態となり、ソフトシャットダウン回路25のNch MOSトランジスタNMT3が“ON”しIGBT4をソフトシャットダウン状態にする。

(もっと読む)

車載情報伝達装置

【課題】インバータの温度を感知する感温ダイオードSDの温度に関する情報をマイコン20に伝達する際に、マイコン20のタイマ機能やA/D変換機能を備えたポートを使用すると、そのリソースが低減すること。

【解決手段】感温ダイオードSDの出力電圧に基づき周波数変調回路34にて周波数変調された信号は、フォトカプラ36に取り込まれる。フォトカプラ36の出力は、マイコン20に取り込まれる。マイコン20においては、フォトカプラ36の出力電圧が閾値電圧以上であるなら論理「H」と認識し、閾値電圧未満であるなら論理「L」と認識する処理を、ハードウェアにて行う。一方、論理「H」である期間や論理「L」である期間に基づく温度情報の復調処理を、ソフトウェア処理とする。

(もっと読む)

半導体集積回路

【課題】出力信号のステップパルスに伴う、不要な電磁輻射ノイズを低減する。

【解決手段】乱数制御レジスタ11は、乱数発生回路からの乱数データの出力のスタート(開始)、スタンバイ(待機)、ストップ(停止)、出力のタイミング等を制御するためのレジスタである。乱数発生回路10から出力された乱数データは、立上り/立下り時間可変データレジスタ12に格納される。立上り/立下り時間可変データレジスタ12に格納されるデータは、乱数発生回路10から順次発生される乱数データによって更新される。出力回路13は、マイクロコンピュータの内部回路14からの信号φを外部機器に出力するための回路であり、出力回路13の出力信号の立上り/立下り時間は、立上り/立下り時間可変データレジスタ12に格納された乱数データに応じて、可変制御されるようになっている。

(もっと読む)

コンパレータ回路

【課題】充放電開始電圧を任意に設定可能であり、ダイオードの温度特性に依存せず回路特性の向上が可能なコンパレータを提供する。

【解決手段】入力信号電圧と、入力信号を抵抗及びキャパシタを用いて平滑して得られた基準電圧とを比較しその結果を出力するコンパレータCOM、入力信号電圧に電圧が加算された加算信号と基準電圧とを比較し、加算信号が基準電圧より低下した時にキャパシタを放電する放電回路、入力信号電圧に電圧が加算された加算信号と基準電圧とを比較し、第2の加算信号が基準電圧より上昇した時にキャパシタを充電する充電回路を備える。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックに応答して1ビットずつレベル遷移する複数のビットの周波数制御信号を生成する周波数制御信号生成部と、及び前記複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。また、他の発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

入力インタフェース回路、集積回路装置および電子機器

【課題】信号入力端子に静電気ノイズが印加された場合に、そのノイズの内部回路への伝達を未然に、かつ確実に防止することができる入力インタフェース回路を提供すること。

【解決手段】ノイズを検出するノイズ検出回路(200)と、ノイズが検出されたときに第1のスイッチ回路(SW1)をオフしてノイズ伝達を遮断する機能をもつノイズキャンセラ(300)と、を設ける。第1のスイッチ回路(SW1)がオフしているときは、第2のスイッチ回路(SW2)がオンして、直前の電圧をラッチする。ノイズ検出回路200に含まれるノイズ検出用トランジスタは、Nウエルの電位を適応的に最適化することができるフローティングNウエルトランジスタによって構成される。

(もっと読む)

1 - 20 / 42

[ Back to top ]