Fターム[5J049AA00]の内容

パルス列発生器 (633) | 回路要素 (417)

Fターム[5J049AA00]の下位に属するFターム

非安定回路(発振回路) (36)

単安定回路 (2)

双安定回路 (49)

遅延回路(遅延線を含む) (29)

積分回路 (2)

微分回路

定電流回路 (5)

差動増幅器 (9)

オペアンプ (3)

比較器 (17)

シュミット・トリガ回路 (1)

カウンタ (26)

シフトレジスタ (30)

分周回路 (10)

AD/DA変換器 (19)

選択回路、マルチプレクサ、デマルチプレクサ (24)

エンコーダ、デコーダ (10)

フィルタ(濾波器) (15)

V/F変換器

ピークホールド回路

PLA

レジスタ (13)

加算器、減算器 (26)

メモリ(ROM、RAM等) (53)

Fターム[5J049AA00]に分類される特許

1 - 20 / 38

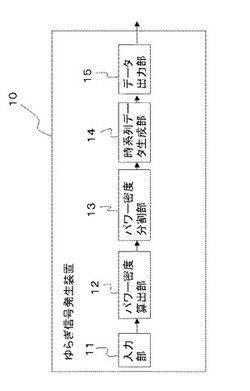

ゆらぎ信号発生装置、ゆらぎ信号発生方法、及びゆらぎ信号発生プログラム

【課題】様々な傾きを有したゆらぎを発生させるとともに、人の要求する山場(ピーク)位置もある程度設定できるゆらぎ信号発生装置を提供する。

【解決手段】ゆらぎ信号発生装置10は、パワー密度を算出する関数とパワー密度を算出する関数のパラメータを入力する入力部11と、入力部によって入力されたパラメータとパワー密度を算出する関数に基づいて、各周波数のパワー密度を算出するパワー密度算出部12と、パワー密度算出部によって算出された各周波数のパワー密度を正弦波成分と余弦波成分に分けるパワー密度分割部13と、パワー密度分割部によって分割された成分に基づいて逆フーリエ変換により時系列データを生成する時系列データ生成部14と、時系列データに基づいて出力データを生成し出力するデータ出力部15と、を備えた。

(もっと読む)

パルス生成回路およびパルス生成方法

【課題】電源電圧の変動しやすい容量の小さい電源である環境下でも、安定したパルス信号を生成できるようにする。

【解決手段】タイミング制御回路1−1,1−2と論理回路2−1とを設ける。タイミング制御回路1−1,1−2は、放電制御端子S11,S21と充電制御端子S12,S22,と信号出力端子T1,T2を有し、内部に時定数素子を備えている。先ず、充電制御端子S12,S22へ充電の開始を指示し、端子T1,T2から出力される電圧VT1,VT2を「H」レベルとする。次に、放電制御端子S11へ放電の開始を指示し、遅延時間τ1経過後に電圧VT1を「L」レベルとし、タイミング制御回路1−2での放電を開始させ、遅延時間τ2経過後に電圧VT2を「L」レベルとする。このタイミング制御回路1−1,1−2からの電圧VT1,VT2を論理回路2−1へ与え、論理回路2−1よりタイミング制御回路1−2での遅延時間τ2をパルス幅とするパルス信号PS1を得る。

(もっと読む)

擬似乱数出力装置、送信装置及び探知機

【課題】他の装置との間で類似することが少ない擬似乱数列を出力し得る擬似乱数出力装置を提供する。

【解決手段】船舶に搭載される擬似乱数出力装置20は、GPS受信機21と、擬似乱数発生部22と、を備える。GPS受信機21は、GPS衛星から測位信号を受信し、自船の位置等のデータを取得する。擬似乱数発生部22は、GPS受信機21が出力する緯度及び経度の情報を加工したものをシードとして用いることにより、擬似乱数を発生させる。擬似乱数発生部22から得られた擬似乱数は、船舶に搭載されるレーダ装置1において、レーダアンテナ14からパルス信号を送信する時間間隔を決定するために用いられる。

(もっと読む)

半導体集積回路、情報処理装置、および情報処理方法、並びにプログラム

【課題】集積回路の既存のフリップフロップを利用して乱数やID生成を行う構成を実現する。

【解決手段】LSIなどの集積回路のテスト用パスとして設定されたスキャンチェーンに接続された複数のフリップフロップから、電源投入時のフリップフロップ設定値を入力するデータ収集部を設けた。データ収集部は、スキャンチェーンまたは独立の接続パスを経由して電源投入時のフリップフロップ設定値を入力し、入力値に基づく乱数または固定データとしてのID生成処理を実行する。この構成により、LSI等の集積回路に形成された既存のフリップフロップをそのまま利用して乱数やIDの生成を行うことが可能となる。

(もっと読む)

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を提供する。

【解決手段】パルス発生装置100を、起動開始信号D0の入力に応じて単位パルス信号を発生する、各々の信号出力部が独立した単位パルス発生回路20_1〜20_Nと、単位パルス発生回路20_1〜20_Nのうち単位パルス信号を出力する予定の一部の回路の信号出力端子を順次選択して、該選択した信号出力端子を共通の信号出力線Pu_Coutに電気的に接続し、残りの単位パルス発生回路の信号出力端子を共通の信号出力線Pu_Coutから電気的に切断するスイッチ制御回路30及び選択スイッチ40とを含む構成とした。

(もっと読む)

パルス信号生成方法およびパルス信号生成装置

【課題】 PWMを用いたパルス信号生成装置において低周波数ノイズの発生を回避してノイズ除去の容易化を実現する。

【解決手段】 パルス信号生成装置(10)は、パルス幅設定部(11)と、波形制御部(12)と、出力部(13)とを備える。パルス幅設定部(11)は、パルス幅データ(DD)を設定する。波形制御部(12)は、周期に相当する数のビットを有し、パルス幅データ(DD)の値に相当する数のビットが第1論理値に設定され且つ残りのビットが第2論理値に設定された波形データ(DW)を、同一の論理値のビットが分散されるように生成する。出力部(13)は、波形データ(DW)の各ビットを順番に選択することによりパルス信号(OUT)を出力する。

(もっと読む)

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を

提供する。

【解決手段】パルス発生装置100を、CLK信号の入力に応じて起動開始信号D0と、

D0を反転したXD0とを出力する起動開始信号生成回路20と、起動開始信号の入力に

応じてパルス信号を発生する、各々の信号出力部が独立した第1〜第Nのパルス発生回路

21_1〜21_Nと、第1〜第Nのパルス発生回路21_1〜21_Nのうちパルス信

号を出力する予定の一部の回路の信号出力部を順次選択して、該選択した信号出力部を共

通の信号出力線に接続し、残りのパルス発生回路の信号出力部を共通の信号出力線から電

気的に切断する選択回路22とを含む構成とした。

(もっと読む)

線形帰還シフト演算装置、通信装置、マイクロプロセッサ、及び線形帰還シフト演算装置におけるデータ出力方法

【課題】遅延の少ない線形帰還シフト演算装置、通信装置、マイクロプロセッサ、及び線形帰還シフト演算装置におけるデータ出力方法を提供する。

【解決手段】入力データが入力され、出力データを出力する線形帰還シフト演算装置において、入力された係数p−1〜pN−1(Nは2以上の自然数)のうち係数p0〜pN−2から、q値q0〜qN−2を生成するL生成部と、前記q値q0〜qN−2と、前記係数p−1〜pN−1と、前記入力データa−N〜a−1,a0〜aN−1とから、出力データb0〜bN−1を演算して前記出力データとして出力する行列演算部とを備える。

(もっと読む)

パルス発生回路及び通信装置

【課題】簡単な回路でかつ低消費電力で帯域制限された正確な短パルスの発生回路を具現し、フィルタを使用せずに目的のパルスを得る。

【解決手段】起動信号に基づき所定形状のパルスを出力端子から出力するパルス発生回路において、起動信号の位相が変化した時点から所定量の時間差で位相が順次変化するn+1個の信号(nは2以上の整数)を発生するタイミング発生回路と、所定の電位を供給する第1の電源及び第2の電源と、n個のインピーダンス素子と、n+1個の信号に基づく論理関数値によって所定順序で出力端子と第1の電源または第2の電源とをインピーダンス素子を介して交互に切り替えて接続するスイッチ回路と、を含むパルス発生回路。

(もっと読む)

表示装置

【課題】表示装置に最適な乱数発生回路を実現する。

【解決手段】表示装置は表示パネルと、制御回路と、乱数発生回路とを備え、乱数発生回路は複数のシフトレジスタと、出力回路と、初期値を保持するレジスタとからなり、複数の初期値を備えることで乱数のランダム性を向上させる。また、複数のシフトレジスタからそれぞれ異なる乱数を出力させることが可能なことから、出力回路にて周波数を増加させて出力することが可能となる。また、デジタル信号の反転数を抑えるノイズコントロール信号を付加して液晶表示装置から発生する電磁波ノイズを低減する。また、複数のシフトレジスタの基本クロックを、断続的に停止を繰り替える間欠駆動クロックとすることで、表示装置から発生する電磁波ノイズを低減する。基本クロックは、表示データの転送クロックに同期するクロック、あるいは、表示データの転送クロックに非同期なクロックであってもよい。

(もっと読む)

クロック発振回路

【課題】簡単な回路構成でスペクトラム拡散を行うことが可能なクロック発振回路を提供する。

【解決手段】基本クロック信号を発振する基本クロック発振器と、基本クロック信号と非同期で、かつ基本クロック信号より短い周期としたクロック調整信号を発振する調整クロック発振器と、基本クロック信号をクロック調整信号の1周期分シフトして、クロックシフト信号として出力するシフト回路23cと、基本クロック信号およびクロックシフト信号を1周期ごとに切り替えて、調整クロック信号として出力する切替回路として機能するカウンタ回路23aおよびセレクタ回路23bとを備えている。シフト回路23cは、基本クロック信号をクロック調整信号の立ち上がりで同期する第2フリップフロップ23c1で形成され、カウンタ回路23aは、基本クロック信号を2分周する第1フリップフロップ23a1および第1インバータ23a2で形成されている。

(もっと読む)

半導体集積回路

【課題】乱数生成回路から出力される1ビットのシードの不規則性を高める。

【解決手段】乱数生成回路50には発振回路11、平滑化回路12、及び真性化回路13が設けられる。発振回路11と平滑化回路12の間は、信号線路DL1で接続される。信号線路DL1の発振回路11側には、クロック信号CLKAを伝送する信号線路DL11が所定の長さの期間Lだけ信号線路DL1に近接配置される。近接配置された信号線路DL11を伝送するクロック信号CLKAにより、信号線路DL1を伝送する発振回路の出力信号S1にクロストークノイズが付加され、時系列的に見て乱数性が非常に高い乱数データとしての出力信号S1Aが平滑化回路12に入力され、平滑化回路12で平滑された出力信号S2が真性化回路13に入力される。

(もっと読む)

ジッタ印加回路、パターン発生器、試験装置、および、電子デバイス

【課題】高周波数かつ大振幅のジッタを生成する。

【解決手段】ジッタを有するジッタ重畳信号を生成するジッタ印加回路であって、与えられる基準信号を、それぞれ予め設定される遅延量で順次遅延させる、縦続接続された複数の遅延回路と、それぞれの遅延回路が出力する信号のタイミングに応じて、ジッタ重畳信号のそれぞれのエッジを生成する信号生成部と、ジッタ重畳信号の各周期に印加すべきジッタに応じた遅延量をそれぞれ設定する遅延設定部とを備え、少なくとも一つの遅延回路の遅延量が、ジッタ重畳信号の平均周期の整数倍とは異なる値に設定されるジッタ印加回路を提供する。

(もっと読む)

準固定回路

【課題】スクランブラ等の同じ機能の回路であっても、異なる種類の回路を1つの回路で実現することができる準固定回路を提供することである。

【解決手段】複数種類のCRC(Cycle Redundancy Check)回路の複数ビット同時処理が可能である準固定回路であって、複数のフリップフロップと、第1の入力ビット信号及び前記複数のフリップフロップの出力信号を基に選択的に排他的論理和を演算し、シフト1回目に相当する出力信号を出力するための第1の排他的論理和回路と、第2の入力ビット信号及び前記シフト1回目に相当する出力信号を基に選択的に排他的論理和を演算し、シフト2回目に相当する出力信号を出力するための第2の排他的論理和回路とを有する準固定回路が提供される。

(もっと読む)

乱数発生装置及び車両制御装置

【課題】セキュリティ性を向上させることを主たる目的とし、加えて不揮発性メモリの書き換え回数を低減することができる乱数発生装置、及び当該乱数発生装置を備える車両制御装置を提供する。

【解決手段】第1乱数発生部21はバックアップRAM13に記憶された過去に発生した乱数を基に新たな乱数を発生し、第2乱数発生部22は、第1乱数発生部21が発生する乱数とは異なる乱数を発生する。バッテリキャンセル後にバッテリ7からの電源供給が再開されてから最初の乱数を発生させる場合に、演算部23は、第1乱数発生部21が発生する乱数に対して第2乱数発生部22が発生する乱数を用いた所定の演算を行う。

(もっと読む)

テンプレートパルス発生回路、通信装置、および通信方法

【課題】パルス通信における省電力化に適したテンプレートパルス発生回路、通信装置、および、この通信方法を提供する。

【解決手段】システムコントローラ830からの制御信号CTLによって、受信パルスの検波に際して同期捕捉(823)を行う同期捕捉モード時にはテンプレートパルス発生回路820がテンプレートパルスを連続的に出力し、同期捕捉が略確立して以降の同期追従モード時にはテンプレートパルスを断続的に出力するようにテンプレートパルスの発生態様を切換えて、パルス通信の開始当初に連続的なテンプレートパルスを利用して短時間で同期捕捉を確立させ、これ以降はテンプレートパルスを断続的に出力するようにして省電力化を図る。

(もっと読む)

雑音信号発生装置

【課題】広帯域で周波数密度が一定の雑音信号を短い処理時間で発生させる。

【解決手段】所望の雑音信号のスペクトラムをその上限周波数FMAXの1/Mとなる境界周波数Faで低域側と高域側に分け、各帯域について所望周波数分解能ΔFのM倍の値で上限周波数FMAXを除して得られる値をポイント数Nとするスペクトラムデータを生成して逆フーリエ変換を行い、得られた低域側の時間波形データDa(k)に対し、倍率Mの補間処理と境界周波数Faの低域通過フィルタ処理して所望周波数分解能に対応した時間波形データDa(k)″を生成し、得られた高域側の時間波形データDb(k)に対し、M通りの異なる遅延時間を与えて所望周波数分解能に等しい周波数差のあるキャリア周波数で境界周波数以上の高域帯へ周波数変換して複数Mの時間波形データDb1(k)〜DbM(k)に変換し、低域側の時間波形データと合成して所望の雑音信号を得ている。

(もっと読む)

信号発生装置

【課題】所望の位相雑音が付加された信号を簡易な構成で生成できるようにする。

【解決手段】2相キャリア信号生成手段21により90゜位相が異なる2相のキャリア信号Sc、Sc′を生成し、その一方Scと雑音信号発生器23から出力される雑音信号θnとを乗算器24に入力し、その乗算器24の出力信号Aの大きさを可変減衰器25で調整しBPF26で帯域制限して、他方のキャリア信号Sc′とともに合成器27に与えて加算合成または減算合成する。この構成で、雑音信号θnの振幅がキャリア信号Scの振幅に対して十分小さければ、振幅雑音が極めて少なく、雑音信号θnに対応した位相雑音が含まれた信号Snを合成器27から出力することができる。

(もっと読む)

ワンダ発生装置及びディジタル回線試験装置

【課題】簡易な構成で所望のワンダを有する信号を発生することができるワンダ発生装置、及び当該ワンダ発生装置を備えるディジタル回線試験装置を提供する。

【解決手段】ワンダ発生装置1は、ダイレクトディジタルシンセサイザ(DSS)14に発生させる信号の中心周波数を規定するデータを設定する周波数設定部11と、所定のワンダを発生させるためのワンダデータを記憶するワンダメモリ12と、周波数設定部11で設定されたデータとワンダメモリ12から読み出されたワンダデータとを加算する加算器13と、加算器13の加算結果を用いて所定周波数の信号を出力するDSS14とを備える。

(もっと読む)

パルス発生回路およびこの回路を用いた電子装置、携帯電話機、パーソナルコンピュータ、ならびに、この回路を用いる情報伝送方法

【課題】パルスの休止期間における貫通連流の値をも極小にして極限まで低消費電力化を

図ったパルス発生回路を提供する。

【解決手段】パルス発生回路を、所定段数縦続接続されたインバータ回路101〜109

と、これらインバータ回路101〜109の各段の手段によって論理反転動作を行う論理

回路110〜125を備え、論理回路110〜125の出力に応じて出力端を第1の電位

レベルV1か又は第2の電位レベルV2かに選択的に接続して出力端131に出力パルス

Poutを得るようにし、該出力パルスPoutの中間の基準レベルとしてV1〜V2を分圧回

路11によって分圧した第3のレベルV3に設定するが、パルスの休止期間では、オンオ

フ制御信号生成回路1500の制御下で開閉手段150をオフにして分圧回路11への給

電を断ち貫通電流が流れないようにする。

(もっと読む)

1 - 20 / 38

[ Back to top ]