Fターム[5J055FX12]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 信号を得る箇所 (1,721) | 制御端子 (1,433)

Fターム[5J055FX12]に分類される特許

41 - 60 / 1,433

液晶表示装置

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

正負電圧論理出力回路およびこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とし、回路動作の確実性、安定性の向上を図った正負電圧論理出力回路を提供する。

【解決手段】論理入力と負電圧との間に、ゲートに論理入力するエンハンスメント型P型電界効果トランジスタEPFET1とブレークダウン保護用素子13,14とが直列に接続され、ブレークダウン保護用素子14に並列に短絡する切替スイッチ8aが接続される。切替スイッチ8aをオン、オフ制御することで、VSSの変動に対して正常な回路動作を確保できる動作ウィンドウの拡張を可能とする。

(もっと読む)

電源電圧検出回路

【課題】低電圧状態を検出し、システムへの通知やシステムの停止等を行う電源電圧検出回路において低電源電圧時の誤動作を回避する電源電圧検出回路を提供する。

【解決手段】基準電圧Vrefを生成する回路200の出力にプルアップ回路250を設け、基準電圧Vrefを生成する回路200を電源電圧VE(100)までプルアップする。さらに、R1(341),R2(342)から成る検出抵抗に直列にスイッチS1(347)を設け、基準電圧Vrefを生成する回路200によって、上記スイッチS1(347)をオン/オフする。そうしておいて低電源電圧時に上記プルアップ回路250により基準電圧Vref(225)を上記電源電圧VE(100)までプルアップさせると共に、上記スイッチS1(347)をオフし分圧値VI(345)を強制的に低下させることで、Vref>VIの状態を保持し、比較器330からの誤信号出力を回避する。

(もっと読む)

半導体スイッチの制御装置

【課題】半導体スイッチ素子に並列に接続される保護回路の異常を検出できる半導体スイッチ素子の制御回路を得る。

【解決手段】半導体スイッチに印加される電圧を抑制するために半導体スイッチに並列に接続された保護回路と、駆動回路の出力ゲート電圧が予め設定された電圧以上あることを検出し、半導体スイッチのオン・オフ状態を判別するゲート電圧検出手段と、半導体スイッチの主端子電圧を検出する主電圧検出手段と、駆動回路に与えられた駆動信号により、駆動指令がオン指令の場合はゲート電圧状態を選択し、駆動指令がオフ指令の場合は主電圧状態を選択する選択手段と、選択手段の出力を絶縁して低圧回路に伝達する第一の信号絶縁手段と、選択手段が選択して出力したゲート電圧状態・主電圧状態と半導体スイッチの駆動指令とを比較し、半導体スイッチの正常又は異常を判別する判別手段とを備える。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

低Vf逆導通FET回路及び多機能FET回路用IC

【課題】内部ダイオード又は外部ダイオードを使用せずに、逆方向へ導通可能なMOS−FET回路を提供すること。

【解決手段】MOS−FET(10)と、このMOS−FET(10)のドレインをマイナス入力に接続し、ソースをプラス入力に接続したオペアンプ(15)と、このオペアンプ(15)の出力を一方の入力とし、ゲート端子(14)を他方の入力とした第一OR回路(17)とからなり、前記第一OR回路(17)の出力を前記MOS−FET(10)のゲートに接続した。

(もっと読む)

RFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器

【課題】スイッチング素子の個数を減らし、スイッチング素子を送受信時共有して、RFアンテナスイッチのサイズを減らすと共に、小型化及びワンチップ化にさらに応じるRFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器を提供する。

【解決手段】アンテナ1と、少なくとも一つの送信段2及び少なくとも一つの受信段3を備える複数の入出力段と、少なくとも一つの送信段2とアンテナ1側の共通ノード4、5との間の送信経路上に配置され、制御信号によって信号を伝達する少なくとも一つの送信スイッチブロック10と、受信段3と共通ノード4、5との間の受信経路上に配置され、制御信号によって伝達する少なくとも一つの受信スイッチブロック30、30a、30bと、スイッチング素子を共有して各々の送信及び受信動作と同期してオン動作する共用送受信スイッチブロック50とを含む。

(もっと読む)

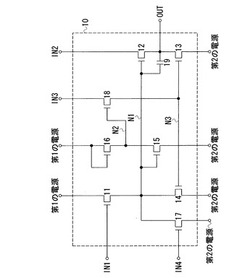

トランジスタ駆動回路

【課題】より簡単な構成で、出力トランジスタを確実にオフ状態に維持できるトランジスタ駆動回路を提供する。

【解決手段】NチャネルMOSFET5とコイル2との共通接続点;出力端子OUTとグランドとの間にフライホイールダイオード3を接続する。FET5のゲートには、NPNトランジスタ6及びPNPトランジスタ7のプッシュプル回路により制御信号を出力し、トランジスタ7のベースとグランドとの間にNPNトランジスタ11を接続し、トランジスタ11のベースとグランドとの間にNチャネルMOSFET14を接続して、FET14にPWM信号を入力する。ダイオード13は、FET14がオフ状態になるとトランジスタ11のベースにベース電流を供給し、ダイオード15をダイオード13のアノードとトランジスタ6及び7のベースとの間に接続する。NPNトランジスタ22をFET5のゲートと出力端子との間に接続し、トランジスタ22をPWM信号に応じてFET5がオフする際にオンさせる。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

半導体装置

【課題】体格及びコストの増大が抑制された半導体装置を提供する。

【解決手段】直流電源とグランドとの間に直列接続された2つの単位回路と、単位回路を制御する制御部と、を備え、2つの単位回路の中点に誘導性負荷が接続された半導体装置であって、2つの単位回路それぞれは、第1スイッチ素子と、第1スイッチ素子と逆並列接続された還流ダイオードと、還流ダイオードと第1スイッチ素子それぞれと並列接続されたバイパス部と、を有し、バイパス部は、直列接続された第2スイッチ素子及び抵抗を有し、制御部は、2つの単位回路の第1スイッチ素子をOFF状態にするデッド期間を挟んで、2つの第1スイッチ素子を交互にON状態とし、デッド期間において、一方の第1スイッチ素子がOFF状態からON状態に移行するまで、一方の第1スイッチ素子と並列接続された第2スイッチ素子をON状態にする。

(もっと読む)

スイッチング素子の保護回路

【課題】窒化物FETを高速スイッチング動作させることができ、且つ、サージ電圧から窒化物FETを保護することができるスイッチング素子の保護回路。

【解決手段】直列に接続された高圧側素子M1及び低圧側素子M2と、高圧側素子をオンオフさせる信号を出力するハイサイドプリドライバ11と、高圧側素子と逆のオンオフ状態になるように低圧素子をオンオフさせる信号を出力するローサイドプリドライバ12と、高圧側素子と低圧側素子の接続点に制御端子が接続されたスイッチング素子Tr1と、スイッチング素子の一方の端子にカソードが接続されたダイオードD1と、ダイオードのアノードに入力端子が接続され、ダイオードのブレーク時にスイッチング素子の制御端子に電流を供給するとともに、低圧側素子のオフを指示する信号をローサイドプリドライバに供給する制御器21とを備える。

(もっと読む)

半導体スイッチ及びスイッチ装置

【課題】電流変動が大きな箇所の半導体スイッチにおいて耐電流と損失を最適化する。

【解決手段】電気的特性及び種類が互いに異なるFET11とIGBT12を並列接続することで半導体スイッチ1aを形成する。端子5及び6間を接続するとき、FET11及びIGBT12は同時にオンされる。端子5及び6間の電流が小電流であるときには、FET11の内部抵抗がIGBT12よりも小さいため、FET11側に優先的に電流が流れて低損失が実現される。端子5及び6間の電流が増大するにつれて、FET11では発熱が内部抵抗増大を招くがIGBT12では内部抵抗が殆ど変化しないため、或る電流値以上では、IGBT12側に優先的に電流が流れる。結果、大電流がFET11側に流れることによるFET11の劣化又は破損が回避される。

(もっと読む)

パワーMOSFETの駆動回路およびその素子値決定方法

【課題】パワーMOSFETを高速駆動する場合であっても、寄生インダクタンスに流れる電流の時間変化に応じて発生する電圧に起因したセルフターンオンの発生を防止できるようにしたパワーMOSFETの駆動回路、また、その素子値決定方法を提供する。

【解決手段】制御回路が、駆動回路によってスイッチを駆動制御することで、(2)区間においてスイッチS2HおよびS2Lをオンすると共にその他をオフとし、(3)区間においてスイッチS1LおよびS3Hをオンすると共にその他をオフとする。すると、(2)〜(3)区間にかけて、ハイサイド側のMOSFETのゲートソース間を所定のインピーダンスに切り替えることができ、リカバリー後半に至ったとしてもハイサイド側のMOSFETのゲートソース間電圧Vgs1を閾値電圧Vt未満に抑制できる。

(もっと読む)

半導体装置及びそれを備えた半導体リレー装置

【課題】半導体装置及び半導体リレー装置において、製造コストを抑えつつ、CR積の値を小さくする。

【解決手段】双方向スイッチ1を構成する2つのMOSFETのうち、一方のMOSFET2に、化合物半導体で構成されたユニポーラ型化合物半導体装置を用い、他方のMOSFET3に、シリコンで構成されたSi−MOSFETを用いる。ここで、ユニポーラ型化合物半導体装置の中には、Si−MOSFETよりもCR積の値が小さいものが多く存在する。従って、一方のMOSFET2にユニポーラ型化合物半導体装置を用いたことにより、両方のMOSFET2、3にSi−MOSFETを用いた場合に比べて、装置全体のCR積の値を小さくできる蓋然性が高まる。また、Si−MOSFETよりも製造コストの高いユニポーラ型化合物半導体装置を2つ用いた場合に比べて、製造コストを抑えられる。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、第1及び第2の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

ゲートドライブ回路

【課題】ワイドバンドギャップ半導体からなるスイッチング素子の回生動作時の電力損失を抑制し、かつ、安定してターンオン/オフさせることができるゲートドライブ回路。

【解決手段】制御回路とスイッチング素子Q1のゲートとの間に接続され、コンデンサC1と抵抗R1とダイオードD1からなる直列回路と、スイッチング素子のゲートとソースとの間にPNP型トランジスタQ2が抵抗R2を介して接続され、トランジスタQ2のコレクタ・ベース間にダイオードD2が接続され、さらにトランジスタQ2のベースはダイオードD1のアノードに接続され、制御回路からのオフ信号が入力されると、トランジスタの接合電圧とダイオードD2との順方向電圧との差分電圧を残してゲートとソースとの間を短絡する。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、複数の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

41 - 60 / 1,433

[ Back to top ]