Fターム[5J055FX20]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 制御、帰還信号の特徴 (2,064) | 制御、帰還信号に閾値を有する (418)

Fターム[5J055FX20]に分類される特許

141 - 160 / 418

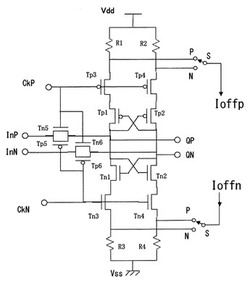

ラッチ型コンパレータ及びこれを用いた多値論理復調回路

【課題】製造プロセスのマージンを削ることなく、オフセットの補正が可能なラッチ型コンパレータ、及びこれを用いた、オフセットの補正が可能な多値論理の復調回路を提供する

【解決手段】本発明によるラッチ型コンパレータは、クロスカップルされた2つのCMOSインバータからなるフリップフロップを含み、フリップフロップの4個のトランジスタの各々のソースと電源/接地間には伝達トランジスタを介して抵抗と設定電流可変の定電流源が接続され、フリップフロップの差動出力は各々伝達トランジスタを介して差動入力に接続され、全ての伝達トランジスタのゲートは、差動クロック入力のいずれかに接続されていることを特徴とする。

(もっと読む)

半導体集積回路、半導体集積回路の駆動方法、電子機器および電子機器の駆動方法

【課題】高耐圧化可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路は、第1電位ノード〔VDD〕と接続された第1ノード〔VOUT〕と、第1ノード〔VOUT〕と第1電位ノードより低電位である第2電位ノード〔VSS〕との間に直列に接続された第1のnチャネル型トランジスタ〔NT1〕および第2のnチャネル型トランジスタ〔NT2〕を有し、第1のnチャネル型トランジスタ〔NT1〕の一端は、第2電位ノード〔VSS〕に接続され、他端は、第2のnチャネル型トランジスタの一端に接続され、ゲート端子は、第2ノード〔VIN〕に接続され、第2のnチャネル型トランジスタ〔NT2〕の他端は、第1ノード〔VOUT〕に接続され、ゲート端子は、第1電位ノード〔VDD〕と第2電位ノード〔VSS〕との間に位置する第1中間電位〔VM1〕に接続されている。第2のnチャネル型トランジスタにより分圧され、各トランジスタに印加される電圧を低減できる。

(もっと読む)

トレラントバッファ回路及びインターフェース

【課題】出力端子が出力回路の電源電圧より高電位である場合や、出力回路の電源電圧が0Vになっても出力端子から電源電圧へ電流の逆流入は発生しないトレラントバッファ回路及びインターフェースを提供すること。

【解決手段】トレラントバッファ回路100は、電源端子VDD1と出力端子102の間にソースを共有して直列接続されたPチャンネルMOSトランジスタQ111,Q112と、出力端子102と接地端子の間に接続されたNチャンネルMOSトランジスタQ113と、PチャンネルMOSトランジスタQ111のゲートに出力接続されたインバータ121と、PチャンネルMOSトランジスタQ112のゲートに出力接続されたインバータ122と、各MOSトランジスタQ111、Q112、Q113にそれぞれ第1、第2及び第3の制御信号を出力してこれらのMOSトランジスタのオン・オフを制御する制御回路130とを備える。

(もっと読む)

駆動回路

【課題】電力ロスを低減しつつセンサ回路に供給される電圧の安定化を図ることができるセンサ駆動回路を安価に提供する。

【解決手段】電圧検出回路12が、ブリッジ回路Bに供給される交流電圧を分圧した電圧を基準電圧Vrefだけシフトアップした電圧を出力する。第1比較回路13が、電圧検出回路12により出力された電圧と第1比較電圧Vc1とを比較して、ブリッジ回路Bに供給される正の交流電圧の大きさが電圧Vthを越えないように第1トランジスタQ1を制御する。第2比較回路14が、電圧検出回路12により出力された電圧と第2比較電圧Vc2とを比較して、ブリッジ回路Bに供給される負の交流電圧の大きさが電圧Vthを越えないように第2トランジスタQ2を制御する。

(もっと読む)

シュミットトリガ型インバータ

【課題】さらに入力ノイズ耐性を有するシュミットトリガ型インバータを提供すること。

【解決手段】入力側ノードへの供給電圧が増加して第1の基準電圧に達するに従い出力側ノードから出る電圧が比較高電圧レベルから比較低電圧レベルに遷移し、入力側ノードへの供給電圧が減少して第1の基準電圧より低い第2の基準電圧まで減少するに従い出力側ノードから出る電圧が比較低電圧レベルから比較高電圧レベルに遷移するインバータと、インバータの入力側ノードに一方端が接続された第1の抵抗素子と、インバータの入力側ノードに一方端が接続された、該一方端の電圧が上昇するほどに抵抗値が減じる可変抵抗素子と、可変抵抗素子の他方端に一方端が接続された第2の抵抗素子と、ドレインが第2の抵抗素子の他方端に接続され、ゲートがインバータの出力側ノードに接続され、ソースが接地電位に接続されたnチャネルMOSトランジスタとを具備する。

(もっと読む)

半導体集積回路

【課題】電源起動時のリーク電流によるトランジスタの誤作動を防止することが可能な半導体集積回路を提供すること。

【解決手段】発明にかかる半導体集積回路は、第1の制御信号を駆動回路120を介して出力する論理回路209と、コレクタが高電位側の電源電圧VCCに接続され、エミッタが出力端子VOUTに接続され、ベースに入力される第1の制御信号に応じてオンオフが制御されるNPN型バイポーラトランジスタ201をそなえる。また、一方の端子がベースと駆動回路210との間のノードに接続され、他方の端子が電源電圧及び接地電圧のいずれか一方に接続されたトランジスタスイッチ203と、第1のトランジスタスイッチに並列に接続された抵抗素子205とを備える。このような回路構成により、電源起動時のリーク電流によるトランジスタの誤作動を防止することができる。

(もっと読む)

ゲートドライバおよびその操作方法

【課題】ゲートドライバおよびその操作方法を提供する。

【解決手段】本発明は、液晶ディスプレイ装置に用いられる複数の直列されたシフトレジスタを有するゲートドライバに関する。各前記シフトレジスタは前記液晶ディスプレイ装置における一行の画素にゲートライン駆動信号を提供するのに用いられる。前記ゲートライン駆動信号はフロントパルスとリアパルスを有し、前記シフトレジスタはフロントパルス発生部とリアパルス発生部を有して対応するパルスを発生する。各前記パルス発生部は第1プルアップ回路を有して電圧レベルを発生し、これにより第2プルアップ回路におけるスイッチ素子を導電状態に維持させる。従って、対応するクロック信号に応じてフロントパルスまたはリアパルスを発生し、及び2つのプルダウン回路は、前記電圧レベルに応じてプルダウン周期のみで前記フロントパルスまたはリアパルスを発生させる。

(もっと読む)

絶縁ゲート型半導体装置の駆動回路

【課題】ターンオンサージやターンオフサージを抑制できる絶縁ゲート型の半導体装置の駆動回路を提供する。

【解決手段】IGBT駆動回路の供給側(電源側)からゲート電極7aとダミーゲート電極7bに至る経路内における各抵抗22〜24について、ゲート電極7aに至る経路に存在する第1、第3抵抗22、24の抵抗値Rg1、Rg3の合計値Rg1+Rg3よりもダミーゲート電極7bに至る経路に存在する第2抵抗23の抵抗値Rg2の方が小さくなるようにする。また、ゲート電極7aやダミーゲート回路と電極7bからIGBT駆動回路の引き抜き側(GND側)に至る経路内における各抵抗22〜24について、ゲート電極7aからの経路に存在する第1抵抗22の抵抗値Rg1の方がダミーゲート電極7bからの経路に存在する第2、第3抵抗23、24の抵抗値Rg2、Rg3の合計値Rg2+Rg3よりも小さくなるようにする。

(もっと読む)

半導体集積回路

【課題】発振回路において発振動作が行われているか否かを判定する発振停止検出回路を内蔵した半導体集積回路において、電源電位が立ち上がる際の誤検出を防止する。

【解決手段】この半導体集積回路は、クロック信号又は反転クロック信号がゲートに印加されて交互にオン/オフする複数のトランジスタが直列に接続され、第1の電源電位から正の電荷を移送するトランジスタ列と、複数のトランジスタによって移送される電荷を蓄積する複数のコンデンサと、最終段のコンデンサの端子をプルダウンするプルダウン素子と、最終段のコンデンサの端子の電位がゲートに印加され、第2の電源電位がソースに供給されるNチャネルMOSトランジスタと、該NチャネルMOSトランジスタのドレインをプルアップするプルアップ素子と、該NチャネルMOSトランジスタのドレイン電位に基づいて出力信号を生成する論理回路とを具備する。

(もっと読む)

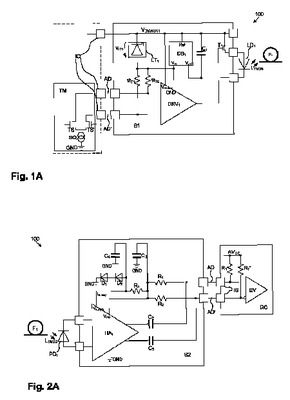

TMDS符号化信号を伝送する回路装置及び方法

少なくとも部分的に、特に少なくともタイムスロット方式でTMDS符号化され、且つ特に少なくとも1つのDVIデータ接続、及び/又は、少なくとも1つのHDMIデータ接続に割り当てられた信号を、少なくとも1つのデータソースから少なくとも1つのデータシンクへ安価に伝送する回路装置(100;100’)及び方法を提供するために、

駆動回路(S1;S1’)は、上流に接続され且つ前記データソースに割り当てられた少なくとも1つの接続インターフェース(IQ)によって、約5ボルトの供給電圧を含み、特に約55ミリアンペア以下でチャージすることができる、供給電圧(VDVI/HDMI)を供給されること、

前記駆動回路(S1;S1’)の下流に接続された少なくとも1つの発光素子(LD1)、特に少なくとも1つの光ダイオード、少なくとも1つの発光ダイオード、少なくとも1つのレーザダイオード、あるいは少なくとも1つの半導体レーザを含む少なくとも1つのレーザによって、電気的なTMDS符号化信号を電気−光変換して、前記TMDS符号化信号を与えられた光(LTMDS)として、少なくとも1つの光ファイバー(F1)、特に少なくとも1つのガラス繊維又は少なくとも1つのプラスチックファイバーを含む少なくとも1つのプラスチック材料繊維に、連結すること、

少なくとも1つのTMDSトランスミッタ(TM)からデータソースに割り当てられた前記接続インターフェース(IQ)へ供給される直流電流部分は、前記駆動回路(S1;S1’)によって前記発光素子(LD1)を制御する変調信号電流に変換されること、

前記TMDS符号化信号を与えられた前記光(LTMDS)は、少なくとも1つの光吸収素子(PD1)、特に少なくとも1つのフォトダイオードによって、前記光ファイバー(F1)から取り出されて、光−電気変換され、前記光吸収素子(PD1)の下流且つ前記データシンクに割り当てられた少なくとも1つの接続インターフェース(IS)の上流に接続された少なくとも1つのトランスインピーダンス変換回路(S2;S2’)に供給され、前記トランスインピーダンス変換回路(S2;S2’)は、少なくとも1つの差動ペア配線(AD、AD’)によって印加される直流電圧部分によって提供されることが提案される。  (もっと読む)

(もっと読む)

受動キーパッドにおける入力範囲間での区別化

【課題】受動キーパッドにおける入力範囲間での区別化をする。

【解決手段】スイッチS1...Snを有する受動回路網100のスイッチ投入を処理する方法および回路。受動回路網100は、スイッチ投入に応じて出力電圧を発生する。この回路は、受動回路網に結合され、出力電圧を基準電圧と比較する比較回路206を備えている。比較回路に結合されたデコーダ212は、出力電圧が所定の範囲内にある場合、スイッチ投入を復号化し、出力電圧が所定の範囲内にない場合、前記スイッチ投入を復号化しない。この回路は、意味あるキープレスの適切な処理ができると同時にうっかりとやったあるいは不注意なキープレスを無視し、それによって電力およびプロセッサ時間を確保する受動回路網キーパッドの入力範囲間で区別する。

(もっと読む)

半導体集積回路装置

【課題】本発明は、コストアップを抑制でき、かつ、異常履歴を得ることができる半導体集積回路装置を提供することを目的とする。

【解決手段】発振を行って発振信号を出力すると共に発振停止を検出したとき発振停止検出信号を出力し発振を再開する発振回路と、発振回路が出力する発振停止検出信号をエラーフラグとして保持するレジスタと、発振回路が出力する発振停止検出信号からリセット信号を生成して機能モジュールをリセットするリセット制御部と、機能モジュールのリセット後、レジスタからエラーフラグを読み出して不揮発性メモリに記憶する記憶制御手段を有する。

(もっと読む)

半導体集積回路

【課題】保護素子の半壊等によって外部電源端子からチップ内部へリーク電流が流れるようになった場合に、これを検出して外部へ報知することが可能な半導体集積回路を提供する。

【解決手段】外部電源端子に接続された保護素子(11)と、該保護素子に流れるリーク電流を検出する電流検出回路(12)とを備え、前記保護素子に所定以上の電流が流れた場合に検出信号を出力するように構成した。さらに、周期的な入力によって内部が周期的にリセットされ、周期的な入力がなくなるとアラーム信号を出力するウォッチドッグタイマ回路(14)を設け、ウォッチドッグタイマ回路から出力されるアラーム信号と前記検出信号との論理積もしくは論理和をとった信号を外部へ出力するように構成した。

(もっと読む)

出力バッファ回路及び出力バッファシステム

【課題】出力回路のスイッチング素子の短絡による破壊を確実に防止することが可能な出力バッファ回路及びそれを複数備えた出力バッファシステムを提供する。

【解決手段】第1の上側スイッチング素子4の他方の主端子と第1の下側スイッチング素子5の一方の主端子とを接続する部分が外部への出力部6を構成する第1の出力回路2と、出力端子が第1の出力回路2の出力部6に接続された第2の出力回路22と、第1の出力回路2の出力部6の短絡を検出する短絡検出回路24と、を備え、その起動時に、第1の出力回路2を動作させる前に第2の出力回路22を動作させて短絡検出回路24を動作させ、出力部6の短絡が検出されなかった場合に第1の出力回路2を動作させ、出力部6の短絡が検出された場合には第1の出力回路2を動作させないよう構成されている。

(もっと読む)

液晶表示装置

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

電流変動制御装置、半導体集積回路、電流変動制御方法および電流変動制御プログラム

【課題】面積を小さくでき、かつ、消費電流の変化を抑制して安定した動作を行う半導体集積回路の全体消費電流を制御する電流変動制御装置を提供する。

【解決手段】電流変動制御装置は、本来的用途に応じて設けられている複数の既存内部回路Bを選択的に活性化させて調整用の消費電流を生じさせる電流制御回路と、内部回路Aのリセット解除およびリセット投入を制御するリセット制御信号を出力するとともに電流制御回路に動作許可を与える動作許可信号を出力するリセット制御回路と、を備える。電流制御回路は、既存内部回路Bに活性化制御信号を出力し、内部回路Aのリセット解除前に既存内部回路Bを順次選択して活性化させることによりこれら既存内部回路Bによる調整用消費電流を徐々に上昇させ、内部回路Aのリセット解除時に既存内部回路Bの活性化を停止させる。

(もっと読む)

ドライバ回路

【課題】高速なデータパターンの時のみ周波数特性を改善して、所望の振幅を得ることが可能な送信側ドライバ回路を提供する。

【解決手段】第1のプルアップ抵抗回路P41、第3のプルアップ抵抗回路P43、第1のプルダウン抵抗回路N41、第3のプルダウン抵抗回路N43の抵抗値を第1の制御信号(SDATAP、SDATAM、DEMPHPP、DEMPHMN、DEMPHPN、DEMPHMP)に応じて変化させ、第2のプルアップ抵抗回路P42、第4のプルアップ抵抗回路P44、第2のプルダウン抵抗回路N42、第4のプルダウン抵抗回路N44の抵抗値を第2の制御信号(EMPHPP、EMPHPMN、EMPHPN、EMPHMP)に応じて変化させる

(もっと読む)

初期化信号出力回路、初期化信号出力制御方法

【課題】入力電源が複数ある場合において、複数の入力電源に対応した初期化信号出力回路において、回路規模の増大や消費電力の増大等を抑えること。

【解決手段】VDDAとVDDDとを含む複数の入力電源に基づいて、PORを出力するパワーオンリセット回路1であって、VDDAに基づいてPORの出力判断の基準となるCPinmを出力する基準電圧発生回路101と、VDDDの供給に応じてVDDAの電圧に応じたCPinpを出力する比較用電圧発生回路103と、CPinm及びCPinpの供給状態に応じてPORを生成する電圧比較器102と、VDDA及びVDDDの供給状態に応じてPORの出力を制御するパワーオンリセット制御回路104とを有することを特徴とする。

(もっと読む)

出力バッファ回路

【課題】伝送路にノイズが入った場合でも正常に通信ができる通信装置を提供する。

【解決手段】帰還増幅回路(2)と、帰還増幅回路(2)から供給される内部信号に応答して出力ノード(N1)に外部出力信号を供給する出力回路(3)と、帰還増幅回路(2)に対する帰還信号の供給を禁止する帰還遮断回路(4)とを具備する出力バッファ回路(1)を構成する。ここで、帰還増幅回路(2)は、入力端(N2)に入力される送信信号(TXD)と外部出力信号を帰還した帰還信号とに基づいて、内部信号の波形を制御する。そして、帰還遮断回路(4)は、出力ノード(N1)のノイズに基づいて生成される帰還遮断命令に応答して、帰還増幅回路(2)への帰還信号の供給を禁止する。

(もっと読む)

半導体集積回路装置

【課題】ESD保護回路を共通化してチップ面積を低減し且つESD保護回路が故障しても保護される複数の被保護回路が同時に動作不能となることを回避する。

【解決手段】点火回路4とダイアグ回路5の各ノードを同一極性のダイオード10〜12を通して共通ノード31に接続し、共通ノード31とESD保護回路6との間に切り離し回路23を備える。ESD保護回路6が短絡故障していないときには、ダイオード41は非導通、分圧電圧Vb>基準電圧Vrとなり、FET35がオフ、FET34がオン可能となる。ESD保護回路6が短絡故障すると、ダイオード41は導通、分圧電圧Vb<基準電圧Vrとなり、FET35がオン、FET34がオフとなり、共通ノード31とESD保護回路6とを電気的に切り離す。

(もっと読む)

141 - 160 / 418

[ Back to top ]