Fターム[5J055FX20]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 制御、帰還信号の特徴 (2,064) | 制御、帰還信号に閾値を有する (418)

Fターム[5J055FX20]に分類される特許

201 - 220 / 418

半導体集積回路

【課題】出力信号のステップパルスに伴う、不要な電磁輻射ノイズを低減する。

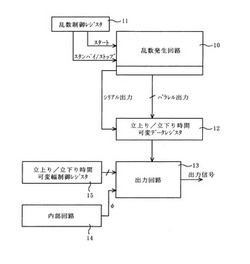

【解決手段】乱数制御レジスタ11は、乱数発生回路からの乱数データの出力のスタート(開始)、スタンバイ(待機)、ストップ(停止)、出力のタイミング等を制御するためのレジスタである。乱数発生回路10から出力された乱数データは、立上り/立下り時間可変データレジスタ12に格納される。立上り/立下り時間可変データレジスタ12に格納されるデータは、乱数発生回路10から順次発生される乱数データによって更新される。出力回路13は、マイクロコンピュータの内部回路14からの信号φを外部機器に出力するための回路であり、出力回路13の出力信号の立上り/立下り時間は、立上り/立下り時間可変データレジスタ12に格納された乱数データに応じて、可変制御されるようになっている。

(もっと読む)

出力装置、多値出力装置、及び半導体集積装置

【課題】ディエンファシス時と非ディエンファシス時の消費電流を一定にすることで、電源変動も一定となり、その結果ジッタの低減を可能にする出力装置を提供する。

【解決手段】入力されたデータを振幅制御して出力するデータ出力部1と、第1及び第2の振幅制御信号に基づいて伝送路に電流を重畳出力して伝送信号の振幅を制御する電流駆動部2と、第1及び第2の振幅制御信号に基づいて電流駆動部2との合計消費電流値が略一定となるように消費電流を制御するダミー電流駆動部3と、を備えて構成されている。

(もっと読む)

電圧制御形スイッチングデバイスのゲート駆動装置

【課題】電圧制御形スイッチングデバイスに過電流異常時に、迅速に定電流パルス出力、定電圧パルス出力を停止できる電圧制御形スイッチングデバイスのゲート駆動装置を提案する。

【解決手段】定電流パルス出力または定電圧パルス出力を発生する電流出力トランジスタまたは電圧出力トランジスタを含む定電流駆動回路または定電圧駆動回路を用い、定電流パルス出力または定電圧パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置である。閾値電圧を持った半導体スイッチ素子を有し、スイッチングデバイスの出力電流に応じて大きさが変化する検出電圧が、半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路を備え、このスイッチ出力に基づいて、電流出力トランジスタまたは電圧出力トランジスタの制御端子に、オフ制御電圧を供給する。

(もっと読む)

ドライバ装置

【課題】トランジスタの異常動作検出と異常信号出力の両機能を備えつつも小型化が図れるドライバ装置を提供する。

【解決手段】外部からの入力信号を受けてトランジスタを駆動制御するドライバ回路と、トランジスタのコレクタに接続されたセンス端子と、センス端子の電位と閾値電圧とを比較するコンパレータと、コンパレータの出力に基づいてセンス端子の電位を保持するラッチ回路と、コンパレータの出力に基づいてタイマー動作を開始するとともに所定時間経過後にセンス端子の電位の保持を解除するためのリセット信号をラッチ回路に出力するタイマー回路とを有し、センス端子の電位に基づいてトランジスタの異常動作を検出するセンス回路と、センス端子に接続され閾値電圧と同じかそれより高い電圧で動作し、異常信号を出力する異常信号出力回路とを備えている。

(もっと読む)

集積回路装置の短絡電荷共有技術

【課題】望ましい動作電圧レベルを得るべく制御される簡単な短絡トランジスタにより、2つまたはそれ以上の回路間における電荷共有を実現する。

【解決手段】短絡トランジスタはPチャネル金属酸化膜半導体(PMOS)デバイスまたはNチャネル金属酸化膜半導体(NMOS)デバイスのいずれかであり、電荷共有が起きる間での信号の起動を可能にする同じクロックを利用して制御されることができる。動作中、望ましい動作電圧レベルは、短絡トランジスタのゲートへの制御回路出力のパルス幅を増減することにより調整できる。

(もっと読む)

パワーオンリセット回路

【課題】電源電圧立ち上がりの緩急に拘わらず安定してリセット信号を生成することができるパワーオンリセット回路を提供する。

【解決手段】

発振信号生成回路110は、電源立ち上がりとともにCR発振回路111による発振を開始し、電源ラインVDDの電圧がダイオードD1の順方向電圧まで達したときに発振信号OSCの出力を開始する。発振検出回路120は、発振信号OSCを用いて電荷を蓄積し、蓄積電荷が与える電圧を発振検出信号SDとして出力する。リセット信号生成回路130は、発振検出信号SDの値がシュミットトリガインバータST1の動作しきい値に達したときに出力を反転させることにより、リセット信号PORを生成する。

(もっと読む)

ソリッドステートリレー

【課題】コストの上昇を抑制すると共に、異常動作を防止し、且つスナバ回路の抵抗近傍部品が故障してしまうことを防止することが可能なソリッドステートリレーを提供する。

【解決手段】ソリッドステートリレー20は、スナバ回路Sを構成するコンデンサC0と抵抗R0との接続点dと、トライアックTAのゲート端子Gとを接続する第3接続ライン28cを備えている。さらに、ソリッドステートリレー20は、第3接続ライン28c上に設けられた抵抗R2と、接続点eと接続点bとの間に設けられたコンデンサCとを備えている。

(もっと読む)

出力回路およびその方法、ならびに、サーマルヘッドドライバ、サーマルヘッド、電子機器、および印刷システム

【課題】 小さいサイズを有する、あるいは、電源電圧の変化に影響を受け難い出力回路等を提供する。

【解決手段】 出力回路(10;20;40;60)は、入力信号(IN)を入力し、第1の電位(VDD)および第2の電位(GND)に接続される第1のインバータ回路(12;22)と、第1のインバータ回路(12;22)からの信号を入力する第2のインバータ回路(14;24)と、第2のインバータ回路(14;24)からの信号を入力する出力トランジスタ(16;26;46)と、少なくとも1つの電流制限トランジスタ(18;28;48;68−1、68−2;108−1、118−2)と、を備える。少なくとも1つの電流制限トランジスタ(18;28;48;68−1、68−2;108−1、118−2)は、第1の電位(VDD)と第2の電位(GND)との間に、第1のインバータ回路(12;22)と直列に接続される。

(もっと読む)

電子回路のブートストラップポイント電圧を低下する方法、及びその方法を用いた装置

【課題】電子回路のブートストラップポイントの電圧を低下させる方法とそれを用いた装置を提供する。

【解決手段】シフトレジスタ回路等の電子回路において、ブートストラップポイント電圧レベルを低下させる放電装置を提供する。この回路において、第1トランジスタは、導通の際、入力パルスを受信し、入力パルスを第2トランジスタのゲート端に伝送して、第二トランジスタを導通状態にする。このゲート端がいわゆるブートストラップポイントである。入力パルスを受信した時、出力パルスが第2トランジスタのドレイン/ソース端に生成される。出力パルスの時間周期において、第1トランジスタは非導通態で、且つ、ブートストラップポイントは高電圧レベルにあり、第1トランジスタに対し電圧を印加する。放電回路は、少なくとも一つのトランジスタから構成され、ブートストラップポイントに接続されて、出力パルス周期内の電圧レベルを低下させる。

(もっと読む)

レギュレータ及び高電圧発生器

【課題】半導体メモリ装置の高電圧発生器の動作中に突然電源供給が中断される場合、チャージポンプから出力された高電圧が放電されず、レギュレータに含まれた比較部に入力端として入力され、トランジスタが劣化することを防止する。

【解決手段】チャージポンプ430の出力電圧を分配する電圧分配部444と、基準電圧と上記電圧分配部の分配電圧のサイズを比較する比較部442と、上記電圧分配部と接地端子を選択的に接続させるレギュレータ駆動部446と、電源電圧の供給遮断時にチャージポンプから出力された高電圧を放電させる高電圧放電部448を設ける。

(もっと読む)

PLLシンセサイザー回路

【課題】 電源変動等が生じると、外部からの割込信号により不定期間を待って再度分周データをPLLシンセサイザーICに書き込むことで、安定的にロック状態に復帰させることができるPLLシンセサイザー回路を提供する。

【解決手段】 PLLシンセサイザーIC106の電源投入時又は電源変動時にマイクロプロセッサ(CPU)104への割込を監視手段が発生させ、CPU104はPLLシンセサイザーIC106の電源投入後又は電源変動後の不定期間に相当する期間を待って、分周データをPLLシンセサイザーIC106に出力して書き込みを行い、更に分周データ出力後にロック状態となるまでの期間ウエイトするPLLシンセサイザー回路である。

(もっと読む)

リセット回路

【課題】リセット回路の回路規模を小さくする。

【解決手段】電源電圧の電圧レベルに応じて、電源電圧を用いる回路に対してリセット指示又はリセット解除を示すリセット信号を出力するリセット回路であって、電源電圧が所定の第1閾値レベルより高いかどうかを検出する電圧検出回路と、電圧検出回路の検出結果に基づいて、電源電圧が第1閾値レベルより高い場合にキャパシタを充電し、電源電圧が第1閾値レベルより低い場合にキャパシタを放電する充放電回路と、キャパシタの電圧が所定の第2閾値レベルより低い場合、リセット指示を示す一方の論理レベルにリセット信号を変化させ、キャパシタの電圧が第2閾値レベルより高い場合、リセット解除を示す他方の論理レベルにリセット信号を変化させるMOSインバータ回路とを備える。

(もっと読む)

信号出力回路、検出スイッチ及び多光軸光電スイッチ

【課題】双方向整流素子の漏れ電流による影響を抑制することが可能な信号出力回路、検出スイッチ及び多光軸光電スイッチを提供する。

【解決手段】信号出力回路29は、出力端子43に第1スイッチング回路30に対応する負荷50が接続されたときに当該負荷のローレベルライン側に接続される一方で、出力端子43に前記第2スイッチング回路30に対応する負荷60が接続されたときに当該負荷のハイレベルライン側に接続される接続端子44と、前記接続端子44レベルがローレベルの場合に前記第1スイッチング回路30からの出力信号S1を前記出力端子43に与え、前記接続端子44レベルがハイレベルの場合に前記第2スイッチング回路30からの出力信号S1を前記出力端子43に与える選択手段を備え、前記出力端子43と前記接続端子44との間に双方向整流素子70が設けられている。

(もっと読む)

IC内のヒューズ・プログラミング電流を制御するためのシステムおよび方法

【課題】自動的に適切なプログラミング電流を決定して印加するためのシステムを提供する。

【解決手段】システムは、複数の測定ヒューズに複数の相違する電流を流し、複数の測定ヒューズの対応するものを破壊することなく切断した1つまたは複数の電流を特定し、特定された電流のうちの1つを自動的に選択するように構成されている測定回路と、選択された電流で1つまたは複数の目標ヒューズをプログラムするように構成されているプログラミング回路と、を具備する。

(もっと読む)

半導体集積回路装置

【課題】簡単な構成のインピーダンス調整回路を備えた半導体集積回路装置を提供する。

【解決手段】第1インピーダンスコードにより出力インピーダンスが可変にされてなる複数組の出力回路と外部端子に接続された第1抵抗素子に対応して上記第1インピーダンスコードを生成する第1インピーダンス制御回路と有する。上記第1インピーダンス制御回路は、上記第1インピーダンスコードをシリアルデータに変換して送出するエンコーダを有する。上記複数組の出力回路のそれぞれは、上記シリアルデータを受けて上記第1インピーダンスコードを再生するデコーダを有する。

(もっと読む)

電流増幅半導体素子の駆動回路

【課題】 電流増幅半導体のベース電流をコレクタ電流に応じた必要最小限の値に制御するようにし、高速で低消費電力の電流増幅半導体素子の駆動回路を提供する。

【解決手段】 2個の直流電源の正側電源2の正極と負極の間に、チョッピング用スイッチング素子4とインダクタ6と被制御電流増幅半導体1のベース及びエミッタとの直列回路を接続するとともに、チョッピング用スイッチング素子とインダクタの接続点に該接続点側にカソード及び負側電源3の負極にアノードとなるようダイオード8を接続し、被制御電流増幅半導体のベースと負側電源の負極間に制御用スイッチング素子7を接続した回路構成をなし、被制御電流増幅半導体のコレクタ及びエミッタ間の電圧を検出し、被制御電流増幅半導体がオン状態時に、該電圧が準飽和電圧近辺の2値間になるようにチョッピング用スイッチング素子のオンオフ期間を制御する制御回路5を有する電流増幅半導体の駆動回路。

(もっと読む)

オートクリア回路

【課題】リセット信号の発生をより簡便な設計により達成することが可能なオートクリア回路を提供する。

【解決手段】電源電圧Vccを有する電源端子V1に接続され、電源電圧Vccより低い2次電圧Vaを出力する電圧供給端子V2を有する電圧供給手段10と、電圧供給端子V2とノードNN及びノードNBとの間に接続されたスイッチ手段11と、ノードNNと接地端子との間に接続され、ノードNNの電位を分割したノード電位VNAを出力する電位分割手段12と、ノードNBと接地端子との間に接続され、電位分割手段12が出力したノード電位VNAに基づいてノードNBを充電又は放電する充放電手段13と、ノードNBの電位を保持して信号を出力端子15より出力すると共に、信号をスイッチ手段11に与えて開閉動作を制御するラッチ手段14とを備える。

(もっと読む)

電子制御システム及び方法

【課題】電子制御システム内の装置が2線又は3線動作を可能にする。

【解決手段】電源(150)は、2線及び3線装置の両方において、閉回路に電力を供給することができる。2つの別々のゼロクロス検出器が、2線及び3線の両方の装置内でタイミング情報を収集できるような形で使用される。両方のゼロクロス検出器(110)が監視され、電子制御を自動的に構成するために使用される。過電圧回路は、オフ状態にあるMOSFETを横断して過電圧状態を検知し、望ましくはアバランシェ領域に達することがないようにMOSFETをオンに切換える。過電流回路は、MOSFETを通る電流が予め定められた電流閾値を上回った時点でそれを検知し、その後、そのMOSFETの安全動作領域(SOA)曲線を超えないようにMOSFETをオフに切換える。

(もっと読む)

内部クロックドライバ回路

【課題】本発明は、動作周波数の制限なく、ライジングDLLクロックとフォーリングDLLクロックのオーバーラップがない内部クロックドライバ回路を提供する。

【解決手段】本発明に係る内部クロックドライバ回路は、ライジングクロックとフォーリングクロックを遅延させて遅延ライジングクロックと遅延フォーリングクロックを出力する遅延部と、前記ライジングクロック、前記フォーリングクロック、および前記遅延ライジングクロックの入力を受けて組み合わせてライジングDLLクロックを出力するライジングDLLクロック生成部と、前記ライジングクロック、前記フォーリングクロック、および前記遅延フォーリングクロックの入力を受けて組み合わせてフォーリングDLLクロックを出力するフォーリングDLLクロック生成部とを含む。

(もっと読む)

電力損失が低減されたMOSFETゲートドライブ

たとえばDC/DCコンバータにおける、電力用MOSFETに対するゲートドライバは、MOSFETを完全オン状態と完全オフ状態との切換えに代えて、完全オン状態と低電流状態とを切換える。それによって、MOSFETのゲートを充電および放電するために伝達されるべき電荷量は減少され、かつMOSFETの効率が改善される。フィードバック電流は、MOSFETの電流の大きさがその低電流状態において正しいことを保障するために用いられてもよい。あるいは、トリミングプロセス(微調整過程)は、低電流状態において、ゲートドライバによって電力用MOSFETのゲートに供給される電圧の大きさを修正するために用いられてもよい。  (もっと読む)

(もっと読む)

201 - 220 / 418

[ Back to top ]