Fターム[5J055FX20]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 制御、帰還信号の特徴 (2,064) | 制御、帰還信号に閾値を有する (418)

Fターム[5J055FX20]に分類される特許

81 - 100 / 418

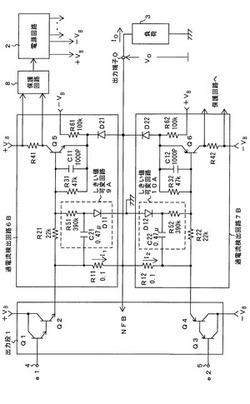

電力増幅器の過電流検出回路及びその方法

【課題】 しきい値を的確に可変して過電流検出の誤作動を防止する。

【解決手段】 過電流検出回路6Bは、Q2のエミッタと出力端子Oの間の電流検出抵抗R11の両端間に抵抗R21、R31が接続されている。R31の両端が過電流検出トランジスタQ5のベース−エミッタ間に接続されており、出力端子Oと−VB の間にダイオードD21、抵抗R61が接続されており、D21のカソードがQ5のエミッタと接続されている。R21とR31の接続点とグランド間には抵抗R51とD11が接続されており、R51とD11の接続点とQ2のエミッタの間にコンデンサC21が接続されている。R51、D11、C21のしきい値可変回路9Aは出力電圧の大きさが大きくなるとしきい値を大きくし、出力電圧の大きさが小さくなるとしきい値を小さくするが、C21とD11により、出力電圧の大きさが増加するときはしきい値を早く増大変化させ、減少するときはしきい値をゆっくり減少変化させる。

(もっと読む)

電子回路

【課題】

内部電源電圧を遮断するパワーダウンモードへの移行を誤動作無く確実に実行するパワーダウンモードの移行シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧から降圧してシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する第1の内部回路30と、電源電圧を供給されて動作する入出力回路24と、第1の内部回路30からの信号を入力し、電源電圧の電圧レベルに変換するレベルシフタ23と、システム電圧発生回路10を制御する制御回路40とを備え、制御回路40は起動信号P4を入力し、この起動信号に所定の遅延時間を与えた短絡制御信号P5を出力する遅延回路100を有し、起動信号はレベルシフタ23を非活性又は活性として制御し、短絡制御信号はシステム電圧発生回路10を停止状態又は動作状態として制御する構成とした。

(もっと読む)

クロック生成装置、クロック切り替え方法及びプログラム

【課題】クロック生成装置に接続されるスレーブ装置の数が変化し、接続先の負荷容量が変動したとしても、クロック生成装置とスレーブ装置間で定められた切り替え仕様を満たすクロック選択信号を出力する。

【解決手段】クロック生成装置は、スレーブ装置実装検出部において接続されたスレーブ装置の数を検出し、その検出数をバッファタイプ選択部に通知する。バッファタイプ選択部においては、この通知に基づきクロック選択信号を出力する際のバッファタイプを選択する。

(もっと読む)

パワーオンリセット回路

【課題】誤動作を起こす可能性があった。

【解決手段】電源投入初期もしくは電源電圧降下時にリセット信号を発生し初期化するパワーオンリセット回路であって、電源電圧に応じた電圧を分圧した第1の比較電圧を生成する第1の比較電圧生成部と、電源電圧に応じた第1の電圧を出力する基準電圧生成部と、電源電圧端子と第1のノードとの間に接続され、制御端子に前記第1の電圧を入力するデプレッション型の第1のトランジスタと、前記第1のノードと接地端子との間に接続され、制御端子が前記第1のノードに接続されるエンハンスメント型の第2のトランジスタと、を備え、前記第1のノードの電位に応じた電圧を第2の比較電圧として生成する第2の比較電圧生成部と、前記第1、第2の比較電圧との比較結果に応じてリセット信号を出力する比較器と、を有するパワーオンリセット回路。

(もっと読む)

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

信号保持回路およびこれを使用したシステム保護装置

【課題】電源電圧が低下したときに信号保持回路での信号保持を確実に解除する。

【解決手段】出力端子toを複数の入力端子のうちの1つtbに接続し、残りの外部入力端子taに外部信号が入力される論理和回路14と、該論理和回路14の出力端子に接続された単一パルスを生成するパルス生成回路15とを備え、前記論理和回路14の前記外部入力端子tbにハイレベルのパルス信号が入力されたときに、当該論理和回路14の出力をハイレベルに保持する信号保持回路13であって、前記論理和回路14の前記出力端子toと前記入力端子tbとの間に、電源電圧低下時に当該論理和回路14によるハイレベル保持状態を解除する電圧を高めるダイオードDを介挿した。

(もっと読む)

半導体装置及び電子機器

【課題】消費電力を低減することができる半導体装置及びそれを用いた電子機器を提供す

ることを課題とする。

【解決手段】本発明の半導体装置は、高電位電源から第1の電位が供給され、低電位電源

から第2の電位が供給され、入力ノードに第1の信号が入力されると、出力ノードから第

2の信号を出力する。本発明の半導体装置は、第2の信号の電位差を、第1の電位と第2

の電位の電位差よりも小さくすることにより、配線の充電と放電に伴う消費電力を低減す

ることができる。

(もっと読む)

スイッチングレギュレータ

【課題】 小型・低雑音のスイッチングレギュレータを提供する。

【解決手段】 導通、遮断の2状態が交互に切り替わる複数のトランジスタで構成されたスイッチングレギュレータの出力段と、その出力段トランジスタを各々個別に駆動するための駆動回路から構成され、当該駆動回路は、各々出力段トランジスタにおける遮断から導通状態への遷移時間が、導通から遮断状態への遷移時間に比べて長くなるように立ち上がり、立ち下がり時の駆動能力をアンバランスに設定され、各々の遷移時間は、出力信号の電位があらかじめ設定された電位に達したことを判定して変化させることを特徴とするスイッチングレギュレータとして構成される。

(もっと読む)

レベルシフト回路

【課題】消費電力低下および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2は、第1入力端子11、第2入力端子12、第1出力端子21、第2出力端子22、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41、第2NMOSトランジスタ42、第1ブートストラップ回路51および第2ブートストラップ回路52を備える。第1ブートストラップ回路51は、第1充電用スイッチ511,第1転送用スイッチ512,第1容量部513および第1インバータ回路514を含む。第2ブートストラップ回路52は、第2充電用スイッチ521,第2転送用スイッチ522,第2容量部523および第2インバータ回路524を含む。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、インバータとして機能する回路(3つのトランジスタTr21,Tr22,Tr23)と、トランジスタTr21,Tr22のゲート電圧Vgの補正を行う閾値補正回路21とを有している。閾値補正回路21は、トランジスタTr21,Tr22のゲートに対して、トランジスタTr21,Tr22の閾値電圧Vth1,Vth2をオフセットとして設定するようになっている。

(もっと読む)

半導体装置

【課題】終端抵抗のオンオフの切り替え時に外部端子にインピーダンスの急激な変化が生じることを低減する。

【解決手段】外部端子(図2のDQに相当)と、外部端子に接続され、出力信号を外部端子に出力可能とする出力回路(図2の21に相当)と、外部端子に終端抵抗をオンオフ可能に接続する終端回路(図2の22に相当)と、終端抵抗がオフ状態又はオン状態のいずれか一方の状態から他方の状態に変化するまでの時間を、データ出力時に出力信号が一方の論理レベルから他方の論理レベルへ変化するまでの時間以上となるように制御する第1のスルーレート制御回路(図2の23aに相当)と、を備える。

(もっと読む)

半導体集積回路装置

【課題】電源投入手順によらずに安定した動作を行う入出力回路の制御を、回路規模の増大を抑え、チューニングが不要なデジタル回路のみで実現する集積回路を提供する。

【解決手段】信号発生器113で生成した信号を、レベルシフト回路111で電源電圧Vcc2の信号振幅へ変換する。次にVcc2の信号振幅に変換したものを、もう一度レベルシフト回路112で内部電源電圧Vcc1の信号振幅へ変換して、フィードバック信号を生成する。比較器114で信号発生器113が生成したオリジナルの信号と、2つのレベルシフトを経て生成された、フィードバック信号とを論理的に比較し、一致しない場合にはVcc2の電源が遮断されていると見なして、入出力回路115での不定伝播を防止するように制御を行う。

(もっと読む)

半導体装置

【課題】入力信号のHレベルまたはLレベルを正しく検知できる半導体装置を提供する。

【解決手段】半導体装置100は、閾値調整信号に基づいて論理閾値電位を調整可能な入力バッファ(入力CMOS回路11)と、入力バッファの入力と出力とが結線されたレプリカ(レプリカ12)と、予め設定された基準電位(ノードNdHの電位)を発生する基準電位発生回路(基準電位発生回路13)と、レプリカ(レプリカ12)の出力電位(ノードNdRの電位)と基準電位(ノードNdHの電位)とを比較し、閾値調整信号(閾値調整信号CTRL)を入力バッファ(入力CMOS回路11)とレプリカ(レプリカ12)とに出力する比較回路(比較回路14)と、を備える。

(もっと読む)

出力バッファ回路、入力バッファ回路、及び入出力バッファ回路

【課題】スルーレートを適切に調整可能なバッファ回路を提供する。

【解決手段】

CMOS出力バッファ回路は、バッファ回路Buffer[1]〜[4]を備えている。各バッファ回路は、電源電圧端子又は接地端子と出力端子との間にトランジスタPO及びNOを有している。各バッファ回路中の複数個のトランジスタPO及びNOは、外部からの制御信号に従い選択的に動作可能な状態とされる。各バッファ回路中の3個のトランジスタPOは、所定のサイズ比を有するように形成されている。

(もっと読む)

ポジションスイッチの出力判定装置

【課題】長期間使用した場合でも、常に適正なスイッチ位置の判定を行うことができるポジションスイッチの出力判定装置を提供する。

【解決手段】本発明に係わるポジションスイッチの出力判定装置(20)は、少なくとも2つの位置間の変位により、第1電圧レベルまたは当該第1電圧レベルと異なる第2電圧レベルとを出力するポジションスイッチ(10)の出力判定装置であって、前記第1電圧レベルと前記第2電圧レベルとの間での切り替りを判定するための判定電圧レベルを記憶する記憶手段(21)と、前記ポジションスイッチから出力された電圧レベルが、前記判定電圧レベルを跨いで変化したときに、当該変化の前後で検出した前記第1電圧レベルと前記第2電圧レベルとの中間の電圧レベルを検出し、当該検出した電圧レベルを前記判定電圧レベルとして前記記憶手段の記憶内容を更新する制御手段(22)と、を備える。

(もっと読む)

論理回路及び半導体装置

【課題】クロックゲーティングを行う論理回路において、待機電力を低減すること又は誤動作を抑制すること。

【解決手段】論理回路は、クロック信号が供給されない期間に渡って、ソース端子及びドレイン端子に電位差が存在する状態でオフするトランジスタを有する。該トランジスタのチャネル形成領域は、水素濃度が低減された酸化物半導体によって構成される。具体的には、当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該論理回路の待機電力を低減すること及び誤動作を抑制することができる。

(もっと読む)

半導体記憶装置および昇圧回路

【課題】回路面積の削減しつつ、消費電流やピーク電流の増大を抑制することが可能な半導体記憶装置を提供する。

【解決手段】昇圧回路は、第1ないし第4の整流素子と、第1ないし第4のMOSトランジスタと、第1ないし第4のキャパシタと、スイッチ回路と、を備える。スイッチ回路は、第1のMOSトランジスタの他端と第3の整流素子の一端との間の第1の接続点、および、第2のMOSトランジスタの他端と第4の整流素子の一端との間の第2の接続点に接続された低レベル端子と、第3のMOSトランジスタの他端、および、第4のMOSトランジスタの他端に接続された高レベル端子と、を有し、低レベル端子の電圧または高レベル端子の電圧を切り換えて、出力端子に出力するスイッチ回路と、を含む。

(もっと読む)

高耐圧スイッチ回路およびそれを用いた半導体集積回路装置

【課題】 双方向スイッチにおいて、ドレイン電圧またはドレイン-ソース間電圧に基づいて、上記スイッチのゲート-ソース間電圧を制御する手段と、上記制御手段を介して、上記スイッチのゲート端子に電圧を印加するスイッチドライバとを備えている双方向スイッチを提供する。

【解決手段】 双方向スイッチであるメインスイッチと、上記メインスイッチのゲート-ソース間電圧を、上記メインスイッチのドレイン電圧、ソース電圧に基づいて制御する手段と、上記制御手段を介して上記メインスイッチのゲート端子に電圧を印加するスイッチドライバとを備えている双方向スイッチを構成する。

(もっと読む)

81 - 100 / 418

[ Back to top ]