Fターム[5J056GG07]の内容

論理回路 (30,215) | 制御対象、制御態様 (2,427) | 出力電圧を制御するもの (1,446) | 段階的に制御するもの (1,382)

Fターム[5J056GG07]の下位に属するFターム

時間遅延を利用するもの (128)

あるノードの電位を利用するもの (888)

あるノードの電流を利用するもの (185)

Fターム[5J056GG07]に分類される特許

21 - 40 / 181

半導体装置

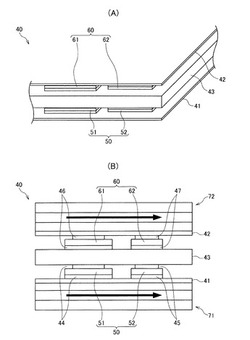

【課題】半導体素子の劣化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置40は、正極41及び負極42と、正極41と負極42の間に配置される出力電極43と、正極41と出力電極43を接続する正側スイッチング素子51と、正極41と出力電極43を接続し、正側スイッチング素子51とは電流を逆方向に流す正側ダイオード52と、負極42と出力電極43を接続する負側スイッチング素子61と、負極42と出力電極43を接続し、負側スイッチング素子61とは電流を逆方向に流す負側ダイオード62と、を備える。正極41及び負極42の電極厚さは、出力電極43の電極厚さよりも薄く設定される。

(もっと読む)

入出力回路、半導体制御システム、および入出力回路の制御方法

【課題】デジタル信号を高速で送受信するための入出力回路を、EM耐性を保ちつつ、小さな回路面積で、実現する。

【解決手段】出力バッファ21は、電源−グランド間に接続されたトランジスタTP1,TN1と、ノードn1と入出力端子23との間に接続された抵抗素子R1とを備え、出力バッファ22は、電源−グランド間に接続されたトランジスタTP2,TN2と、ノードn2と入出力端子23との間に接続された抵抗素子R2とを備えている。信号入力モードにおいて、出力バッファ21,22によって1つの終端回路を構成する。例えば、トランジスタTP1,TN2をON、トランジスタTN1,TP2をOFFにし、抵抗素子R1,R2を通る電流パスを形成する。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減する。

【解決手段】内部回路(LK#2)の内部ノードに対応して対応の内部ノードの信号をラッチする複数のラッチ回路(F1−F7)をテストパス(302)に配置する。内部回路のMISトランジスタは、ラッチ回路のMISトランジスタよりスタンバイ状態時にゲートトンネル電流が低減される状態に設定される。

(もっと読む)

半導体装置及び制御方法

【課題】メモリの出力バッファの平均電流値を低減し、消費電流を抑制すること。

【解決手段】本発明に係る半導体装置は、メモリリードアドレスDの連続性を判定し、判定結果Hを出力するアドレス連続性判定回路23と、判定結果Hに基づいて、メモリリードアドレスDに対応するリードデータを出力するメモリの出力バッファ22の駆動能力を制御する駆動能力切り替え制御回路24と、CPUの要求リードアドレスAに対応するリードデータが当該CPUへ到達するまでの期間に、CPU要求リードアドレスAに連続する予想アドレスを生成するアドレス生成部12と、予想アドレスに対応するリードデータを格納するプリロードバッファ14を備える。

(もっと読む)

多値記憶手段、多値バッファ手段および双方向性スイッチング手段

【課題】C・MOS・FET等の相補型3端子スイッチング手段を用いたオン・オフ駆動手段も使用できる双方向性スイッチング手段を提供する。

【解決手段】どちらも両主電極の役割がその印加電圧の方向により互いに入れ換わることができ、どちらも互いに相補関係に有る2つのオン・オフ制御スイッチング手段が有って、その両オン・オフ制御スイッチング手段のうち一方の主電極と他方の主電極を接続し、一方の開放された主電極と一方の制御電極の間に一方のオン・オフ駆動手段を設け、一方の開放された主電極と他方の制御電極の間に他方のオン・オフ駆動手段を設け、その両オン・オフ制御スイッチング手段の直列回路を双方向性のスイッチとして使用する。

(もっと読む)

電気光学装置、シフトレジスタ回路および半導体装置

【課題】ゲート線駆動回路の領域を効率よく利用できると共に、ゲート線選択信号の立ち上がり速度の低下(立ち上がり遅延)を防止できる電気光学装置、並びに、それに適した単一導電型のトランジスタで構成されたシフトレジスタ回路を提供する。

【解決手段】ゲート線駆動回路30は、複数のゲート線GLの奇数行を駆動する奇数ドライバ30aと、偶数行を駆動する偶数ドライバ30bとから成る。奇数および偶数ドライバ30a,30bの単位シフトレジスタSRの各々は、2行前の選択信号Gk-2を受け、その2水平期間遅れて自己の選択信号Gkを活性化させる。偶数ドライバ30bのスタートパルスSP1は、奇数ドライバ30aのスタートパルスSP2よりも1水平期間だけ位相が遅れている。

(もっと読む)

レベルシフト回路

【課題】レベル変換における動作範囲を広くする。

【解決手段】第1の電位(VDD1)の波高値を有する入力パルス信号(VIN)を入力するCMOSインバータ回路(P1、N1)と、第1の電位よりも高電位となる第2の電位(VDD2)の電源で動作し、一端(ND1)をCMOSインバータ回路の出力端に接続し、他端から第2の電位の波高値を有し入力パルス信号と同相の出力パルス信号(VOUT)を出力するラッチ回路(INV1、P3)と、第1の電位以上かつ第2の電位未満の電源供給をCMOSインバータ回路に対して行う電源供給回路(P2、INV2)と、を備え、電源供給回路は、入力パルス信号が少なくとも接地レベルとなる場合に電源供給を制限するように機能する。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】スタンバイ時における半導体装置の消費電力を低減する。

【解決手段】スタンバイ時においてハイレベルを出力すべき論理回路については、一対の電源ノードを擬似電源線VDDT1L,VSSTLに接続し、スタンバイ時においてローレベルを出力すべき論理回路については、一対の電源ノードを擬似電源線VDDTL,VSST1Lに接続する。スタンバイ時における擬似電源線VDDTL,VDDT1L,VSSTL,VSST1Lの電位VDDT,VDDT1,VSST,VSST1は、VDDT<VDDT1<VDD、VSST>VSST1>VSSを満たす。これにより、スタンバイ状態においてオンするトランジスタのゲート電極と基板との間を流れるリーク電流や、スタンバイ状態においてオフするトランジスタのドレインと基板との間を流れるリーク電流が低減される。

(もっと読む)

プリエンファシス機能を含む出力回路と半導体装置

【課題】プリエンファシス機能を有する出力回路において、デエンファシス時における差動出力信号のコモンモード電圧のプリエンファシス時のコモンモード電圧からの変動を抑制する。

【解決手段】入力信号とその相補信号とを差動入力して差動出力し、差動出力信号のうち高電位側の出力信号にデエンファシスをかける際に、当該デエンファシス電流を供給するトランジスタ(N3、N4)に流れる電流を絞る回路(N5、N6、R3)を備え、デエンファシス時の前記出力信号のハイレベルの前記出力信号のプリエンファシス時のハイレベルからの変化量を縮減させ、デエンファシス時の前記差動出力信号のコモンモード電圧をプリエンファシス時のコモンモード電圧に近づける。

(もっと読む)

半導体集積回路

【課題】入力信号の立ち上がり時と立ち下がり時で遷移時間差の少ないレベルシフト回路を提供する。

【解決手段】同じ回路構成のVDD 電源系の第1、第2のレベルシフタ11、12と、VEXTQ 電源系のインバータ13と、VDD 電源系のインバータ15を具備し、第1のレベルシフタ11内の2個の入力用NMOSトランジスタTN1 、TN2 のゲート端子には、VEXTQ 電源系の入力信号INとインバータ13の出力信号を入力し、第2のレベルシフタ12内の2個の入力用NMOSトランジスタTN3 、TN4 のゲート端子には、第1のレベルシフタ11の出力ノードA2の信号とインバータ13の出力信号を入力し、第2のレベルシフタ12の出力ノードA4の信号をインバータ15により波形整形して出力信号OUT を得る。

(もっと読む)

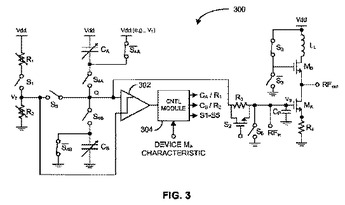

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

集積回路装置及び電子機器

【課題】通常動作モード、低消費電力動作モードでの省電力化等を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第1の電源電圧VDDAを出力する第1のレギュレーターRG1と、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第2の電源電圧VDDBを出力する第2のレギュレーターRG2と、第1の電源電圧VDDAが供給され、通常動作モード及び低消費電力動作モードにおいて動作する第1のロジック回路LG1と、第2の電源電圧VDDBが供給され、通常動作モードにおいて動作し、低消費電力動作モードでは非動作になる第2のロジック回路LG2を含む。

(もっと読む)

半導体記憶装置および昇圧回路

【課題】回路面積の削減しつつ、消費電流やピーク電流の増大を抑制することが可能な半導体記憶装置を提供する。

【解決手段】昇圧回路は、第1ないし第4の整流素子と、第1ないし第4のMOSトランジスタと、第1ないし第4のキャパシタと、スイッチ回路と、を備える。スイッチ回路は、第1のMOSトランジスタの他端と第3の整流素子の一端との間の第1の接続点、および、第2のMOSトランジスタの他端と第4の整流素子の一端との間の第2の接続点に接続された低レベル端子と、第3のMOSトランジスタの他端、および、第4のMOSトランジスタの他端に接続された高レベル端子と、を有し、低レベル端子の電圧または高レベル端子の電圧を切り換えて、出力端子に出力するスイッチ回路と、を含む。

(もっと読む)

スイッチトキャパシタ型積分器

【課題】待機電流を抑制することによって、低消費電力のスイッチトキャパシタ型積分器を実現する。

【解決手段】φ1において入力信号の電荷をサンプリングするサンプルキャパシタC1と、φ2においてサンプルキャパシタC1の電荷を仮想ノード4を介して累積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1,MN1と、主トランジスタMP1,MN1のゲート端子と仮想接地ノード4の間に挿入された校正キャパシタC3,C4と、φ1において校正キャパシタC3,C4に対して、仮想ノード4が基準電位Vcmにあるときの主トランジスタMP1,MN1のゲート・ソース間電圧が略閾値電圧となる電位差が生じるように電荷を供給する校正装置12と、を有する。

(もっと読む)

半導体集積回路

【課題】外部負荷を駆動する入出力回路を有するデジタル回路と、外部回路と通信を行う通信回路を備えるアナログ回路とを混載して成る半導体集積回路において、入出力回路による内部発生ノイズを低減し、アナログの通信回路における通信エラーの発生を抑える。

【解決手段】外部負荷となるメモリ5を駆動する入出力回路3とCPU2とを有するデジタル回路と、イーサーネットによって外部回路と通信を行う通信回路41を備えるアナログ回路4とを混載して成る半導体集積回路1において、前記入出力回路3と電源VDDとの間に電圧調整回路6を介在して、入出力回路3への供給電源電圧VDD’を可変にする。そして、CPU2が前記通信回路41からエラー通知F2を受信すると、電圧制御回路6へ電圧制御信号F3を出力し、前記入出力回路3の動作を保証できる下限電圧までの範囲で、パッド31,32に加わる電圧を低下させ、ノイズF1を抑える。

(もっと読む)

半導体集積回路およびその調整方法

【課題】一対の信号線に差動の信号を出力する差動出力駆動回路を備える半導体集積回路において、立ち上がり時間と立ち下がり時間とをそれぞれ独立に調整できるようにする。

【解決手段】一対の信号線4a,4bのそれぞれとGNDとの間に出力容量Ca,Cbを備えるとともに、それぞれの信号線4a,4bに直列に第1の抵抗R1a,R1bを介在し、かつ前記信号線4a,4bを第2の抵抗R2a,R2bによって電源電位にプルアップする。そして、該半導体集積回路1を基板に実装した後に測定された立ち上がり時間と立ち下がり時間とに応じて、抵抗値調整回路Aa,Abが、前記抵抗R1a,R2a;R1b,R2bの抵抗値をそれぞれ調整する。したがって、立ち上がり時間と立ち下がり時間とをそれぞれ独立に調整できるようになり、それらの対称性を維持しなければならないような規格に対しても対応可能となる。

(もっと読む)

供給ノイズおよび終端ノイズの低減方法およびシステム

【課題】 SSNに関連する問題を軽減するシステムおよび方法を提供すること。

【解決手段】 シングルエンドの通信チャネルを介して第1の集積回路(IC)が第2のICと通信する通信システムを開示する。双方向基準チャネルは、第1のICおよび第2のIC間に延在し、両エンドで終端される。基準チャネルの各エンドにおける終端インピーダンスは、信号を異なる方向に通信するための異なるモードをサポートする。基準チャネルの終端インピーダンスは、それぞれの信号方向に最適化されることができる。

(もっと読む)

半導体集積回路装置

【課題】簡便かつ小さな面積の回路で、高電圧から低電圧へのレベルシフト回路を具備する半導体集積回路装置を提供すること。

【解決手段】高電圧で動作する高電圧回路と、低電圧で動作する低電圧回路と、高電圧回路の信号を低電圧回路の信号に電圧変換するレベルシフト回路とを備えた半導体集積回路装置であって、レベルシフト回路は、ドレイン電極が高電圧回路に接続され、ソース電極が低電圧回路に接続され、ソース電極に低電圧が印加され、ドレイン及びゲートが高電圧に耐える構造を備えているデプレッション型NMOSトランジスタで構成した。

(もっと読む)

半導体集積回路装置

【課題】電源遮断時にそれ以前の情報を保持する低消費電力モードにおいてその復帰を高速にする。その一つに従来のデータ保持型フリップフロップを用いることが考えられるが、そのためにセルを大きくする等の面積オーバーヘッドが生じるのは望ましくない。

【解決手段】電源遮断時のデータ保持のための電源線は一般の電源幹線よりも細い配線にて形成する。望ましくは、データ保持回路の電源を信号線扱いとして、自動配置配線時に配線することである。そのために、セルにはあらかじめ上記データ保持回路用電源のための端子を通常の信号線と同様に設けて設計しておく。[効果]セルに余分な電源線のレイアウトが不要となり省面積化が図られるとともに、既存の自動配置配線ツールにより設計が可能となる。

(もっと読む)

21 - 40 / 181

[ Back to top ]