Fターム[5J081DD11]の内容

LC分布定数、CR発振器 (9,854) | 発振用能動素子とその接続 (1,031) | 複数素子の組合せ (353) | エミッタ・ソース・カソード共通接続 (234) | 差動 (226)

Fターム[5J081DD11]の下位に属するFターム

ダブルバランス (4)

Fターム[5J081DD11]に分類される特許

1 - 20 / 222

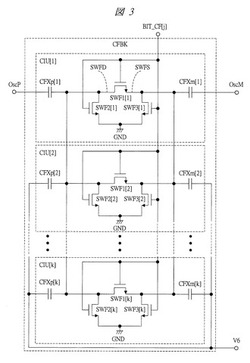

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

電圧制御発振器および関連システム

【課題】位相雑音および出力が改善された電圧制御発振器および関連システムを提供する。

【解決手段】電圧制御発振器は、第1の可変静電容量素子(120)と、第2の可変静電容量素子(122)と、可変静電容量素子(120、122)間に結合され、出力ノード(104)において、発振信号の振動周波数において可変静電容量素子(120、122)の間にインダクタンスを提供する誘導素子(132)とを含む。第1の可変静電容量素子(120)は第1の制御電圧ノード(110)および出力ノード(104)の間に結合され、第2の可変静電容量素子(122)は第1の制御電圧ノード(110)に結合され、第2の誘導素子(134)は第2の可変静電容量素子(122)および第2の制御電圧ノード(112)の間に結合される。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

CR発振回路およびその周波数補正方法

【課題】基準周波数信号を用いることなく、温度変動、電源電圧変動および回路定数のばらつきにかかわらず高精度な発振周波数を得る。

【解決手段】出荷検査時において、発振動作の環境温度と電源電圧を変化させながら発振周波数が目標周波数に一致するのに必要な抵抗5の抵抗値を順次求め、環境温度と電源電圧に対して当該抵抗値を対応付けたデータテーブルをメモリ18に記憶する。CR発振回路の実際の使用状態では、制御回路17は、所定の制御周期ごとに温度検出回路15と電源電圧検出回路16から電圧Va、Vbを入力しA/D変換する。メモリ18に予め記憶されたデータテーブルから電圧Va、Vbに対応した抵抗5の抵抗値を読み出し、抵抗5の抵抗値Rが当該読み出した指定値に等しくなるようにスイッチ7a〜7cを切り替える。

(もっと読む)

周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路

【課題】自励発振回路周辺の状態変化による発振周波数の変化を抑えることができる周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路を提供する。

【解決手段】周波数自動調整機能付自励発振回路は、基準信号を生成する基準信号生成回路101bと、基準信号の周波数を調整する発振周波数調整回路101aとを有する自励発振回路101と、互いに特性の異なる1組の抵抗素子を含み、1組の抵抗素子の抵抗値の変化の違いにより自励発振回路101の周辺状態を検出し、検出された周辺状態を示す信号を出力する特性変動検出回路102_1と、特性変動検出回路102_1の出力信号に基づいて発振周波数調整回路101aによる周波数調整を制御する制御部103とを備える。

(もっと読む)

電圧制御発振器

【課題】良好な位相雑音特性を有し、かつ広帯域な発振周波数範囲を有する電圧制御発振器を提供することを目的とする。

【解決手段】本発明に係る電圧制御発振器1は、電源と、少なくとも3つのポート10a〜10dを備えるインダクタ11と、少なくとも3つのポートから選択される異なるポート対にそれぞれ接続される少なくとも2つの負性抵抗回路12及び14と、を有し、インダクタは、少なくとも2つの負性抵抗回路に接続されるポート対の間でそれぞれインダクタとして動作可能であることを特徴とする。

(もっと読む)

改良された帯域幅を備える電圧制御発振器を有する位相同期ループ回路

【課題】改良された電圧制御発振器を提供する。

【解決手段】電圧制御発振器(16)は複数の直列に接続された合成利得段(42、44、46)を含む。合成利得段はトランスコンダクタンス段(48)及びトランスインピーダンス段(50)を含む。トランスコンダクタンス段は第1電源電圧端子から第2電源電圧端子への第1電流経路(52、56、64)及び第2電流経路(54、58、66)を有する。第1可変抵抗(62)は第1電流経路と第2電流経路との間に接続される。トランスインピーダンス段は、第1電流経路の出力に接続された入力端子と、出力端子とを有する第1インバータ(68、72)及び第2電流経路の出力に接続された入力端子と、出力端子とを有する第2インバータ(70、74)を有する。第2可変抵抗(76)は第1インバータの入力端子と出力端子との間に、第3可変抵抗(78)は第2インバータの入力端子と出力端子との間に接続される。

(もっと読む)

多相信号を生成するための方法、回路及びシステム

【課題】位相誤差を補償しながら設定可能な位相オフセットで多相信号を生成するための方法等を提供する。

【解決手段】一実施形態において、回路は、第1の周波数及び第1の位相を有する第1の周期信号を生成する第1のLC型電圧制御発振器(LCVCO)と、第2の周波数及び第2の位相を有する第2の周期信号を生成する第2のLCVCOとを有し、第2の位相は、90度オフセットで第1の位相に対してオフセットされる。

(もっと読む)

VCO利得補償及び位相ノイズ低減のためのプログラマブルバラクタ

【課題】電圧制御発振器の制御利得を発振周波数に対して比較的一定に維持し、位相ノイズを低減したプログラマブルバラクタ装置を提供する。

【解決手段】プログラマブルバラクタ装置100は、複数のデジタルバラクタビットB0、B1、B2によって制御される複数のバイナリ重み付けバラクタ104,106,108を含み得る。プログラマブルバラクタ装置は、複数のバイナリ重み付けバラクタと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとする制御とを含み得る。プログラマブルバラクタ装置の実効容量を変化させる方法は、複数のバイナリ重み付けバラクタを設けることと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとすることとを含み得る。

(もっと読む)

電圧制御発振器およびそれを用いた情報機器

【課題】周波数変換利得の変動が少ない発振器のためのLC共振回路、それを用いた発振器及び情報機器を提供する。

【解決手段】発振器のLC共振回路が、インダクタL1、第1の微調容量と第1の容量バンクからなる並列回路と、第2の微調容量と第2の容量バンクの直列容量とを含む。発振器の周波数変換利得は、第1の容量バンクの容量値が大きくなるに従い低下する第1の微調容量による発振器の周波数変換利得と、第2の容量バンクの容量値が大きくなるに従い増大する第2の微調容量による周波数変換利得の和となる。

(もっと読む)

発振器及び半導体集積回路装置

【課題】発振器の出力端子間に直接寄生する容量Cparaの大きさが無視できない場合でも温度特性を補償する発振器及び発振器を内蔵する半導体集積回路装置を提供する。

【解決手段】インダクタンス素子Lと、容量素子Cと、増幅器30と、をそれぞれ第1の端子と第2の端子との間に並列に接続し、インダクタンス素子と容量素子とによって生じる共振を増幅器によって増幅し、第1の端子と第2の端子とから出力する発振器であって、第1の端子と第2の端子との間にインダクタンス素子の寄生抵抗RLより抵抗値の大きな第1の抵抗素子Rcが第1の端子と第2の端子との間に容量素子と直列に接続されている。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

高周波発振器

【課題】小型に構成され、高調波と基本波との電力比を増加可能な高周波発振器を得る。

【解決手段】印加された電源電圧に基づいて、発振周波数の基本波で発振動作を行い、発振周波数の2倍波を出力する2倍波取り出し型発振器10と、2倍波取り出し型発振器10の出力端子に接続され、発振周波数の2倍波を通過帯域とする出力回路20とを備え、出力回路20は、2倍波取り出し型発振器10に電源電圧を供給する電源端子21と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する結合線路22と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する伝送線路23と、結合線路22の結合量に応じた出力電力を得る第1負荷抵抗24と、電源端子21に対して並列に接続されたキャパシタ25とを有する。

(もっと読む)

発振器

【課題】少ない電流で必要な負性抵抗が得られることにより、安定に動作することのできる発振器を提供する。

【解決手段】互いに並列に配設された容量素子134,234およびインダクタ133,233を有する共振回路13,23と、共振回路13,23の損失を打ち消す負性抵抗が生じるように配設された複数のトランジスタを有する負性抵抗発生器14,24と、第1バイアス端子15,25と、第2バイアス端子16,26と、を備えた複数の発振部10,20と、各共振回路13,23が互いに等価的に並列に接続されるように、複数の発振部10,20を電気的に結合する結合部30Aと、を備え、複数の発振部10,20は、それぞれの第1バイアス端子25および第2バイアス端子16において互いに直列に接続され、複数の発振部10,20における複数のトランジスタ143,144,243,244は、互いに同じ導電型で構成されている。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

発振回路

【課題】、数百メガヘルツの発振周波数を有する発振信号を出力する場合において、半導体集積回路内に設けられた他の回路の特性劣化を抑制することができる発振回路を提供する。

【解決手段】半導体集積回路の内部に設けられた内部キャパシタと、半導体集積回路の外部に設けられた外部キャパシタ及び外部インダクタとからなる共振回路と、共振回路に入力端及び出力端が接続された増幅回路と、を有し、共振回路は、内部キャパシタ、外部インダクタ、並びに内部キャパシタ及び外部インダクタを接続する配線からなる第1閉回路と、外部キャパシタ、外部インダクタ、並びに外部キャパシタ及び外部インダクタを接続する配線からなり、第1閉回路の配線抵抗よりも小なる配線抵抗を有する第2閉回路と、を有することを特徴とする発振回路。

(もっと読む)

発振回路及び電子機器

【課題】発振周波数が安定するまでに要する時間の短い発振回路及び電子機器を提供する。

【解決手段】周波数補正回路を有する共振回路と、前記共振回路の両端の間に接続された増幅回路とを備えた発振回路が提供される。前記周波数補正回路は、第1のコンデンサと、両端の電位が変動可能に前記第1のコンデンサと直列的に接続された第1のトランジスタと、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】VCOに含まれるスパイラルインダクタとMOSバラクタを接続する配線に付加される寄生インダクタ、および/または寄生容量を低減することができる半導体装置を提供する。

【解決手段】LCタンクVCOは、第1および第2のスパイラルインダクタL1,L2と、第1および第2のMOSバラクタC1,C2とを備える。第1および第2のMOSバラクタC1,C2は、半導体基板に垂直な方向から見たときに、第1のスパイラルインダクタL1と第2のスパイラルインダクタL2の間の領域に配置される。

(もっと読む)

発振回路

【課題】小型かつノイズ抑制に優れる発振回路を提供すること。

【解決手段】本発明にかかる発振回路100は、インバータ1及び2、タンク回路3を有する。タンク回路3は、出力ノードOUTTと出力ノードOUTBとの間に並列に接続される。インバータ1は、ドレインが出力ノードOUTBに接続されたn型MISトランジスタM1及びp型MISトランジスタM3を有する。インバータ2は、ドレインが出力ノードOUTTに接続されたn型MISトランジスタM2及びp型MISトランジスタM4を有する。p型MISトランジスタM3及びM4のゲート端子は、それぞれ出力ノードOUTT及びOUTBと直接的に接続される。n型MISトランジスタM1及びM2のゲート端子は、それぞれ結合容量CG1及びCG2を介して出力ノードOUTT及びOUTBと接続され、抵抗CG1及びCG2を介してバイアス電圧VBIASが印加される。

(もっと読む)

二重正帰還電圧制御発振器

【課題】低供給電圧の性能でのマイクロ波帯域における電圧制御発振器の効率を向上させるための二重正帰還電圧制御発振器を提供する。

【解決手段】2つのコルピッツ回路20、21は第1正帰還ループを提供し、第1負抵抗と等価である。NMOS交差結合ペア回路30は、第2正帰還ループを提供し第2負抵抗と等価である。2つのコルピッツ回路20、21及びNMOS交差結合ペア回路30によって生成される2つの各負抵抗は、LCタンクの寄生抵抗に対して並列に接続されている。この為2つの各負抵抗は、LCタンクの寄生抵抗をオフセットする。2つの各負抵抗が生成されるので、低電圧の稼動時において、及び、直流電流の共有において、高い負抵抗が二重正帰還電圧制御発振器10によって生成される。この為、二重正帰還電圧制御発振器10は、より低い電力下で発振可能である。

(もっと読む)

1 - 20 / 222

[ Back to top ]