Fターム[5J081FF25]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路素子 (660) | スイッチ・セレクタ (145)

Fターム[5J081FF25]に分類される特許

121 - 140 / 145

間欠動作回路及び変調装置

【課題】小回路規模、低消費電力で、立ち上がりと立ち下がりの速い出力波形を得ることができる間欠動作回路を提供すること。

【解決手段】能動回路106と、能動回路106の動作開始と動作停止を制御する第1の制御信号S1を生成する第1の制御信号生成回路101と、能動回路106にリンギング振動を起こさせ、かつ、そのリンギング振動の周波数と振幅値を制御することができる第2の制御信号S2を生成する第2の制御信号生成回路102と、能動回路106からリンギング振動と安定振動が継続して出力されるように、第1及び第2の制御信号S1、S2の能動回路106への入力タイミングを調整するタイミング調整回路103とを設けるようにする。

(もっと読む)

発振器、PLL回路および受信機、送信機

【課題】 回路規模を縮小することができるとともに集積化に適した発振器、PLL回路および受信機、送信機を提供すること。

【解決手段】 可変容量回路230、230Aの静電容量を可変することによって電圧制御型発振器21の発振周波数が変更される。可変容量回路230は、制御信号によって静電容量が連続的に変更可能な複数の可変容量素子60〜64と、可変容量素子のそれぞれに対応しており静電容量が固定の複数のコンデンサ50〜54と、可変容量素子とこれに対応するコンデンサとからなる組合せ回路を一組として複数の可変容量素子60〜64と複数のコンデンサ50〜54のそれぞれの選択的な接続の有無を組合せ回路を単位として切り替える複数のスイッチ71〜74、81〜84とを備えている。

(もっと読む)

半導体集積回路

【課題】 トリミングを行わずに電圧制御発振回路の発振周波数を調整すること。制御回路の面積を抑え、調整誤差の少ない発振回路を内蔵した半導体集積回路を提供すること。

【解決手段】 電圧制御発振回路(VCO)の周波数を調整する可変容量素子を、プロセスや素子のばらつき調整用可変容量素子群と、周波数選択用可変容量素子群との2系統に分離して調整を行い、可変容量素子の切り替えスイッチの数と回路面積の増大を小さくする。調整誤差については、調整期待値との差分を記憶素子で記憶し、その差分値が最小となる容量素子値を求めることにより影響を最小限に押さえることが可能となる。

(もっと読む)

集積回路

【課題】従来の発振器用集積回路では、低振幅の出力波形を要求された場合に、出力増幅回路トランジスタ対のゲート・ソース間電圧が十分に確保できず、大きな負荷を駆動できないという問題があった。

【解決手段】 出力増幅回路112のPチャネルトランジスタ110およびNチャネルトランジスタ111のゲートを、コンデンサ106および107により発振回路104の出力に交流的に結合するとともに、抵抗108および109を介してPチャネルトランジスタ110のゲートはGND電位に、Nチャネルトランジスタ111のゲートは電源電位にバイアスされていることにより、これらのトランジスタのゲート・ソース間電圧が充分に確保され、大きな負荷を駆動できるようにしたことを特徴とする集積回路。

(もっと読む)

電圧制御発振器

【課題】 本発明の課題は、電圧制御発振器の位相雑音を抑制することである。

【解決手段】複数のMOSトランジスタTR12、TR13・・・のドレインは、複数のスイッチSW1、SW2・・・を介してMOSトランジスタTR11のドレインと接続されている。発振周波数を設定するための周波数設定用デジタルデータから得られるgm設定用デジタルデータによりスイッチSW1,SW2・・・をオンまたはオフにすることでMOSトランジスタTR11に並列に選択的に複数のMOSトランジスタTR12,TR13・・・を接続する。これにより、共振回路10に供給する電流を変化させる。

(もっと読む)

2バンド発振器

【課題】 2つの発振信号を切り替えて共通の端子から出力する場合に、発振信号の減衰を少なくする。

【解決手段】 第1の周波数帯の発振信号を出力する第1の発振トランジスタ11と、第1の発振トランジスタ11のコレクタに電源を供給する第1のインダクタ12と、第1の発振トランジスタ11の動作を切り替える第1のスイッチ素子16と、第2の周波数帯の発振信号を出力する第2の発振トランジスタ21と、第2の発振トランジスタ21のコレクタに電源を供給する第2のインダクタ22と、第2の発振トランジスタ21の動作を切り替える第2のスイッチ素子26と、第1の周波数帯の発振信号又は第2の周波数帯の発振信号を外部に出力する出力端子30とを備え、第1のインダクタ12と出力端子30との間に第1のスイッチ素子16を介挿し、第2のインダクタ22と出力端子と30の間に第2のスイッチ素子22を介挿した

(もっと読む)

周波数変換器

【課題】 発振周波数を下げたときに発振停止を起こしにくくし、さらに、温度が上昇したときにも発振停止を起こしにくくする。

【解決手段】 ミキサトランジスタ86〜89のコレクタバイアス電流と発振トランジスタ61、62のコレクタバイアス電流とを設定するためのバイアス電源74を設け、制御電圧Vtが第1の所定値以上のときよりも第1の所定値以下のときにバイアス電源74の出力電圧を高くしてミキサトランジスタ86〜89のコレクタバイアス電流又は発振トランジスタ61、62のコレクタバイアス電流の少なくとも一方を大きくした。

(もっと読む)

発振器およびこれを用いたPLL回路

【課題】 インダクタを制御信号により連続的に変化可能とすることにより、発振器およびPLL回路の機能および性能を向上させる。

【解決手段】 インダクタンスが変化する可変インダクタ部と、可変インダクタ部に接続された可変容量素子と、可変インダクタ部のインダクタンスと可変容量素子の容量とで決まる発振周波数により発振する出力部と、発振周波数を変調する周波数制御信号を生成する制御信号生成手段とを含む。可変インダクタ部は、第1インダクタと、第1インダクタに流れる電流を表す電気信号を検出し、電気信号に基づいて電流信号を生成する電流信号生成手段と、電流信号を受ける第2インダクタとを含み、第1インダクタと第2インダクタを所定の磁気的結合位置に配置し、第1インダクタのインダクタンスを所望の値にする。

(もっと読む)

誘電体共振器装荷型発振回路及びこれを用いたレーダー装置

【課題】 誘電体共振器装荷型発振回路の立ち上がり時間及び/又は立ち下がりを短縮する。

【解決手段】 誘電体共振器11と、誘電体共振器11に共振電圧を与える駆動回路20と、共振電圧を生成するために必要な電圧Vdsを駆動回路20に与えるスイッチ71と、共振電圧の生成を停止させるグランド電圧を駆動回路20に与えるスイッチ72と、スイッチ71から見て電圧Vdsを供給する電源端子側に接続され、駆動回路20が発生するノイズを除去するコンデンサ42とを備える。そして、これらスイッチ71,72を排他的に導通させれば、スイッチ72をオンさせることにより直ちに発振を停止させることができ、また、スイッチ71のオン・オフにかかわらず、コンデンサ32は常に電荷が蓄積された状態となることから、スイッチ71がオンすると直ちに発振動作を行うことが可能となる。

(もっと読む)

発振回路

【課題】 発振周波数帯の切替に連動して各周波数帯に最適なバイアス電圧を発振トランジスタに印加する。

【解決手段】 発振トランジスタ1と、互いに異なる発振周波数帯にそれぞれ対応して設けられた共振回路9、11と、1つの共振回路を選択して発振トランジスタ1のベースとコレクタとの間に結合する切替手段12とを備え、選択された共振回路に対応したバイアス電圧を切換手段12によって発振トランジスタ1のベースに印加した。

(もっと読む)

電圧制御発振器及びこれを備えた集積回路装置

【課題】本発明は、ある周波数を発振するに際して、いずれの電圧制御発振回路を選択すべきかを一意的に決定することが可能な電圧制御発振器を提供することを目的とする。

【解決手段】本発明に係る電圧制御発振器は、複数の電圧制御発振回路(図6ではVCO1〜VCO3)と、そのうちの1つを選択して動作させる選択回路と、を有して成り、隣接する電圧制御発振回路の発振周波数可変域がその端部で互いに重複されて成る電圧制御発振器において、最も低域側にばらついた状態(low状態)におけるn(≧1)番目の電圧制御発振回路の上端周波数が、最も高域側にばらついた状態(high状態)におけるm(=n+1)番目の電圧制御発振回路の下端周波数よりも高くなるように、各電圧制御発振回路の発振周波数可変域を調整して成る構成とされている。

(もっと読む)

発振装置

【課題】 従来の電圧制御型発振器に比べ、電圧による発振周波数の制御性が良い発振装置を提供する。

【解決手段】 発振装置10は、電圧制御型発振器1と、制御電圧供給回路2とを備える。電圧制御型発振器1は、入力電圧Vinのビット数に対応して3個の可変容量ダイオード141〜143を含み、可変容量ダイオード141〜143は、ノードN4,N5間に並列に接続される。制御電圧供給回路2は、3ビット[A3A2A1]からなる入力電圧Vinに基づいて、3個の可変容量ダイオード141〜143の3個の容量の和が入力電圧Vinに比例するように制御電圧VCTL1,VCTL2,VCTL3を決定し、その決定した制御電圧をそれぞれ可変容量ダイオード141〜143へ供給する。

(もっと読む)

発振回路及びフェーズロックトループ回路

【課題】電源電位が変動する場合であってもレギュレータが不要な発振回路およびフェーズロックトループ回路を実現する。

【解決手段】抵抗Raの一端に電源電位VDDを与え、抵抗Raの他端に定電流源75aを接続する。インダクタL1a,L2aの一端にも電源電位VDDを与え、キャパシタ群1a,2aの一端に、抵抗Raの他端における電位Vmaを与える。インダクタL1a,L2aの他端とキャパシタ群1a,2aの他端とを接続する。抵抗Raには定電流が流れるので、電位Vmaは電源電位VDDに対して一定の電位差を有し、インダクタL1a,L2aの一端およびキャパシタ群1a,2aの一端の間に常に一定の電圧が加わる。よって、たとえ電源電位VDDが変動しても、常に一定の電圧をインダクタおよびキャパシタの直列接続体に印加することができ、レギュレータが不要な発振回路を実現できる。

(もっと読む)

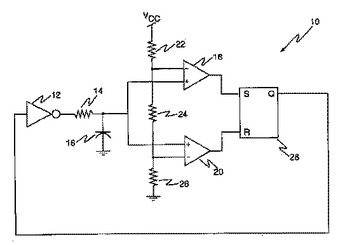

電圧補償及び温度補償されたRC発振回路

入力及び出力を有するインバータを具備する、温度補償された集積RC発振回路。RC網は、前記インバータと、比較器の対との間に接続されている。第1比較器は、第1基準電圧に接続された反転入力と、前記RC網に接続された非反転入力と、出力とを具備する。第2比較気は、前記RC網に接続された反転入力と、第2談笑電圧に接続された非反転入力と、出力とを具備する。セット・リセット・フリップフロップは、前記第1比較器の出力に接続されているセット入力と、前記第2比較器の出力に接続されているリセット入力と、前記インバータの入力に接続されている出力とを具備する。前記比較器の差動増幅器は、各々ミラー接続されたpチャネルMOSトランジスタを制御する、ダイオード接続されたpチャネルMOSトランジスタを具備し、前記pチャネルMOSトランジスタのチャネル幅は、前記ダイオード接続されたpチャネルカレントミラートランジスタの幅より狭い。  (もっと読む)

(もっと読む)

電圧制御発振器及びそれを用いたPLL回路並びに周波数変調器

【課題】 安定なPLLを構成できる電圧制御発振器を得る。

【解決手段】 複数の周波数帯域を出力周波数帯域とすることができる電圧制御発振器1において、その電圧制御発振部3の前段に電圧変換部2を設け、制御部4が、電圧制御発振器1の周波数制御電圧S1−出力周波数S2変換特性を線形とすると共に電圧制御発振器1の出力周波数帯域それぞれにおける上記変換特性の傾きを略同一とすべく、出力周波数帯指定信号S3により指定される周波数帯域に応じて電圧変換部2の電圧変換特性を制御する。

(もっと読む)

CR発振回路および電子装置

【課題】 発振周波数の調整手段の選択余地を広げるのが望ましい。

【解決手段】 CR発振回路100において、第1発振用コンデンサC1および第2発振用コンデンサC2を並列に設け、CR発振回路100全体の容量値を選択可能に構成し、可変抵抗である、例えば第5トリミング抵抗116eを少なくとも一つ含む複数の抵抗を直列に設け、第5トリミング抵抗116eの抵抗値を調整することによってCR発振回路100全体の抵抗値を選択可能に構成し、CR発振回路100全体の容量値として選択可能な最小値CMINと最大値CMAX、およびCR発振回路100全体の抵抗値として選択可能な最小値RMINと最大値RMAXの間に、

CMIN・RMAX≧CMAX・RMIN

なる関係をもたせる。

(もっと読む)

電圧制御発振器の周波数制御用可変インダクタンス回路

電子デバイス(20)は、インダクタ(42)を含むデバイス回路(32)を有する第1の基板(22)と、多数の他のインダクタ(62)を含むインダクタンス調整回路(60)を有する第2の基板(24)とから作成される。基板(22、24)は、互いに対向するように組み合わせる。他のインダクタ(62)は、インダクタ(42)に対して種々の相互インダクタンスの関係を選択するように構成する。これらの関係は、デバイスの動作期間中に選択することができ、デバイス回路(32)に可変インダクタンスを提供する。 (もっと読む)

周波数同調可能な装置

周波数同調可能な装置は、キャパシタンス範囲の全体にわたって同調可能な容量性部分(C1、C2、Cv1、Cv2)を有する共振回路(RS)を備える。発振ループを形成するために、共振回路には複数の増幅器(AB、AS1、AS2、AS3)が結合される。それらの増幅器の少なくとも1つが、活性状態とアイドル状態との間で切り替えが可能な切替可能増幅器(AS1)である。切替可能増幅器は、活性状態とアイドル状態との間で切り替えられたときに、共振回路の容量性部分と並列にキャパシタンス変化を引き起こす。切替可能増幅器は、このキャパシタンス変化が、容量性部分が同調可能なキャパシタンス範囲とほぼ一致するように構成される。  (もっと読む)

(もっと読む)

電圧制御発振器及び通信用半導体集積回路

【課題】 周波数可変範囲が広く、良好な位相雑音特性を持ち、低コストで集積化した周波数シンセサイザを提供する。

【解決手段】 共振タンク回路(A)および前記共振タンク回路(A)の共振周期数で発振、増幅する増幅回路(B)からなるVCOにおいて、前記共振回路(A)に、発振周波数バンドを可変させる容量バンド切り替え回路(D)を備えると共に、各発振周波数バンドに対応して適した電流を前記増幅回路(B)供給するために、電流バンド切り替え回路(E)を備えることにより、発振周波数の可変範囲拡大と、各周波数バンドでの電流最適化により広帯域で良好な位相雑音特性を可能する。

(もっと読む)

電圧制御発振器

【課題】発振周波数の安定化を図りつつ、位相ノイズの増加を抑えることができる電圧制御発振器を提供する。

【解決手段】電圧制御発振器は、インダクタセクション20、バラクタセクション22、ネガティブGmセクション21、トリミングキャパシタアレイ23及びバイアス回路R10〜R15,R20〜R25を備えている。バイアス回路は、上記トランジスタ26−0〜26−5,27−0〜27−5とキャパシタC10〜C15,C20〜C25との接続点N4にバイアス電圧Vbiasを与える。キャパシタを切り離すトランジスタのドレインをバイアスすることによって寄生ダイオードをオンしないようにでき、それによって位相ノイズの増加を抑制することができる。

(もっと読む)

121 - 140 / 145

[ Back to top ]