Fターム[5J081FF25]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路素子 (660) | スイッチ・セレクタ (145)

Fターム[5J081FF25]に分類される特許

1 - 20 / 145

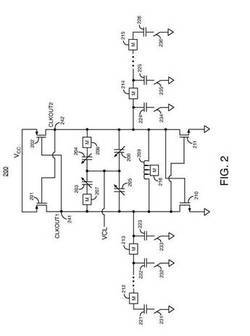

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

発振回路、発振器、電子機器及び発振回路の起動方法

【課題】起動時の異常発振を抑えるとともに負荷の大きさによらず電源電圧の低電圧化が可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(水晶振動子10)と、共振子の一端から他端への帰還経路を有する増幅回路20と、電圧供給回路30と、を含む。電圧供給回路30は、電源電圧Vccが入力される時定数回路(抵抗32とコンデンサー34によるRC積分回路)を有し、電源電圧Vccが入力されてから時定数回路の時定数に応じて立ち上がるとともに増幅回路20の負荷によらず一定電圧となる駆動電圧VAを発生させ、駆動電圧VAを増幅回路20に供給する。

(もっと読む)

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

発振回路、発振器、電子機器及び発振回路の起動方法

【課題】インダクタンス素子に起因して発生する起動時の異常発振を効率的に抑えることが可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(SAW共振子10)と、増幅回路20と、スイッチング素子(NMOSスイッチ30)と、を含む。増幅回路20は、共振子の一端から他端への帰還経路、当該帰還経路に設けられている第1のインダクタンス素子(伸長コイル200)、当該帰還経路に設けられ、第1のインダクタンス素子と直列に設けられている可変容量素子(可変容量ダイオード202)、を有している。スイッチング素子は、第1のインダクタンス素子と可変容量素子とを含む回路部に対して並列に設けられている。

(もっと読む)

発振器、半導体部品及び電子機器

【課題】複数の端子のうち一部の端子が使用されない場合においても好適に動作可能な発振器を提供する。

【解決手段】発振器1は、振動素子14と、振動素子14に電圧を印加して発振信号Outを生成する発振回路27と、発振回路27の出力部27aに接続されることにより発振信号Outを出力可能な端子5(Out1)及び端子5(Out2)と、出力部27aと外部機器(回路基板53を含む)との端子5(Out2)を介した導通状態の変化に応じた発振回路27の周波数の変化を補償する接続補償回路37とを有する。

(もっと読む)

CR発振回路およびその周波数補正方法

【課題】基準周波数信号を用いることなく、温度変動、電源電圧変動および回路定数のばらつきにかかわらず高精度な発振周波数を得る。

【解決手段】出荷検査時において、発振動作の環境温度と電源電圧を変化させながら発振周波数が目標周波数に一致するのに必要な抵抗5の抵抗値を順次求め、環境温度と電源電圧に対して当該抵抗値を対応付けたデータテーブルをメモリ18に記憶する。CR発振回路の実際の使用状態では、制御回路17は、所定の制御周期ごとに温度検出回路15と電源電圧検出回路16から電圧Va、Vbを入力しA/D変換する。メモリ18に予め記憶されたデータテーブルから電圧Va、Vbに対応した抵抗5の抵抗値を読み出し、抵抗5の抵抗値Rが当該読み出した指定値に等しくなるようにスイッチ7a〜7cを切り替える。

(もっと読む)

周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路

【課題】自励発振回路周辺の状態変化による発振周波数の変化を抑えることができる周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路を提供する。

【解決手段】周波数自動調整機能付自励発振回路は、基準信号を生成する基準信号生成回路101bと、基準信号の周波数を調整する発振周波数調整回路101aとを有する自励発振回路101と、互いに特性の異なる1組の抵抗素子を含み、1組の抵抗素子の抵抗値の変化の違いにより自励発振回路101の周辺状態を検出し、検出された周辺状態を示す信号を出力する特性変動検出回路102_1と、特性変動検出回路102_1の出力信号に基づいて発振周波数調整回路101aによる周波数調整を制御する制御部103とを備える。

(もっと読む)

電圧制御発振器

【課題】良好な位相雑音特性を有し、かつ広帯域な発振周波数範囲を有する電圧制御発振器を提供することを目的とする。

【解決手段】本発明に係る電圧制御発振器1は、電源と、少なくとも3つのポート10a〜10dを備えるインダクタ11と、少なくとも3つのポートから選択される異なるポート対にそれぞれ接続される少なくとも2つの負性抵抗回路12及び14と、を有し、インダクタは、少なくとも2つの負性抵抗回路に接続されるポート対の間でそれぞれインダクタとして動作可能であることを特徴とする。

(もっと読む)

回路装置及び電子機器

【課題】無駄な電力消費やノイズの悪影響等を抑制できる回路装置及び電子機器等の提供。

【解決手段】回路装置は発振回路10とバッファー回路20を含む。バッファー回路20は、プリバッファーPBFと第1、第2の出力バッファーQBF1、QBF2を含む。第1のモードでは、第1の出力バッファーQBF1が動作イネーブル状態に設定され、第2の出力バッファーQBF2が動作ディスエーブル状態に設定される。第2のモードでは、第1の出力バッファーQBF1及び第2の出力バッファーQBF2が動作イネーブル状態に設定される。第1のモードでは、プリバッファーPBFの駆動能力が、第2のモードに比べて低い駆動能力に設定される。

(もっと読む)

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

VCO利得補償及び位相ノイズ低減のためのプログラマブルバラクタ

【課題】電圧制御発振器の制御利得を発振周波数に対して比較的一定に維持し、位相ノイズを低減したプログラマブルバラクタ装置を提供する。

【解決手段】プログラマブルバラクタ装置100は、複数のデジタルバラクタビットB0、B1、B2によって制御される複数のバイナリ重み付けバラクタ104,106,108を含み得る。プログラマブルバラクタ装置は、複数のバイナリ重み付けバラクタと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとする制御とを含み得る。プログラマブルバラクタ装置の実効容量を変化させる方法は、複数のバイナリ重み付けバラクタを設けることと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとすることとを含み得る。

(もっと読む)

圧電発振器

【課題】安定駆動に達するまでの時間を短縮した圧電発振器を提供する。

【解決手段】本発明の水晶発振器(圧電発振器)50は、水晶振動子(圧電振動子)1と、水晶振動子1に接続されて発振ループを形成して発振信号を出力する水晶発振部(圧電発振部)24、及び水晶発振部24の起動時に自励発振する自励発振部25により構成された発振回路と、を備え、自励発振部25の周波数が水晶発振部24の周波数よりも高く設定されている。尚、自励発振部25は、複数のコンデンサー(容量素子)C、インバーター5及び抵抗素子4により構成され、複数のコンデンサーCの合成容量の値を調整するために、調整手段6を備えている。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

車両制御システムおよび車載器

【課題】携帯機と車載器との間で無線通信を行うに際し、車載器に使用される振動子の発振周波数の温度ばらつきを軽減する。

【解決手段】受信IC22には車載器20の温度を測定する第2温度センサ27が内蔵されている。そして、補正部23は、携帯機10の第1振動子11および車載器20の第2振動子21の周波数温度特性のデータマップがそれぞれ記憶されており、受信IC22から携帯機10の温度を示す送信側温度情報を入力すると共に第2温度センサ27から車載器20の温度を示す受信側温度情報を入力し、送信側温度情報、受信側温度情報、およびデータマップに基づいて取得したオフセット値を第2振動子21に付加することで、第2振動子21の第2周波数を第1振動子11の第1周波数に近づける補正を行う。

(もっと読む)

可変容量素子

【課題】従来の可変容量素子は、容量値の精度が低い問題があった。

【解決手段】本発明の可変容量素子は、第1の電源端子と出力端子CTOPとの間に接続される第1の容量素子C1と、容量切替信号CSELに応じて導通状態が切り替えられる容量選択スイッチN1と、第1の容量素子C1と並列に接続され、かつ、容量選択スイッチN1と直列に接続される第2の容量素子C2と、容量選択スイッチN1が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITBに応じて、第2の容量素子C2と容量選択スイッチN1とを接続する容量切替ノードNDaの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する誤差補正回路10と、を有する。

(もっと読む)

発振回路及び電子機器

【課題】発振周波数が安定するまでに要する時間の短い発振回路及び電子機器を提供する。

【解決手段】周波数補正回路を有する共振回路と、前記共振回路の両端の間に接続された増幅回路とを備えた発振回路が提供される。前記周波数補正回路は、第1のコンデンサと、両端の電位が変動可能に前記第1のコンデンサと直列的に接続された第1のトランジスタと、を有することを特徴とする。

(もっと読む)

1 - 20 / 145

[ Back to top ]