Fターム[5J081FF25]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路素子 (660) | スイッチ・セレクタ (145)

Fターム[5J081FF25]に分類される特許

41 - 60 / 145

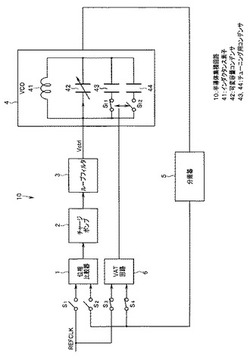

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

発振制御回路

【課題】発振開始時からデューティが50%に安定する発振制御回路を提供する。

【解決手段】作動制御回路3が、発振信号の発振電位がCMOSインバータIV1の反転電位よりも低い第1基準電位よりも低くなるまでMOSトランジスタT11及びT12をオフ状態、MOSトランジスタT2をオン状態に保持する。作動制御回路3が、発振信号の発振電位が第1基準電位よりも低くなったとき出力が反転するCMOSインバータIV31と、CMOSインバータ31の後段に設けた抵抗R31とコンデンサC31とからなるローパスフィルタ31と、ローパスフィルタ31の出力が閾値を越えると出力が反転するCMOSインバータ33と、を有している。

(もっと読む)

電圧制御発振器、並びにそれを用いたPLL回路、FLL回路、及び無線通信機器

【課題】発振周波数が温度によって変化する場合に、発振周波数の可変範囲を狭くすることなく発振周波数を所望の値に保持することができる電圧制御発振器、並びにそれを用いたPLL回路、FLL回路、及び無線通信機器の提供。

【解決手段】可変容量回路120を構成する可変容量素子121,122の接続点Yには、制御電圧Vtが印加される。容量スイッチ回路130を構成するスイッチング素子132には、制御信号Fselが印加される。インダクタ回路110を構成するインダクタ111,112の接続点Xには、制御部170によって電源電圧Vddが印加される。この電源電圧Vddの電圧値は、局部発振信号の発振周波数が温度変化に対して一定となるように制御される。

(もっと読む)

可変インダクタ及び電圧制御発振器

【課題】LCの並列共振による電圧制御発振器を構成するための可変インダクタであって、小型かつQ値の劣化を抑制した、複数周波数発振可能な可変インダクタを提供すること。

【解決手段】可変インダクタ100は、線対称軸Y−Y’を有し、可変インダクタ100が備える複数の円弧が共有する中心点Zが1つ存在する。可変インダクタ100は、点Zを中心点とした第1の円周上の円弧で構成された、Y−Y’に関して線対称な第1のインダクタ部Ind1と、点Zを中心点とした第2の円周上の円弧で構成された、Y−Y’に関して線対称な第2のインダクタ部Ind2とを備える。Ind1は、端子D’から端子D’とY−Y’に関して線対称な端子D’’まで延在する。Ind2は、端子E’から第端子E’とY−Y’に関して線対称な端子E’’まで延在する。第1の円周の半径r1は、第2の円周の半径r2よりも短い。

(もっと読む)

可変インダクタ及び電圧制御発振器

【課題】LCの並列共振による電圧制御発振器を構成するための可変インダクタであって、小型かつQ値の劣化を抑制した、複数周波数発振可能な可変インダクタを提供すること。

【解決手段】可変インダクタ100は、線対称軸Y−Y’を有し、Y−Y’上の点Bを通るY−Y’に関して線対称なインダクタ部Ind1及びInd2を備える。インダクタ部Ind2は、点B以外でインダクタ部Ind1と交わらず、インダクタ部Ind1及びInd2は共に曲線のみで構成される。インダクタ部Ind1の線路長はInd2の線路長よりも短い。Ind1は、Y−Y’上の点Z1を中心点とした円周上の円弧で構成され、端子D’から点Bを通って端子D’とY−Y’に関して線対称な端子D’’まで延在する。Ind2は、Y−Y’上の点Z2を中心点とした円周上の円弧で構成され端子E’から点Bを通って端子E’とY−Y’に関して線対称な端子E’’まで延在する。

(もっと読む)

発振器および位相同期ループ

【課題】発振器の位相雑音を低減し、位相同期ループの消費電力および位相雑音を低減する。

【解決手段】発振器は、共振回路の容量値に応じて発振周波数が可変する構成であって、外部から入力する外部クロックと設定データに応じて、オーバーフロー信号を間欠的に出力するアキュムレータ11と、オーバーフロー信号の間欠入力に応じてオン・オフするスイッチ12と、スイッチ12を介して共振回路に接続される固定容量値を有する容量素子C2とを備え、設定データに応じて間欠的に出力されるオーバーフロー信号の入力によりスイッチ12がオンとなるオン時間における発振周波数と、オーバーフロー信号が入力されないときにスイッチ12がオフとなるオフ時間における発振周波数との間で、オン時間とオフ時間の時間割合に応じた平均発振周波数を可変させる。

(もっと読む)

オーム調節可能な発振周波数を有する発振器

調節可能な発振周波数を有する発振器は、端子で負性入力抵抗を示している能動素子、負性入力抵抗を示しているその能動素子の端子と連結した発振回路、および、その発振器の発振周波数が調節可能である調節可能なオーム抵抗を有する素子を含む。 (もっと読む)

発振回路、集積回路装置及び電子機器

【課題】複数の周波数のうちから所望の周波数を選択してクロック信号を生成できる発振回路、集積回路装置及び電子機器を提供すること。

【解決手段】発振回路は、キャパシター10の一端、第1の抵抗素子20の一端及び第2の抵抗素子30の一端がその入力に接続される第1の反転回路と、キャパシター10の他端がその出力に接続される第n(nは2以上の偶数)の反転回路とを有する第1〜第nの反転回路INV1〜INVnと、第nの反転回路INVnの出力が入力され、第1の抵抗素子20の他端を駆動する第1の駆動用反転回路DR1と、第nの反転回路INVnの出力が入力され、第2の抵抗素子30の他端を駆動する第2の駆動用反転回路DR2とを含む。

(もっと読む)

電圧制御発振回路

【課題】製造コストの追加なく一般的に用いられる可変容量素子を利用し、位相雑音特性に優れたRTW形式の電圧制御発振回路を実現できるようにする。

【解決手段】電圧制御発振回路は、ループ状の伝送線路15と、信号線路と接続されたアクティブ回路17と、信号線路と接続され複数の可変容量ユニット23を有する可変容量部21とを備えている。各可変容量ユニット23は、可変容量素子31と、可変容量素子31に制御電位を印加する制御端子41と、可変容量素子31に基準電位を印加する基準電位端子43とを有している。少なくとも2つの可変容量ユニット23は、基準電位が互いに異なっている。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

高周波発振器

【課題】周囲の環境温度による光ファイバの熱伸縮に対してもPLL制御を正常に行うことができる高周波発振器を得る。

【解決手段】レーザ光源が発生したレーザ光を光変調器により変調し、光ファイバを介して伝送した変調後のレーザ光を光電変換器により高周波信号に変換し、変換後の高周波信号からバンドパスフィルタにより所定の通過帯域成分を取り出し、当該所定の通過帯域成分の高周波信号の周波数を変調信号として前記光変調器に帰還すると共に発振信号として出力する高周波発振器において、高周波信号の周波数が一定になるように制御するPLL制御手段と、当該高周波発振器の発振周波数の変動をPLL制御手段の予め設定した周波数引き込み範囲内に納めるように高周波信号の位相を調整する位相調整手段を備えた。

(もっと読む)

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

発振回路は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ、コンデンサ、およびオプションコンダクタも含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。  (もっと読む)

(もっと読む)

信号処理装置及び信号処理方法

【課題】最大の周波数マージンで、発生させる発振周波数をロック状態にする。

【解決手段】ループフィルタ23は、発振周波数における所定の特性に基づいて、入力される制御電圧に対応して発振周波数を発生させるVCO63であって、所定の特性が粗調整されるVCO63に、制御電圧を入力し、VCO粗調整回路135は、制御電圧が所定の設定範囲を超えた場合に、VCOによる所定の特性を、複数の特性のうちのいずれかに粗調整し、DAC133は、制御電圧が所定の設定範囲内で変化する場合に、発振周波数がロック状態とならないとき、所定の設定範囲を広げる方向に更新する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

半導体集積回路装置

【課題】差動構成のゲートとドレインとのクロスカップリングのための配線の寄生抵抗を低減する。

【解決手段】第1のアクティブ領域から突出した第1の突出部を夫々有する複数の第1のゲートと、第1のアクティブ領域に隣接した第2のアクティブ領域から、第1の突出部の突出方向とは反対の方向に突出した第2の突出部を夫々有する複数の第2のゲートと、複数の第1のゲートの第1の突出部上及び第2のアクティブ領域の全てのドレイン上に形成されて複数の第1のゲートと第2のアクティブ領域の全てのドレインとを接続する第2の共通配線と、複数の第2のゲートの第2の突出部上及び第1のアクティブ領域の全てのドレイン上に形成されて複数の第2のゲートと第1のアクティブ領域の全てのドレインとを接続する第3の共通配線とを具備したことを特徴とする。

(もっと読む)

PLL周波数シンセサイザ回路及びその制御方法

【課題】信号に対するノイズの増加がなく安定したPLL周波数シンセサイザ回路及びその制御方法を提供する。

【解決手段】電圧制御発振器の制御電圧をモニタし、制御電圧に応じて前記電圧制御発振器の変調感度との間で安定に動作するように設定されたループフィルタを切り替えるようにした。

(もっと読む)

無線装置

【課題】

簡単な回路構成で2つの周波数帯域を出力可能とし、無線装置の小型化及びコストの低減を図る。

【解決手段】

発振回路部26から発せられる基本周波数を逓倍回路部27を介して出力する様にし、該逓倍回路部に給電する電圧を2つの異なる電圧に切換え可能とし、1つの電圧では前記逓倍回路部が増幅作動する様にし、他の電圧では該逓倍回路部が逓倍作動する様構成し、2つの周波数帯を択一的に発信可能とした。

(もっと読む)

発振器

【課題】内蔵するICチップの内容を外部から設定し、書き換えることで回路定数や回路方式あるいは分周数を実装機器の仕様に合せて切り換え可能とした融通性の高い発振器を提供する。

【解決手段】内蔵するICチップ3に発振回路と共に複数の回路定数や回路方式の回路、あるいは複数の分周数の分周回路を備えると共に、該ICチップに不揮発メモリの領域、あるいは分周回路領域を設け、発振器の回路定数や回路方式を当該不揮発メモリに外部から書き込んだデータで切り換える構成とした。

(もっと読む)

電圧制御発振器

【課題】VCO利得の変動を抑圧した簡易な構成のVCOの提供。

【解決手段】二つの周波数可変手段を具備することでマルチバンド動作を行なう電圧制御発振器(VCO)において、可変容量素子11iaと12ia及び11ibと12ib(i=1、2、3)をそれぞれ互いに極性が逆になる向きに並列接続可能とし、可変容量素子対を形成する。一般に、可変容量素子11iaと12ia、11ibと12ib(i=1、2、3)の容量値は異なる値に設定される。これらの可変容量素子対は、ループコントロール端子3に印加されるコントロール電圧VCNTにより制御されると同時に、帯域設定信号VSW1、VSW2、VSW3によってオンオフされるスイッチ素子であるトランジスタ101a、102a、103a、101b、102b、103bの切替により、VCO本体に電気的に分離・接続される。

(もっと読む)

発振回路装置

【課題】 この発明は、負性抵抗を示す帯域が広くして、使用できる発振周波数を多くすることを目的とするものである。

【解決手段】 この発明の発振回路装置は、相互接続された一対のトランジスタ1、2と抵抗・容量の回路網で構成された発振部100と、発振部100に接続されるループ状の伝送線路で構成された共振部200と、を備え、前記抵抗・容量の回路網の抵抗値及び容量値を前記発振部が第1の周波数帯で負性抵抗となり、その第1の周波数帯より高い周波数帯においてフラットな負性抵抗を示すように設定したことを特徴とする。

(もっと読む)

41 - 60 / 145

[ Back to top ]