Fターム[5J081KK07]の内容

LC分布定数、CR発振器 (9,854) | 制御手段及び要因 (1,418) | 一次要因 (534) | 容量 (335)

Fターム[5J081KK07]の下位に属するFターム

素子内容量 (235)

Fターム[5J081KK07]に分類される特許

81 - 100 / 100

可変集積インダクタ

【課題】2個以上の値の間で切替え可能なインダクタンス値を有する可変集積インダクタについて記載する。

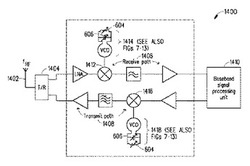

【解決手段】好適な実施形態において、可変集積インダクタは、一対の2次インダクタに電磁結合されたマルチループ1次インダクタを含んでいる。2次インダクタは互いに接続されて閉回路を形成しており、その内部で2次インダクタは、マルチループ1次インダクタにより出力されるインダクタンス値を変化させるように直列接続と並列接続との間で切替え可能な可変トポロジを有している。一応用例において、可変集積インダクタは、マルチバンドRF無線トランシーバ(例えば、無線通信装置)で使用可能な種類である電圧制御発振器(VCO)内で用いられる。他の応用例において、可変集積インダクタは、同調増幅器負荷、インピーダンス整合ネットワーク、デジタル制御発振器、または他の任意の種類の周波数選択LCネットワークに利用可能である。

(もっと読む)

電圧制御発振器

【課題】 位相雑音を低く保ちながら低消費電力化を実現できるLC共振型電圧制御発振器を提供する。

【解決手段】 クロスカップリングされる少なくとも1対のペアトランジスタを用いて構成される交流信号増幅回路とLC回路とを有し、LC回路の素子値を制御電圧に応じて変更することで所望周波数の発振信号を生成する電圧制御発振器において、交流信号増幅回路は、各ペアトランジスタのドレインにソースが接続され、対応するペアトランジスタとでカスコード増幅回路を形成する付加トランジスタを備えて構成される。

(もっと読む)

通信装置およびこれを具備した車両

【課題】

複数系統を有する通信装置において、幅広い温度環境においても通信を継続するとともに、装置の小型化を図る。

【解決手段】

並列接続された複数の静電容量を適宜接続・開放することにより発振周波数を切り換え可能なIC化局部発振器を具備し、温度変化に応じて一つの信号経路における静電容量値の設定を変更し、その後任意の時間経過をもって他の信号経路の発振器における静電容量値の設定を変更する。

(もっと読む)

電圧制御発振器およびRF−IC

【課題】 広い周波数範囲を取ることができ、また発振安定性を改善することができるW−CDMA用の電圧制御発振器、RF−ICを提供する。

【解決手段】 電圧制御発振器(RF−IC)において、共振回路の共振用A,Bインダクタ14,15との間で磁気的相互作用を発生する切替用A,Bインダクタ12,13と、共振用A,Bインダクタ14,15と切替用A,Bインダクタ12,13との間の磁気的相互作用によりインダクタンス値を切り替えるスイッチ機能、切替用A,Bインダクタ12,13の負荷となる負荷機能を兼ね備えたスイッチ・負荷手段としての、A,B,C,D_NMOS6,7,8,9とを備え、制御信号によりA,B,C,D_NMOS6,7,8,9のオン・オフをさせて相互誘導を制御し、共振回路のインダクタンス値を切り替えて発振周波数を切り替える。また、インダクタンス値を上げて発振安定性を上げる。

(もっと読む)

キャパシタアレイ回路及び電圧制御発振器

【課題】 ほぼ均一な周波数ステップを実現し、可変周波数範囲を拡大することが可能なキャパシタアレイ回路及びそれを用いた電圧制御発振器を提供する。

【解決手段】 端子VCOout1、VCOout2の間に、キャパシタC0、スイッチ用トランジスタQN0が直列に接続され、これと並列に、キャパシタC1、スイッチ用トランジスタQN1が直列に接続され、…、これらと並列に、キャパシタCn、スイッチ用トランジスタQNnが直列に接続されており、スイッチ用トランジスタはそれぞれゲートにトリミング信号Tが入力されて導通が制御され、第j(jは2以上でn以下の整数)のキャパシタの容量は、第j−1のキャパシタの容量の2倍の値より小さいことを特徴とする。

(もっと読む)

電圧制御発振器

【課題】 電圧制御発振器の小型・低価格化を図りつつ、優れた発振特性が得られるようにする。

【解決手段】 電界効果型トランジスタT1、T2、可変容量素子P1、P2、バッファB1、B2および定電流源G1を半導体チップK1に形成し、インダクタL1、L2およびキャパシタC1、C2は低温焼成セラミック基板K2に形成し、低温焼成セラミック基板K2上に半導体チップK1をフェースダウン実装することにより、電界効果型トランジスタT1、T2、インダクタL1、L2およびキャパシタC1、C2にてコルビッツ差動型共振器を構成する。

(もっと読む)

インダクタ、共振回路、半導体集積回路、発振器、通信装置

【課題】 インダクタを大型化することなくそのQ値を高める。

【解決手段】 積層された複数の絶縁層における所定の層上にコイルパターンが形成されたインダクタであって、少なくとも2つの絶縁層上にコイルパターンが形成されるとともに各コイルパターン同士が電気的に接続されている。

(もっと読む)

発振制御装置

【課題】 VCOのf/v感度のばらつきを補正することで、VCOの安定動作とC/N劣化などの特性の劣化防止を図ることができる発振制御装置を提供する。

【解決手段】 可変共振器2を備えるVCO1と分周器6と位相比較器7とLPF8とによって構成されるPLLにおいて、可変共振器制御信号生成部10が、LPF8の出力電圧を入力してVCO1のf/v感度を検出して可変共振器制御信号を生成し、可変共振器制御信号によって可変共振器2の容量を制御する。具体的には、電圧検知回路5がLPF8の出力電圧を入力して所定の電圧を検知すると、データラッチ回路4が電圧検知回路5の検知した電圧に基づいた可変共振器制御信号を可変共振器2へ送信して可変容量の制御を行う。その結果、PLLの構成素子のばらつきや温度変化があってもVCO1のf/v感度を最適値に制御することができる。

(もっと読む)

CR発振回路および電子装置

【課題】 発振周波数の調整手段の選択余地を広げるのが望ましい。

【解決手段】 CR発振回路100において、第1発振用コンデンサC1および第2発振用コンデンサC2を並列に設け、CR発振回路100全体の容量値を選択可能に構成し、可変抵抗である、例えば第5トリミング抵抗116eを少なくとも一つ含む複数の抵抗を直列に設け、第5トリミング抵抗116eの抵抗値を調整することによってCR発振回路100全体の抵抗値を選択可能に構成し、CR発振回路100全体の容量値として選択可能な最小値CMINと最大値CMAX、およびCR発振回路100全体の抵抗値として選択可能な最小値RMINと最大値RMAXの間に、

CMIN・RMAX≧CMAX・RMIN

なる関係をもたせる。

(もっと読む)

電圧制御発振器及び通信用半導体集積回路

【課題】 周波数可変範囲が広く、良好な位相雑音特性を持ち、低コストで集積化した周波数シンセサイザを提供する。

【解決手段】 共振タンク回路(A)および前記共振タンク回路(A)の共振周期数で発振、増幅する増幅回路(B)からなるVCOにおいて、前記共振回路(A)に、発振周波数バンドを可変させる容量バンド切り替え回路(D)を備えると共に、各発振周波数バンドに対応して適した電流を前記増幅回路(B)供給するために、電流バンド切り替え回路(E)を備えることにより、発振周波数の可変範囲拡大と、各周波数バンドでの電流最適化により広帯域で良好な位相雑音特性を可能する。

(もっと読む)

電圧制御発振器

【課題】 ノイズを広帯域に亘って除去することにより、電圧制御発振器の出力信号の品質を高める。

【解決手段】 動作電圧が与えられる電源端子Vccと、制御電圧が与えられる制御端子Vtと、制御電圧に応じた発振周波数の信号を出力する出力端子Poとを備え、電源端子Vccには互いに自己共振周波数の異なる2つのバイパスコンデンサCvcc1,Cvcc2が並列接続されており、制御端子Vtには互いに自己共振周波数の異なる2つのバイパスコンデンサCvt1,Cvt2が並列接続されている。これにより、動作電圧や制御電圧に重畳しているノイズを広帯域に亘り除去されることから、出力信号の品質(C/N特性)を向上させることが可能となる。

(もっと読む)

発振回路

【課題】 負性抵抗の減少を抑制することを目的とし、また、発振周波数付近で負性抵抗を選択的に増大させること。

【解決手段】 増幅器の出力から入力への帰還によって発振を行う発振回路において、発振回路が通常備える発振のための第1の帰還とは別に、振幅及び位相推移を行う第2の帰還の2重帰還を行うことによって、発振回路の負性抵抗を所望の周波数で増加させると共に、等価リアクタンス成分を調整する。発振回路は、コルピッツ発振回路が備える負性抵抗を生成する第1の帰還回路と、コルピッツ発振回路の発振段トランジスタのエミッタ端子からベース端子に電流帰還する第2の帰還回路とによって構成することができる。エミッタ端子からベース端子への電流帰還は帰還容量を介して行う。

(もっと読む)

電圧制御発振器

【課題】発振周波数の安定化を図りつつ、位相ノイズの増加を抑えることができる電圧制御発振器を提供する。

【解決手段】電圧制御発振器は、インダクタセクション20、バラクタセクション22、ネガティブGmセクション21、トリミングキャパシタアレイ23及びバイアス回路R10〜R15,R20〜R25を備えている。バイアス回路は、上記トランジスタ26−0〜26−5,27−0〜27−5とキャパシタC10〜C15,C20〜C25との接続点N4にバイアス電圧Vbiasを与える。キャパシタを切り離すトランジスタのドレインをバイアスすることによって寄生ダイオードをオンしないようにでき、それによって位相ノイズの増加を抑制することができる。

(もっと読む)

線形容量を有する電圧制御発振器

【課題】線形及び単調な容量特性を持つ電圧制御発振器を達成し、これによる連続及び単調な利得が得られ、位相雑音の低減を可能とする。

【解決手段】 電圧制御発振器は、増幅器(5)と、インダクタ(L)、及びその制御電圧によって変化する容量をそれぞれ有する、直列に接続の第1(Cv+)及び第2(Cv−)の可変コンデンサを備える発振システム(6)とを備える。可変コンデンサの1つ(Cv+)の容量は、その制御電圧と同方向に変化し、他の可変コンデンサ(Cv−)の容量は、その制御電圧と反対方向に変化する。固定容量を有するコンデンサは、第1(Cv+)及び第2(Cv−)の可変コンデンサと直列又は並列に接続され、第1及び第2の可変コンデンサは、各々PMOS及びNMOS型トランジスタにて形成される。追加の第1及び第2の可変コンデンサの追加の列は、第1及び第2の可変コンデンサと並列に接続される事ができる。

(もっと読む)

電圧制御発振器、ならびにそれを用いたPLL回路および無線通信機器

【課題】 広い周波数可変範囲を得るために複数のバンドを用いた場合、全てのバンドにおいて、良好な位相雑音特性を有し、かつ周波数感度を同程度にすることができる電圧制御発振器を提供すること。

【解決手段】 電圧制御発振器は、インダクタ回路と可変容量回路と高周波スイッチ回路とで構成された並列共振回路と、負性抵抗回路と、周波数制御部と、周波数感度制御部とを備える。周波数制御部は、高周波スイッチ回路が有するスイッチング素子のオンオフを制御することによって、発振周波数のバンドをシフトさせる。周波数感度制御部は、使用するバンドに応じて、制御電圧に対する可変容量回路全体の容量の変化率を調整する。周波数感度制御部は、差動信号の仮想接地点に接続されている。

(もっと読む)

多層電子部品の集合基板及び多層電子部品の製造方法

【課題】 トリミング位置を簡単且つ正確に特定することが可能な多層電子部品の集合基板を提供する。

【解決手段】 本発明による多層電子部品の集合基板は、切断により複数の多層電子部品を取り出すことが可能な多層電子部品の集合基板であって、複数の絶縁層のうち所定の絶縁層上に形成されたトリミングパターン122bと、同じ絶縁層に形成され、トリミングパターン122bとの相対的な位置関係を示す認識用マーク122aとを備える。これにより、画像認識によりトリミング位置の特定を行う場合であっても、非常に簡単な処理でトリミング位置の特定を行うことが可能となる。しかも、認識用マークがトリミングパターンと同じ層に形成されていることから、層間のパターンずれなどが生じず、正確にトリミング位置を特定することが可能となる。

(もっと読む)

エバネッセントモード形結合共振器を使用する広帯域電圧制御発振器

1つの態様では、本発明は、能動素子の2つの端子の間に接続された複数の共振器を有する能動素子と、複数の共振器の間に接続された少なくとも1つの共振器とを含む電圧制御発振器を含んでいる。この少なくとも1つの共振器は、好ましくは、発振器の中に存在する選択された量のエネルギーを蓄積できるエバネッセントモード形バッファとして動作する。  (もっと読む)

(もっと読む)

LC発振器を備えたPLLの粗チューニング時間の改良

LC発振器のチューニング方法と装置が開示されている。本発明の実施形態は、ビット比較時間を適応的に制御し、最少の粗チューニング時間が得られるようにすることを含んでいる。ビット比較時間は、LC発振器のキャパシタアレイ内の対応する加重キャパシタの冗長量に逆比例してスケーリングされる。 (もっと読む)

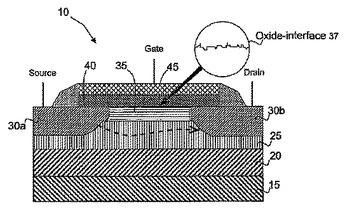

ストレインド・シリコン電圧制御発振器(VCO)

ストレインド・シリコン電圧制御発振器(VCO)は、ストレインド・シリコン層を有する第1Pチャネル金属酸化膜半導体(PMOS)装置を含み、ストレインド・シリコン層を有する第2PMOS装置に結合される。  (もっと読む)

(もっと読む)

マルチループ構成から形成されたインダクタンスループを有する集積回路パッケージ

集積回路パッケージが、リードワイアと1つまたは複数の入出力(I/O)パッケージピンとの接続から形成されるインダクタループを含む。一実施形態では、インダクタループは、集積回路チップ上の第1のボンディングパッドをパッケージの第1のI/Oピンに接続する第1および第2のワイアと、チップ上の第2のボンディングパッドをパッケージの第2のI/Oピンに接続する第3および第4のワイアとから形成される。インダクタループを完成するために、第1のI/Oピンと第2のI/Oピンは、ピン間の第3の導体によって接続される。第3の導体は、1つまたは複数のボンディングワイアを含むことができ、I/Oピンは、互いに隣接するものであることが好ましい。しかし、ループは、例えばループ長要件、空間の考慮すべき点、および/または他の設計要因もしくは機能要因に基づいて、I/Oピンの非隣接接続から形成することができる。他の実施形態では、第1のI/Oピンと第2のI/Oピンの間の接続が、I/Oピンに単一構造を持たせることによって確立される。他の実施形態では、第1のI/Oピンと第2のI/Oピンの間の接続が、パッケージ基板の表面上に、またはこの基板内に位置するメタライゼーション層によって確立される。集積回路パッケージの境界線内でインダクタループを形成することにより、空間要件における実質的な削減が実現され、これは小型化を促進する。また、集積回路は、その少なくとも1つのパラメータがパッケージのインダクタループの長さによって制御される様々なシステムのいずれか1つで実装することができる。

(もっと読む)

(もっと読む)

81 - 100 / 100

[ Back to top ]