Fターム[5J081KK07]の内容

LC分布定数、CR発振器 (9,854) | 制御手段及び要因 (1,418) | 一次要因 (534) | 容量 (335)

Fターム[5J081KK07]の下位に属するFターム

素子内容量 (235)

Fターム[5J081KK07]に分類される特許

21 - 40 / 100

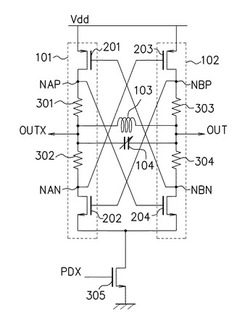

半導体回路

【課題】安定した動作を行うことができる半導体回路を提供することを課題とする。

【解決手段】ソースが第1の電位ノードに接続される第1のpチャネルトランジスタ(201)と、ソースが第2の電位ノードに接続される第1のnチャネルトランジスタ(202)と、ゲートが第1のnチャネルトランジスタのドレインに接続され、ドレインが第1のnチャネルトランジスタのゲートに接続される第2のpチャネルトランジスタ(203)と、ゲートが第1のpチャネルトランジスタのドレインに接続され、ドレインが第1のpチャネルトランジスタのゲートに接続される第2のnチャネルトランジスタ(204)と、第1のpチャネルトランジスタ及び第1のnチャネルトランジスタのドレイン間に接続される第1の抵抗(301,302)と、第2のpチャネルトランジスタ及び第2のnチャネルトランジスタのドレイン間に接続される第2の抵抗(303,304)とを有する。

(もっと読む)

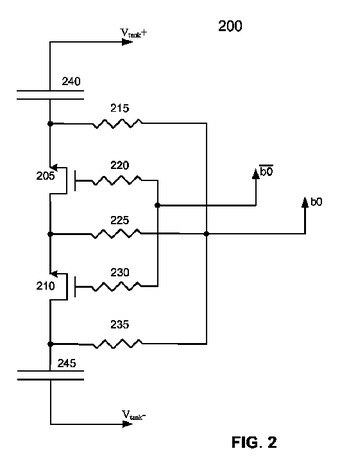

キャパシタスイッチング回路

キャパシタンススイッチング素子(200)が、トランジスタ(205、210)によって直列に接続された、第1のキャパシタ(240)と第2のキャパシタ(245)とを含む。トランジスタのゲートは、一組の抵抗器(220、230)を介して第1の信号(b0/)によってバイアスをかけられ、ソースおよびドレインは、第2の組の抵抗器(215、225、235)を介して第2の信号(b0)によってバイアスをかけられる。信号はレベルシフトされており、相補的であってよい。素子をオンにするためには、第1の信号(b0/)をVDDに設定することができ、第2の信号(b0)をゼロに設定することができる。素子をオフにするためには、第1の信号(b0/)をVDD/2の倍数に設定することができ、第2の信号(b0)をVDD/2の倍数プラス1(the multiple plus one)に設定することができる。素子が発振器同調回路で使用されるとき、トランジスタの圧力ストレスが低減され、トランジスタを薄酸化物で製作することができる。発振器は、セルラアクセス端末のトランシーバにおいて使用されてもよい。  (もっと読む)

(もっと読む)

温特補正機能付き発振回路およびその製造方法

【課題】 発振周波数を補正するためのメモリなどが不要な温特補正機能付き発振回路およびその製造方法を実現する。

【解決手段】 温特補正機能付き発振回路10は、第1の発振回路21と、第2の発振回路22と、第1の発振回路21が発生する発振周波数を理想の発振周波数に近い発振周波数に補正するための補正回路50とを備える。補正回路50は、第1の発振回路21の発振周波数f1と、第2の発振回路22の発振周波数f2との差分(f1−f2)を検出し、その検出した差分に補正係数αを乗じ(α・(f1−f2))、その補正された差分を第1の発振回路21の発振周波数に加算し(f1+α・(f1−f2))、それを出力する動作を行う。

(もっと読む)

PLL回路

【課題】高周波動作において、互いに容量が異なる複数のコンデンサの組み合わせを切り替えて電圧制御発振器の発振周波数帯域を切り替える際に、全ての発振周波数帯域同士を重なり合わせることが可能なPLL回路を提供することを目的とする。

【解決手段】互いに容量が異なる複数のコンデンサ51−1〜51−nの組み合わせを切り替えることにより発振周波数帯域を切り替える電圧制御発振器2を備えるPLL回路1において、電圧制御発振器2が高周波動作しているとき、容量が比較的大きなコンデンサ52−4又はコンデンサ52−5が選択されなくなる場合、補正用のコンデンサ5−1又はコンデンサ5−2を選択して電圧制御発振器2の全体の容量を大きくする。

(もっと読む)

VCO周波数チューニングのための、オーバーラップする2セグメントキャパシタバンク

【解決手段】(例えばFM受信機中の)VCOは、LC共振タンクを含む。LC共振タンクは、粗同調キャパシタバンクおよび微同調キャパシタバンクを含む。粗同調キャパシタバンクは複数のデジタル制御粗同調キャパシタエレメントを含み、アクティブな際に各々は第1キャパシタンス値を供給する。微同調キャパシタバンクは複数のデジタル制御微同調キャパシタエレメントを含み、アクティブな際に各々は第2キャパシタンス値を供給する。キャパシタミスマッチの現実的な問題に対処するため、VCOチューニング範囲の全体にわたるキャパシタンスオーバーラップが、微キャパシタバンクのデジタル制御微同調キャパシタエレメントの全てがアクティブな場合に、微キャパシタバンクのキャパシタンス値が第1キャパシタンス値より大きくなるように第1及び第2キャパシタンス値を選択することによって生成される。 (もっと読む)

自動調整発振器

【課題】チャージポンプを用いずに、出力周波数の精度を高くすることのできる自動調整発振器を提供する。

【解決手段】発振器10は、発振回路11、第1電圧供給回路13、第2電圧供給回路14及び調整値生成回路16を備えている。第1電圧供給回路13は、基準時間で第1電圧V1が基準電圧Vrefに到達するような時定数となる抵抗値の抵抗器R1とキャパシタン

スのキャパシタC1とを備える。第2電圧供給回路14は、発振回路11の周波数に応じたパルス信号S1,S2によってスイッチングを行なう第1及び第2スイッチング手段SW1,SW2によって第2電圧V2を上昇させる。調整値生成回路16は、第2電圧V2が第1電圧V1よりも先に基準電圧Vrefになった場合には、周波数を低くする調整値を

発振回路11に供給し、第2電圧V2が第1電圧V1よりも遅れて基準電圧Vrefになっ

た場合には、周波数を高くする調整値を発振回路11に供給する。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

高周波発振器

【課題】高価な誘電体共振器やバラクタダイオードを使用することなく、廉価に制作することができ、また回路面積が小さく小型化が可能となるようにする。

【解決手段】誘電体基板1上に形成されたマイクロストリップ線路2において、増幅素子3の入力端のゲートが入力端側線路2aに接続され、出力端のドレインが出力端側線路2bに接続され、ソースが接地電極5を介して基板裏面の接地面7に接続される。そして、上記増幅素子3の上面に、例えば棒状の金属体10を絶縁性接着剤9によって接着し、この金属体10をマイクロストリップ線路2の伝送線路方向に配置することで、この金属体10の一方端を入力端側線路2a、他方端を出力端側線路2bに容量性結合する。この金属体の結合は、一端のみでもよい。これによれば、増幅素子3からの出力が、容量C12、インダクタンスL、容量C11を通って入力端へ帰還し、発振が行われる。

(もっと読む)

発振器及びそれを用いた周波数生成回路並びに無線通信システム

【課題】LC型発振器において、高調波歪みによる位相雑音の劣化が小さく、かつ発振振幅の増大化を図り、これにより良好な低位相雑音特性を有する発振器及びそれを用いた通信システムを提供する。

【解決手段】トランジスタからなる少なくとも1つ以上の電圧-電流変換部と、1対の容量性素子と誘導性素子からなるLCタンクを2つ有している共振器とを具備して成り、前記の電圧-電流変換部の出力端子は、前記の共振器に接続され電流-電圧変換されたのちに、前記電圧-電流変換部の入力端子に接続されることにより、帰還ループが構成されて成り、前記共振器を構成している2つのLCタンクを構成する誘導性素子が相互誘導結合されており、前記相互結合係数がおおよそ-0.6であることを特徴とする。

(もっと読む)

発振器および位相同期ループ

【課題】発振器の位相雑音を低減し、位相同期ループの消費電力および位相雑音を低減する。

【解決手段】発振器は、共振回路の容量値に応じて発振周波数が可変する構成であって、外部から入力する外部クロックと設定データに応じて、オーバーフロー信号を間欠的に出力するアキュムレータ11と、オーバーフロー信号の間欠入力に応じてオン・オフするスイッチ12と、スイッチ12を介して共振回路に接続される固定容量値を有する容量素子C2とを備え、設定データに応じて間欠的に出力されるオーバーフロー信号の入力によりスイッチ12がオンとなるオン時間における発振周波数と、オーバーフロー信号が入力されないときにスイッチ12がオフとなるオフ時間における発振周波数との間で、オン時間とオフ時間の時間割合に応じた平均発振周波数を可変させる。

(もっと読む)

電圧制御発振回路

【課題】製造コストの追加なく一般的に用いられる可変容量素子を利用し、位相雑音特性に優れたRTW形式の電圧制御発振回路を実現できるようにする。

【解決手段】電圧制御発振回路は、ループ状の伝送線路15と、信号線路と接続されたアクティブ回路17と、信号線路と接続され複数の可変容量ユニット23を有する可変容量部21とを備えている。各可変容量ユニット23は、可変容量素子31と、可変容量素子31に制御電位を印加する制御端子41と、可変容量素子31に基準電位を印加する基準電位端子43とを有している。少なくとも2つの可変容量ユニット23は、基準電位が互いに異なっている。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

発振回路は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ、コンデンサ、およびオプションコンダクタも含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。  (もっと読む)

(もっと読む)

信号処理装置及び信号処理方法

【課題】最大の周波数マージンで、発生させる発振周波数をロック状態にする。

【解決手段】ループフィルタ23は、発振周波数における所定の特性に基づいて、入力される制御電圧に対応して発振周波数を発生させるVCO63であって、所定の特性が粗調整されるVCO63に、制御電圧を入力し、VCO粗調整回路135は、制御電圧が所定の設定範囲を超えた場合に、VCOによる所定の特性を、複数の特性のうちのいずれかに粗調整し、DAC133は、制御電圧が所定の設定範囲内で変化する場合に、発振周波数がロック状態とならないとき、所定の設定範囲を広げる方向に更新する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

発振器

【課題】内蔵するICチップの内容を外部から設定し、書き換えることで回路定数や回路方式あるいは分周数を実装機器の仕様に合せて切り換え可能とした融通性の高い発振器を提供する。

【解決手段】内蔵するICチップ3に発振回路と共に複数の回路定数や回路方式の回路、あるいは複数の分周数の分周回路を備えると共に、該ICチップに不揮発メモリの領域、あるいは分周回路領域を設け、発振器の回路定数や回路方式を当該不揮発メモリに外部から書き込んだデータで切り換える構成とした。

(もっと読む)

発振回路装置

【課題】 この発明は、負性抵抗を示す帯域が広くして、使用できる発振周波数を多くすることを目的とするものである。

【解決手段】 この発明の発振回路装置は、相互接続された一対のトランジスタ1、2と抵抗・容量の回路網で構成された発振部100と、発振部100に接続されるループ状の伝送線路で構成された共振部200と、を備え、前記抵抗・容量の回路網の抵抗値及び容量値を前記発振部が第1の周波数帯で負性抵抗となり、その第1の周波数帯より高い周波数帯においてフラットな負性抵抗を示すように設定したことを特徴とする。

(もっと読む)

デジタル制御発振器及びこれを用いた位相同期回路

【課題】発振周波数を線形に近くかつきめ細やかに制御可能なデジタル制御発振器を提供する。

【解決手段】正相発振信号を出力する正端子213と、逆相発振信号を出力する負端子214と、センタータップ210とを有し、正端子とセンタータップとの間の任意の位置に第1の接点211を備え、負端子とセンタータップとの間の第1の接点に対応する位置に第2の接点212を備える差動インダクタ200と、正端子と負端子との間に接続され、第1のデジタル制御コードによってキャパシタンスを2値に変化させる第1の可変キャパシタを複数含む第1の可変キャパシタバンク220と、第1の接点と第2の接点との間に接続され、第2のデジタル制御コードによってキャパシタンスを2値に変化させる第2の可変キャパシタを複数含む第2の可変キャパシタバンク240と、正端子と負端子との間に接続される負性抵抗230とを具備する

(もっと読む)

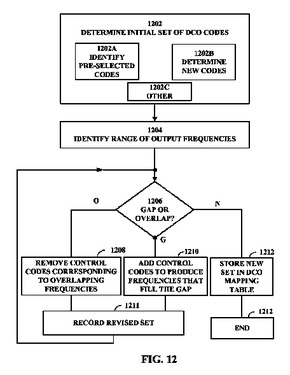

デジタル制御発振器のためのダイナミック較正技法

デジタル制御発振器(DCO)を較正するための技法を開示する。本開示の一態様では、DCOを動作させるための制御コードの初期セットを判断する。初期セットから生成された出力周波数レンジを識別する。周波数レンジにおけるギャップまたはオーバーラップインスタンスを識別する。オーバーラップの場合、修正されたセットを確立するためにオーバーラップインスタンスに対応する制御コードを初期セットから除去する。ギャップの場合、ギャップを充填する周波数値を生成するために、制御コードを初期セットに追加する。同じことを実行するための装置も開示する。  (もっと読む)

(もっと読む)

搬送波発振器

【課題】低消費電力および低コストへの要求に応える通信装置を提供する。

【解決手段】任意の周波数の搬送波を生成する搬送波発振器であって、周期信号を生成するエネルギー貯蔵タンク21−1とエネルギー貯蔵タンク21−1に合体され前記周期信号の振幅を増幅するように構成された増幅器21−2とを有し、第1のインピーダンスを示す発振器21と、前記第1のインピーダンスより小さい第2のインピーダンスを示すアンテナ23と、前記発振器21と前記アンテナ23の間に接続され、第3のインピーダンスを提供するように構成されて、前記発振器から前記アンテナに向けて見た場合の前記第2及び第3のインピーダンスの合成インピーダンスが、任意の周波数で前記搬送波を生成するよう前記発振器21を促進するのに充分な大きさとなるようにしたネットワーク22とを備える。

(もっと読む)

21 - 40 / 100

[ Back to top ]