Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

681 - 700 / 713

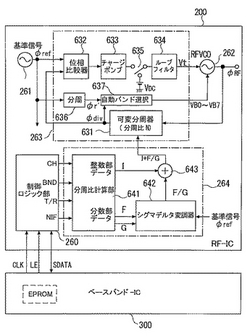

通信用半導体集積回路

【課題】 広い周波数範囲で高精度に発振動作ができ、占有面積を増大させずにVCOの使用周波数帯を短時間に選択できる通信用半導体集積回路の提供。

【解決手段】 発振器と発振信号を任意の分周比(整数I+分数F/G)で分周可能な可変分周器とを有する発振回路を備えた通信用半導体集積回路で、外部からの送信開始指示と使用周波数帯情報により、可変分周器に与える分周比を算出の分周比算出回路と、分周比算出回路により算出の分周比により可変分周器を動作させ、発振器に所定レベルの電位を制御電圧として供給した状態で可変分周回路の出力信号の位相と基準信号を分周する固定分周回路の出力信号の位相とを比較して発振器の発振周波数帯を選択のバンド選択回路とを設け、バンド選択回路により発振器の発振周波数帯を選択後、発振器の制御電圧もしくは制御電流を周波数制御回路の出力に切り替えて発振回路を動作させる。

(もっと読む)

PLL回路用のシステム及び方法

【課題】ノードに雑音を導入せずに電圧制御発振の特性を測定し、初期化することのできるPLL回路を提供する。

【解決手段】システムは、アップ及びダウン信号を受信し、その信号に基づいてその出力の電圧を維持するチャージポンプ230と、チャージポンプ230に結合され、第1のモードまたは第2のモードのいずれかでチャージポンプ230へアップ及びダウン信号を供給するように制御する制御回路220とを備えたPLL回路200を有する。制御回路220は、第1のモードでは位相周波数検出器210から受信された信号をアップ及びダウン信号として通過させ、第2のモードでは位相周波数検出器210から受信された少なくとも1つの信号を無効にしてチャージポンプ230の出力の電圧を選択可能な試験電圧へ駆動するように構成される。

(もっと読む)

遅延回路、半導体集積回路、位相調整回路、DLL回路およびPLL回路

【課題】 大きな遅延時間を得ることができると共に、遅延時間をきめ細かく制御することが可能な遅延回路を得る。

【解決手段】 インバータ1〜nを複数段直列接続して形成され、各P−chトランジスタ1a〜naの基板電極に電位VDDHを供給し、各P−chトランジスタ1a〜naのソース電極にスイッチ1c〜ncが接続され、そのソース電極に供給する電位として電位VDDHまたは電位VDDLを選択可能にされ、また、電位VDDHおよび電位VDDLのうちの少なくとも一方の電位は調整自在にされたものである。

電位VDDHまたは電位VDDLの電位調整、およびスイッチ1c〜ncによる電位選択に応じて、P−chトランジスタ1a〜naに逆バイアスまたは順バイアスをかけ、大きな遅延時間を得ることができると共に、遅延時間をきめ細かく制御することができる。

(もっと読む)

PLL回路のノイズを抑制するシステム及び方法

位相ノイズおよび内部発生器内のミスマッチによって発生するノイズを抑制して周波数ジェネレータのSNRを向上させるシステム及び方法である。このノイズ抑制はスプリアスノイズ信号を発生器のループ帯域幅外にシフトする変調方式によって行われる。このシフトにより、例えば発生器の信号パス上のフィルタを使用して、ノイズ信号を完全に除去できるか又は所望の程度まで除去できる。一実施形態では、所望の程度のノイズ抑制を行うため、シグマデルタ変調器により、PLL回路のフィードバックパス上のパルススワロ分周器の値が制御される。別の実施形態では、PLL回路に入力されるレファレンス信号を変調することにより、ノイズが抑制される。別の実施形態では、所望の周波数シフトを行うため、前記の変調形式が組み合わされる。これら変調技術により、ロックタイムがより速くなるとともに、周波数ジェネレータのSNRが大幅に向上する。  (もっと読む)

(もっと読む)

アイドル時間ループスタビライザを備えた電荷ポンプPLLに基づいたバーストモード受信器

【課題】

【解決手段】バーストモード受信器は、入来信号を受信するデジタル位相検出器を含む。前記受信器はまた、前記デジタル位相検出器からのパルス信号を受信して、前記入来クロック位相と前記ローカル生成ロック位相を比較して前記電荷ポンプを制御する電荷ポンプと、前記電荷ポンプからの電荷値を受信し、制御信号を生成するループフィルタと、前記制御信号を受信し、回復されたクロックを生成し、前記回復されたクロックをデジタル位相検出器に供給するローカルクロック生成器とを含む。

(もっと読む)

PLL回路およびDLL回路

【課題】 ロックするまでの時間を短縮することができ、初期制御電圧を、回路の用途に応じて変更することができ、製造条件等により、ロックするまでの時間が変動することを防ぐことのできるPLL回路およびDLL回路を提供する。また、ジッタを迅速に低減することのできるDLL回路を提供する。

【解決手段】 PLL回路は、位相比較器3と、チャージポンプ4と、ループフィルタ5と、電圧制御発振器6と、選択信号に応じて制御電圧のレベルを選択する電圧設定回路10と、複数個の選択信号のうち少なくとも1つを出力し、電圧制御発振器6において周波数の増減された出力クロックの、入力クロックに対する逓倍数を検出し、複数個の選択信号の中から最適な選択信号を特定し、電圧設定回路10に出力する設定値判定回路9とを含み、各回路は、待機信号に応じて処理の開始および停止を行なう。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラが、提供される。PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL)とを備えている。このPLLは、誤り訂正信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器と、前記発振器に結合され、前記基準信号を受信し、且つ前記基準信号と、フィードバック信号との間の位相差に基づいて誤り訂正信号を生成させる位相周波数検出器(PFD)と、前記PFDに結合され、周期的にPFDが誤り訂正信号を生成することができるようにする抑制回路とを備えている。  (もっと読む)

(もっと読む)

周波数可変発振回路並びにそれを用いた位相同期回路及びクロック同期回路

【課題】低い電源電圧で動作し、かつ、高い周波数で発振することができる周波数可変発振回路並びにそれを用いた広い発振周波数範囲を有する位相同期回路及びクロック同期回路を提供すること。

【解決手段】pMOS及びnMOSトランジスタのゲートを相互に接続して入力端子とし、かつ、ドレインを相互に接続して出力端子とした相補型増幅回路を用いて差動増幅回路及び入出力端子を互いに交叉して接続した正帰還回路を構成し、差動増幅回路の出力端子間に正帰還回路を接続し、前記相補型増幅回路のソース電流を制御するための周波数制御信号をゲートに入力するMOSトランジスタと前記相補型増幅回路とを電源端子と接地端子の間に直列に接続して構成した遅延回路を環状に縦続接続して周波数可変発振回路を構成する。

(もっと読む)

通信用半導体集積回路および無線通信システム

受信用VCO(250)と送信用VCO(240a,240b)と中間周波数用VCO(230)のうち少なくとも1つのVCOが変復調回路と共に1つの半導体チップ上に形成された通信用半導体集積回路において、オンチップのVCOを複数の周波数帯で動作可能に構成し、また該VCOの発振周波数を測定する回路(22)および測定された値を記憶する記憶回路(18)と該記憶回路に記憶されている測定値と外部からの設定値とを比較して上記VCOの使用周波数帯を決定する回路(19)を設けるとともに、該記憶回路の記憶データを外部へ読出しまた外部から書き込むことができるように構成した。  (もっと読む)

(もっと読む)

電圧制御発振器プリセット回路

周波数合成回路は、周波数が或る値にプリセットされ、入力電圧に応じて発振信号を生成する電圧制御発振器(40)を含む。デジタル処理装置(60)は、前記回路が位相ロックループモードで動作することをディスエーブルにすることが出来る。前記回路がディスエーブルにされたら、前記装置は、各々の第1及び第2ループフィルタ入力電圧値に応じて前記発振信号の第1及び第2周波数を決定する。更に、前記装置は、2つの前記周波数、前記周波数分割器の分割比及び前記基準信号から制御値を生成する。前記回路は、前記制御値に応じて前記ループフィルタ入力電圧をプリセット値にプリセットするよう構成されるD/A変換器(70)を更に有する。前記発振器の出力が対応入力プリセット値において発振したら、前記装置(60)は、前記D/A変換器(70)をディスエーブルにし、前記周波数合成回路が位相ロックループモードで動作することをイネーブルにする。  (もっと読む)

(もっと読む)

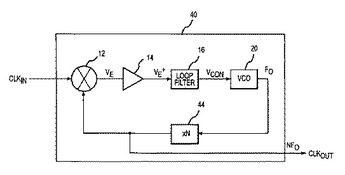

低電力と低いタイミング・ジッタのフェーズ・ロック・ループと方法

フェーズ・ロック・ループは、入力クロック信号から出力クロック信号を生成する。出力クロック信号は、クロック・ツリーを通して結合されて、出力クロック信号の位相を入力クロック信号の位相と比較する位相検出器にフィード・バックされる。出力クロック信号は、位相検出器から出力を受け取るように結合された制御入力を有する電圧制御発振器と、電圧制御発振器の出力に結合された周波数逓倍器とによって生成される。を持っている電圧制御発振器によって生成される。結果として、電圧制御発振器が相対的に低い周波数で動作することによって相対的に小さな電力を使用する一方、周波数逓倍器により生成されたCLKOUT信号は、相対的に高い周波数を持っている。  (もっと読む)

(もっと読む)

PLL回路および高周波受信装置

【課題】 分周比を定めるカウント周期が設定される分周用のカウンタを備えるPLL回路において、周期設定時間を短縮する。

【解決手段】 メモリ28は、分周するカウンタ24の設定周期を複数パターン記憶しており、シリアルバスSBを介してPLL回路61の外部から入力される選択信号によって指定された設定周期を読み出す。メモリ28から読み出されたデータ量の多い設定周期を、パラレルバスPBを介してカウンタ24に入力するので、カウンタ24への周期設定には時間がほとんどかからない。また、カウンタ24のbit数が増えても設定時間は長くならない。しかも、受信チャンネルが決まっている領域では、従来と同じシリアルバスSBのインターフェースを用いても、メモリ28に記憶されている設定周期を選択するためのデータ量の少ない選択信号を伝送し、カウンタ24の周期設定時間を短くすることができる。

(もっと読む)

低ジッタのスイッチドキャパシタ周波数シンセサイザのための制御信号の生成

位相検出器および制御信号のジェネレータ(140)は、遅延されていないアップ信号(620)および遅延されていないダウン信号(625)を生成するために、基準信号(基準クロック)およびフィードバック信号(フィードバック信号)に応答する。プログラム可能な遅延ユニット(630,635)は、チャージポンプにアップ信号およびダウン信号を与えるために、遅延されていないアップ信号および遅延されていないダウン信号を遅延させる。アップ信号およびダウン信号に応答するよう構成される分周器(655)は、分周されたクロック信号(660)を与える。ノンオーバーラップクロック生成器は、スイッチドキャパシタリップル平滑フィルタのためにノンオーバーラップ保持偶数およびノンオーバーラップ保持奇数信号(hold_e,hold_o)を与えるために、分周されたクロック信号に応答するよう構成される。  (もっと読む)

(もっと読む)

干渉に堅固な水晶発振器用バッファ

【課題】

【解決手段】RF信号リークによって入り込んだ不要な擬似的成分を抑制する基準周波数信号分配回路構成の方法と回路構成が開示されている。方法と回路構成は基準周波数信号経路に沿ったバッファの部品を再配置して、それにより、回路構成に入り込んだRFリーク経路と関係する導電性及び誘導性成分を抑制することを含んでいる。位相周波数検出器における不要トーンのサブサンプリング、またはバッファの信号経路における基準信号と干渉トーンの間の相互変調による擬似成分を抑制するために、バッファの後にフィルタを用いてもよい。

(もっと読む)

フェーズロックドループ回路

入力基準信号Urefと入力信号Up,inとの間の位相差ΔΦを検出するための位相比較器であって、Kpが前記位相比較器の位相検出器ゲインである位相比較器と、入力信号Uvco,inに応じて角周波数ωvco,outを有する周期的な出力信号Uvco,outを生成するための電圧制御発振器(VCO)であって、Kvcoが前記電圧制御発振器の電圧制御発振器ゲインである電圧制御発振器(VCO)と、フェーズロックドループ回路の動作中にループゲインK:=Kp×Kvcoが所定の範囲内のままとなるようにフェーズロックドループ回路の動作中に前記位相検出器ゲインKpを制御するようになっているコントローラと、を備えるフェーズロックドループ回路(PLL回路)。  (もっと読む)

(もっと読む)

スイッチトキャパシタフィルタ及びフィードバックシステム

ループフィルタ(30)は、電流信号の入力端と基準電圧との間に設けられた第1の容量素子(31)と、上記入力端と第1の容量素子(31)との間に設けられたスイッチトキャパシタ回路(32)と、第1の容量素子(31)及び前記スイッチトキャパシタ回路(32)に並列に設けられた第2の容量素子(33)とを備えている。スイッチトキャパシタ回路(32)において、第3の容量素子(321)が第1の容量素子(31)側に接続されるとき、第4の容量素子(322)は第2の容量素子(33)側に接続される。上記構成のループフィルタ(30)において、第2の容量素子(33)の容量値を、第3及び第4の容量素子(321,322)の容量値よりも大きく設定する。 (もっと読む)

マルチバンドOFDMベースの超広帯域無線の周波数発生

本発明は、一般的に言えば、1つまたは複数の周波数シンセサイザ(たとえばPLLなど)および1つまたは複数の単一サブバンド・ミキサを使用して、周波数帯域の対応するサブバンドを占有する通信信号を受信するために少なくとも3つのローカル発振器信号の発生を提供する。ある実施形態によれば、所与のローカル発振器信号の出力パスには1つの単一サイドバンド・ミキサしかなく、それによってスパーを低減する。ある他の実施形態によれば、3つのローカル発振器信号が連続して発生される。  (もっと読む)

(もっと読む)

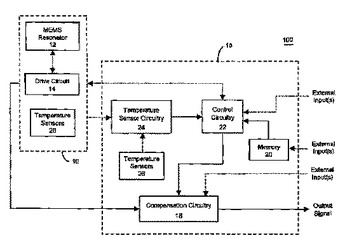

周波数および/または位相補償された微細電気機械発振器

本明細書で説明され、図示される多数の発明がある。1態様で、本発明は、出力信号を生成する微細電気機械共振器と、微細電気機械共振器の出力信号を受け取り、値のセットに応答して第2周波数を有する出力信号を生成するために微細電気機械共振器に結合された周波数調整回路構成と、を有する、補償された微細電気機械共振器を対象とする。1実施形態で、値を、微細電気機械共振器の動作温度および/または微細電気機械共振器の製造変動に依存する、微細電気機械共振器の出力信号の周波数を使用して、決定することができる。1実施形態で、周波数調整回路構成に、周波数逓倍器回路構成(たとえば、PLL、DLL、ディジタル/周波数シンセサイザ、および/またはFLLならびにこれらの任意の組合せおよびその組み合わせの変更)を含めることができる。周波数調整回路構成に、それに加えてまたはその代わりに、周波数分周器回路構成(たとえば、DLL、ディジタル/周波数シンセサイザ(たとえば、DDS)、および/またはFLL、ならびにこれらの任意の組合せおよびその組み合わせの変更)を含めることができる。  (もっと読む)

(もっと読む)

通信システム

無線周波数送信機及び受信機における標準の周波数発生回路は、第1の基準周波数信号を出力するように動作する第1の電圧制御発振器と、第2の基準周波数信号を出力するように動作する第2の電圧制御発振器とを含む。また、位相同期ループ回路は、第1及び第2の基準周波数信号を受信するように接続され、第1の基準周波数信号から発生される一組の出力基準周波数信号の第1サブセット、及び第2の基準周波数信号から発生される出力基準周波数信号の第2サブセットとを有する一組の出力基準周波数信号を出力するように動作する一組の切替可能な分周器を含む。さらに、位相同期ループ回路は、外部の基準周波数信号及びフィードバック基準周波数信号を受信するように接続され、かつ、所望の第1及び第2の基準周波数信号を維持するために、受信した外部の基準周波数信号及びフィードバック基準周波数信号に従って第1及び第2の電圧制御発振器へ制御電圧を供給するように動作するVCO制御手段を含む。第1及び第2の基準周波数信号は、一組の出力基準周波数信号における出力基準周波数信号の周波数に等しくない。 (もっと読む)

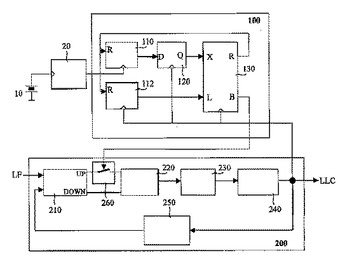

PLL回路

本発明は、位相又は周波数検出回路(210)の出力信号に応じて制御される発振回路(240)を有する位相同期ループ装置に関し、切替制御手段(130)は、所定の閾値周波数が供給される第1のタイマ手段(110)及び発振回路(240)の出力周波数が供給される第2のタイマ手段(112)の出力に応答して遮断信号を発生するように設けられる。遮断信号に基づいて、遮断手段(260)は、発振回路(240)への出力信号の供給を抑制する。これにより、PLL装置の出力周波数は、周波数閾値を超えて変化することが回避可能となるとともに、唯1つのPLL回路だけで済むことになる。

(もっと読む)

(もっと読む)

681 - 700 / 713

[ Back to top ]