Fターム[5J106DD23]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 同期化クロック制御回路 (365) | 分周比・カウンタ値制御 (46)

Fターム[5J106DD23]に分類される特許

1 - 20 / 46

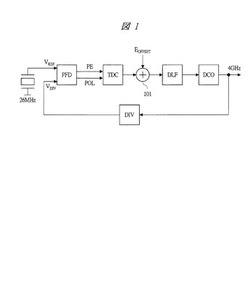

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

PLL回路

【課題】本発明は、遅延素子の遅延時間のばらつきを補償するように、デジタルコードを補正する必要のないTDCを提供することを目的とする。

【解決手段】基準信号の周波数に対して所望倍数の周波数を有する出力信号を出力する発振部と、基準信号についての出力信号の整数分周及び小数分周の和並びに当該所望倍数について差分を計算し、発振部に当該差分を0にするように出力信号を出力させる位相比較部と、を備えるPLL回路において、TDC2は、小数分周の初期値を設定し、初期値を計測値として出力するデジタルコード発生器23と、初期値に基づく位相比較部及び発振部の動作後に、当該差分を0にする方向に、小数分周の分解能を1ステップとして段階的に、小数分周を初期値から最適値へと更新し、最適値を計測値として出力するデジタルコード発生器23及び加減算器24と、を備える。

(もっと読む)

発振回路およびそれを用いた電子機器

【課題】スペクトルのピークを抑制する。

【解決手段】発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。プログラマブル分周器18は、その分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号CKOUTを設定された分周比で分周し、分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKREFと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。VCO(電圧制御発振器)14は、ループフィルタ12から出力される位相差信号S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえることにより出力クロック信号CKOUTのスペクトルを拡散させる。

(もっと読む)

シリアル・データ通信装置のDPLL回路

【課題】PLCで設計・構成するシリアル・データ通信の高速化を図ることができ、しかも受信データのジッタ許容範囲を明確にできる。

【解決手段】DPLL回路10のうち、データシフト回路DS1〜DS3は受信データからソースクロックCLKで同期を取った複数のシリアル・データを生成する。排他的論理和回路EX_ORは一対のシリアル・データから受信データの変化点を検出する。カウンタDPLCNTは、最大カウント値nが設定され、変化点から次の変化点までをソースクロックをカウントする。一致判定回路ANDはカウンタのカウント値が予め設定したカウント値n/2に一致したときに受信クロックとして出力する。ハイレベル・データ・リンク・コントローラ・モジュール(HDLC−IP)20は、受信クロックを使って受信データ(シリアル・データ)の転送制御を行う。

(もっと読む)

クロック発生装置及びクロック信号生成方法

【課題】CPUに供給するクロック信号の周波数に関わらず、周辺回路に所定の周波数のクロック信号を供給することができるクロック信号生成回路及びクロック信号生成方法を提供する。

【解決手段】本発明にかかるクロック信号生成回路は、CPUに入力される第1クロック信号から、周辺回路に入力される所定の周波数を有する第2クロック信号を生成する。外部から入力される逓倍比及び分周比のうち少なくとも1に基づき、発振子が出力するクロック信号から入力される第1クロック信号を生成する第1クロック生成部と、第1クロック信号から第2クロックを作成するための基準値を算出する基準値算出部と、第1クロック信号のカウント値と基準値との比較結果に基づき、第2クロックを生成する第2クロック生成部とを有し、基準値算出部は、逓倍比及び分周比のうち少なくとも1つが変更され第1のクロック信号の周波数が変更されると、基準値を再度算出する。

(もっと読む)

PLL回路

【課題】周波数やロックアップ時間が変動したり、PLL特性が劣化したりするのを抑えることのできるPLL回路を提供する。

【解決手段】演算器15a,15bは、出力信号の目標の周波数を示す目標周波数設定値が変化した時、フラクショナル分周器17に対して目標周波数設定値で示される周波数と異なる周波数を示す周波数設定値を複数回設定する。そして、演算器15a,15bが周波数設定値を複数回設定した後に、演算器15a,15bから出力される周波数設定値は、目標周波数設定値と同じ値になる。これにより、周波数の引き込み動作時に、アナログスイッチング素子を用いてループフィルタの切り替えを行う必要がないため、スイッチング切り替え時に発生するノイズや、切り替え前後のループフィルタに生じる電圧差によって、発振器にノイズが発生することがない。

(もっと読む)

スペクトラム拡散クロック生成回路及びその制御方法

【課題】変調度が安定しない。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

(もっと読む)

クロック信号生成装置及び電子装置

【課題】目標周波数が変更されても、生成するクロック信号の周波数を短時間で目標周波数に一致させるクロック信号生成装置、及び、電子装置を提供することを目的とする。

【解決手段】第1制御部は、設定された目標周波数が第1の目標周波数から第2の目標周波数に変更されると、第1の所定のタイミングで、第1設定数として第3の数よりも小さい第5の数を前記第1カウンタに設定するとともに、第2設定数として第4の数よりも小さい第6の数を前記第2カウンタに設定し、第1の所定のタイミングの後の第2の所定のタイミングで、第3の数を前記第1カウンタに設定するとともに、前記第4の数を前記第2カウンタに設定する。

(もっと読む)

ADPLL回路、半導体装置及び携帯情報機器

【課題】ADPLL環境下またはADPLL環境に近い環境下において、ABSの精度向上手段を提供し、ABSの処理時間短縮を実現する。

【解決手段】ABS103中のデジタル周波数比較器103−1に、DPFD102の出力するDPE信号の初期位相差を格納するDFFを用意する。ABS動作開始直後に、DPFD102が出力するDPE信号はDPFD102の内部回路の初期位相差を表すものであるとしてDFFに記録する。以後デジタル周波数比較器103−1は入力されるDPE信号からDFFに記録された初期位相誤差を引いたものでABSを行い、高速かつ安定したABS動作の実現を図る。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

シンセサイザと、これを用いた受信装置及び電子機器

【課題】シンセサイザにおけるデジタル的な周波数制御に起因した位相雑音性能の悪化。

【解決手段】本発明のシンセサイザは、基準発振器から出力された基準発振信号が入力される比較器と、比較器の出力側に接続されたフィルタと、フィルタの出力側に接続されて発振信号を出力する発振器と、発振器の出力信号を制御部からの制御信号に基づいて分周する分周器とを備え、比較器は、分周器からの出力信号と基準発振器からの出力信号とを比較してこの比較結果を示す信号をフィルタに出力すると共に、制御部は、温度を検出する検出器の検出結果に基づいて分周器の分周比を時間間隔Tで制御し、時間間隔Tとフィルタのカットオフ周波数fcとの関係は、1/T≧fcを満たす構成である。

(もっと読む)

デジタル放送受信装置、時刻情報生成回路、及びデジタル放送受信方法。

【課題】

従来の複数PCRに同期したSTCクロック再生方法は、複数チャンネル毎にPCRとの差分情報を参照するVCXOを独立に備えて複数のマスタクロックを生成し、これらマスタクロックを互いに独立に使用してSTCクロックを再生するPLLを有する構成となっており、高価な回路構成となっていた。

【解決手段】

複数PCRに同期させるために得られた各差分情報を一定周期で切り替えて、一組のVCXOに供給し、時分割にマスタクロックを生成し、各STCクロックを再生するPLLを機能させる。上記、切り替え時に未選択側の差分情報が必要なPLLは出力クロックの変動を抑えるためにPLL内部の位相比較をHoldさせることにより、安価で安定度の良い回路構成を可能にする。

(もっと読む)

同期周波数合成器

【課題】同期周波数合成器によるクロック生成装置を提供する。

【解決手段】クロック生成装置において、2つの入力クロックに関連付けられた基準位相の範囲内の位相値を有する出力を生成する位相補間器121を有する。ロジック・ユニット130は、位相補間器121の複数の位相設定を決定するために結合され、分周器122は位相補間器121に結合され、変更可能な分周設定に基づき出力クロックを生成する。

(もっと読む)

半導体集積回路

【課題】入力された信号の位相と内部クロック信号の位相との差を所定の範囲内で吸収する能力を正確に試験することができる半導体集積回路を提供する。

【解決手段】半導体集積回路は、入力された信号の位相によって制御された位相を有する信号を生成する信号生成回路と、制御値を生成する制御値生成ブロックとを備えており、制御値生成ブロックが生成した制御値に応じて信号生成回路が生成する信号の位相を強制的にずらすことによって信号生成回路を試験する。ここで、制御値生成ブロックは、内部クロック信号に同期して動作するとともに、外部から、内部クロック信号よりも低い周波数を有する外部クロック信号に同期して目標値を受信し、受信した目標値に基づいて、内部クロック信号に同期して変化する制御値を生成する。

(もっと読む)

分周器

【課題】専用の発振器を用いないボーレート発生器のように分周する周波数の誤差を許容する分周器を簡素な構成かつ高精度で実現する。

【解決手段】分周器としてのボーレート発生器1は、所定の基準クロックRCLKを分周することにより、データをサンプリングするボーレートクロックBCLKを生成する。このボーレート発生器1は、m進/m−1進ダウンカウンタ2と、カウンタ切替制御部3とを備える。m進/m−1進ダウンカウンタ2は、異なる分周比を切り替えて基準クロックRCLKを分周する。カウンタ切替制御部3は、記ボーレートクロックBCLKの正規のボーレートクロックに対する1周期毎の誤差の累積値が所定範囲を超えると、前記累積値が減少するように、m進/m−1進ダウンカウンタ2の分周比を切り替える。

(もっと読む)

周波数変調機能付きクロック生成回路

【課題】良好なスペクトラム拡散効果を有し、ノイズの発生が少なく周辺回路や電子部品の誤動作を低減することができる周波数変調機能付きクロック生成回路を提供する。

【解決手段】クロック生成回路1は、帰還用分周器17を有し、周波数変調されたクロックを出力するPLL回路10と、帰還用分周器17から所定の周波数のみ取り出しPLL回路10に入力するバンドパスフィルタ20と、三角波を生成する三角波生成回路40とを有し、バンドパスフィルタ20は、サイン波生成器としても機能し、所定のタイミングでサイン波を生成して三角波と合成して帰還用分周器17の分周比を変化させる。

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

デジタルPLL回路

【課題】同期信号消失時の同期維持精度が向上されるとともに簡素な回路構成のデジタルPLL回路を提供することである。

【解決手段】同期信号の入力があるときの2つのクリアパルスの間に含まれる内部クロックの数の時系列的な平均値を学習値として記憶する学習値記憶回路と、PLLクロックカウンタのカウント値が学習値の整数成分と一致したとき一致検出パルスを生成する一致検出回路と、一致検出パルスを内部クロックの1周期分遅延して遅延パルスを生成するフリップフロップと、一致検出パルスまたは遅延パルスのいずれか一方を小数補正信号に従って選択し擬似同期パルスとして出力する擬似同期パルス選択回路と、補正区間において遅延パルスの数の擬似同期パルスの数に対する割合が学習値の小数成分に近似するよう選択する小数補正信号を出力する小数補正演算回路と、を有する。

(もっと読む)

フェーズロックドループ回路

【課題】入力される水平同期信号に対して、サンプリングクロックの周期の値に制約されることなく、位相誤差量を低減することができるフェーズロックドループ回路を提供する。

【解決手段】入力される水平同期信号(H-sync)は、逓倍PLL回路2から出力される、周期が等しく、1/4周期分づつずれた位相関係の4種の第1〜第4サンプリングクロックによりサンプリング回路でそれぞれサンプリングされ、各サンプリングクロックに位相同期した4種の水平同期出力データが生成され、これらはさらに加算回路6で加算されて加算水平同期出力データが生成された後、位相比較器13に入力され、分周器14で分周されたシステムクロック(第1サンプリングクロック)と位相比較される。

(もっと読む)

1 - 20 / 46

[ Back to top ]