Fターム[5J106DD43]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | ゲート回路 (250)

Fターム[5J106DD43]に分類される特許

1 - 20 / 250

PLL回路

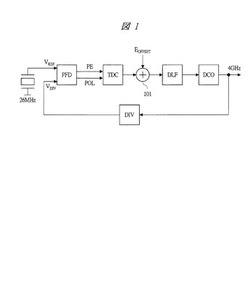

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置の内部回路に供給されるクロック信号の周波数が、正常時よりも高くなった場合の上記内部回路の暴走を回避する。

【解決手段】半導体集積回路装置(1)において、内部回路(17)と、水晶振動子を用いた発振動作によりクロック信号を形成する水晶発振回路(11)と、上記内部回路が正常に動作可能な周波数のクロック信号を形成する内蔵発振器(14)とを設ける。また上記水晶発振回路で形成されたクロック信号の周波数が、上記内部回路の正常動作の周波数範囲よりも上昇したことを検出可能な異常高速発振検出回路(13)を設ける。さらに上記異常高速発振検出回路での検出結果に基づいて、上記水晶発振回路で形成されたクロック信号に代えて、上記内蔵発振器で形成されたクロック信号を上記内部回路に供給するための制御回路(16)を設けることで、内部回路の暴走を回避する。

(もっと読む)

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

半導体装置、受信機、送信機、送受信機及び通信システム

【課題】周波数誤差に基づく送信クロックを生成し、送信データに対して任意にSSCの適用が選択可能な半導体装置が、望まれる。

【解決手段】半導体装置は、受信信号を入力し、動作クロック信号に基づいて受信信号からクロック信号とデータ信号を取り出すクロックアンドデータリカバリ部と、受信信号から取り出したクロック信号と動作クロック信号との周波数誤差信号を求める周波数誤差調整部と、周波数誤差信号を記憶する周波数誤差信号記憶部と、周波数誤差信号に基づいて動作クロック信号の周波数を制御する動作クロック生成部と、周波数誤差信号記憶部が記憶する周波数誤差信号の値に基づいて、動作クロック生成部が生成する動作クロック信号をスペクトラム拡散させて変動させるSSCG部と、を備えている。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

デジタルPLL回路、半導体集積回路装置

【課題】デジタルPLL回路の追従可能な周波数レンジを拡大する。

【解決手段】第1カウンタ(21)は、第1クロック信号をカウントして第1カウント値を出力し、第2カウンタ(22)は、第2クロック信号を分周して生成される第3クロック信号をカウントして第2カウント値を出力する。位相検出器(23)は、第1クロック信号と、第3クロック信号との位相差をデジタル値で示す出力値を出力する。位相誤差演算回路(26)は、第1カウント値と、第2カウンタ値と、出力値とに基づいて、位相誤差を演算して出力する。デジタルフィルタ回路(107)は、位相誤差を平滑化して発振周波数を示すコードを出力する。デジタル制御発振器(108)は、コードに応答して第2クロック信号を出力する。キャリブレーション制御回路(112)は、分周比と、第2クロック信号と第1クロック信号との比較結果とに基づいてデジタル制御発振器の発振周波数を調整する。

(もっと読む)

時間−デジタル変換器及びPLL回路

【課題】本発明は、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないTDCを提供することを目的とする。

【解決手段】本発明は、直列に接続され入力端で発振器が出力する出力信号CKVを入力される複数の遅延素子21と、複数の遅延素子21が出力する複数の遅延クロック信号を、PLL回路が入力される基準信号FREFのエッジタイミングでそれぞれラッチする複数のラッチ回路22と、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、複数の遅延素子21の遅延時間を調整する遅延時間調整回路32と、を備えることを特徴とするTDC2である。

(もっと読む)

遅延ロックドループを内蔵する半導体集積回路およびその動作方法

【課題】擬似ロックを防止するための論理回路の回路規模を低減する。

【解決手段】遅延ロックドループ(DLL)は、複数の可変遅延回路DL0〜8の電圧制御遅延回路1と位相周波数比較器2とチャージポンプ3を具備する。初段の出力PH[0]と最終段の出力PH[8]は、比較器2に供給される。比較器2のアップ信号とダウン信号は、チャージポンプ3に供給される。擬似ロック防止回路4は、第M段の出力PH[1]と第M+1段の出力PH[2]に応答して、可変遅延リセット信号RST_VDL_T、Bを生成する。初段の回路DL0から第M+1段の回路DL2に、クロック入力信号CLKとクロック反転入力信号がリセット信号RST_B、Tとして供給される。第M+2段の回路DL3から最終段の回路DL8に、可変遅延リセット信号RST_VDL_T、Bがリセット信号RST_B、Tとして供給される。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

情報処理システム

【課題】システムリセット時の起動時間を短縮可能な情報処理システムを提供する。

【解決手段】複数の機能モジュールの内の機能モジュール1では、システムリセット信号にてPLL回路10及び信号処理部12をリセットした後にPLL回路10へのリセットを解除する。リセット解除後にPLL回路10で生成された内部クロック信号がシステムクロック信号に位相ロックしていない場合には起動中を示す第1の起動状態信号を機能モジュール2に供給する。位相ロックしている場合には起動完了を示す第2の起動状態信号を機能モジュール2に供給すると共に信号処理部12へのリセットを解除する。機能モジュール2では、第1の起動状態信号にてPLL回路20及び信号処理部22をリセットする。そして、第2の起動状態信号にてPLL回路20へのリセットを解除し、リセット解除後に、位相ロックした時に信号処理部22へのリセットを解除する。

(もっと読む)

PLL回路

【課題】低消費電力のPLL回路を提供する。

【解決手段】位相比較回路11は、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(UP信号とDN信号)をチャージポンプ12に供給し、バイアス回路16は、チャージポンプ12にバイアス電流を供給し、制御回路17は、2種の位相差信号のうち一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、2種の位相差信号の両方が非活性化状態のときに、バイアス回路16を停止させる。

(もっと読む)

多相クロック発生回路、及び多相クロック発生方法

【課題】回路規模の増加を抑えかつ出力信号のジッタ特性を低下させずに、複数の動作周波数に対応できる多相クロック発生回路を提供する。

【解決手段】多相クロック発生回路は、位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスと、リファレンスクロック信号の周波数に基づいて、複数の遅延パスのうち、リファレンスクロック信号の周波数に対応する遅延パスを選択するスイッチ部と、スイッチ部が選択した遅延パスにより、位相差が変更された複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間回路とを備える。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

半導体装置

【課題】DLL回路がロックしないという現象の発生を防止する。

【解決手段】カウンタ回路202と、カウンタ回路202のカウント値CNTに応じた遅延量を内部クロック信号LCLKに与えるディレイライン201とを有する。まず、カウンタ回路202は第1のカウント値にセットされ、判定信号PDに基づいてそのカウント値CNTが周期的に更新される。その結果、内部クロック信号LCLKの位相が所望の位相に到達しなかった場合、カウンタ回路202は、第1のカウント値とは異なる第2のカウント値にセットされ、DLL回路200がリスタートされる。これにより、DLL回路がロックしなかった場合であっても自動的にリスタートされることから、DLL回路がロックしないという現象が防止される。

(もっと読む)

CDR回路、受信装置、および送受信システム

【課題】非線形位相比較器を用いたCDR回路、受信装置、および送受信システムの再生クロックの位相追従精度を向上させる。

【解決手段】CDR回路106、受信装置101、および送受信システム100は、受信データ105および再生クロック119が入力される非線形位相比較器の出力に、受信データに対する、再生クロックに対して位相差を有するクロックの遅れまたは進みに応じて重み付けをし、重み付けされた出力に基づいて再生クロックの位相を調整する。

(もっと読む)

位相比較回路

【課題】入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得る。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

(もっと読む)

PLL回路

【課題】 電源投入時及び基準周波数信号断から基準周波数信号入力有りの時からロックまでの時間を短くでき、ロック時の発振を安定化させ、更にロック状態から基準周波数信号断となった時にロックから制御電圧の中心付近まで早く落ち着かせることができるPLL回路を提供する。

【解決手段】 電源投入時とREF断状態からREF有りとなった場合に、積分器15内のオペアンプ39の利得を大きくし、増幅器16内のオペアンプ37の利得を大きくすることで、ロックまでの時間を短くでき、ロック時に増幅器16内のオペアンプ37の利得を小さくし、ロック状態でREF断となった場合に、積分器15内のオペアンプ39の利得を小さくしているので、自走時にコンデンサ28の電荷の放電を早めて、自走周波数に移行する時間を短くして安定化を早めることができるPLL回路である。

(もっと読む)

位相ロックループ回路

【課題】電圧制御発振回路の入力部でのリークに起因する定常位相誤差を防止できる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号とフィードバッククロック信号の位相差を検出する位相比較回路と、検出された位相差に応じた電流を第1の容量に出力するチャージポンプ回路と、第1の容量に蓄積されている電荷に基づく制御電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振回路とを有する位相ロックループ回路にて、チャージポンプ回路による第1の容量への電流の出力完了後の第1の時刻に第1の電圧を保持し、保持された第1の電圧に基づき電圧制御発振回路の入力部に流れるリーク電流に応じた電流を生成し、生成された電流に応じた補正電流をカレントミラー回路を介して第1の容量に出力するようにして、リーク電流による制御電圧の変動を抑制する。

(もっと読む)

半導体装置

【課題】DLL回路の調整を素早く完了する。

【解決手段】第1のクロック信号(図2のCLKIN)を遅延させて第2のクロック信号(図2のLCLK)を生成する遅延部(図2の33、34が相当する)と、第1のクロック信号と、第2のクロック信号をさらに遅延した信号(図2のRCLK)との位相を比較する位相比較回路(図2の36)と、遅延部の遅延量を決定するカウント値を遅延部に出力すると共に、位相比較回路の位相比較結果に応じてアップダウンするカウンタ回路(図2の37)と、初期設定動作時において、第1のクロック信号の周期を検知し、検知した周期に応じたカウント値の初期値をカウンタ回路に対して出力する初期遅延量制御回路(図2の30)と、を備える。

(もっと読む)

1 - 20 / 250

[ Back to top ]