Fターム[5J106KK37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | IC化,LSI化 (197)

Fターム[5J106KK37]に分類される特許

181 - 197 / 197

広帯域周波数を発振する装置および方法

図5に示すような、位相ロックループと可変周波数分割器(560)とを備えた、周波数を発振する装置が示されている。可変周波数分割器(560)は、第1の周波数の信号をある分割比で分割して第2の周波数(Fout)の信号を発生し、この周波数分割は、位相/周波数検出器(510)へ入力される参照周波数クロック入力(Fref)とフィードバック周波数の信号入力との比較に基づいて行われる。チャージポンプ(520)およびループフィルタ(530)が、第2の周波数の信号(355)を分割して正しいフィードバック周波数の実現を可能にする分割器(550)とともに示されている。VCO(540)には、選択されるキャパシタを備える共振回路と、動作周波数を設定する制御電圧と、適当な利得のための能動回路(320)とが内在する。  (もっと読む)

(もっと読む)

位相同期ループ回路

【課題】 ループ利得の変動を抑圧できるループ利得検出回路を備えたPLL回路を提供する。

【解決手段】 PLL回路内の電圧発振器1で駆動されるカウンタ6と、その出力を周期的に積算するアキュームレータ(ACL)と、ACLのカウント値とレジスタ9に予め設定された設計値とを比較する比較演算回路部8を設け、ACLのカウント値がループ利得と反比例することを応用してPLL回路のループ利得を検出する。検出結果に基づいてチャージポンプ電流等でループ利得の補正を行ってループ利得を校正する。これにより、PLL回路は、PLLを構成する各素子の特性のばらつきに影響しない安定したループ特性を保つことができる。

(もっと読む)

PLLクロック出力安定化回路

【課題】源振クロックで所定サイクル毎に周波数を測定することで、PLL回路が安定したことをLSI内部等で検査可能にする。

【解決手段】PLLクロック出力安定化回路は、基準クロックclkを固定又は可変の逓倍数Nで逓倍してPLLクロックpll_clkを出力するPLL回路10と、一定期間の間、前記PLLクロックpll_clkでカウントアップするカウンタ17と、カウンタ17のカウント値と固定又は可変の逓倍数Nとを比較する比較回路18と、一定期間の間、比較回路18の比較値の等しい状態が続いた回数だけカウントアップするカウンタ20と、カウンタ20のカウント値が安定待ち回数kに達したときに出力イネーブル信号enableを生成し、出力イネーブル信号enableにより、PLLクロックpll_clkを遮断していたゲート回路25を開いてPLLクロックpll_clkを通過させる出力手段とを備えている。

(もっと読む)

アナログ遅延回路の同調範囲を設定する方法及び装置

アナログ遅延線、ハイブリッド遅延線及び遅延ロック・ループ(DLL)のための装置及び方法が記述される。DLLにおいて、粗位相検知器が、粗遅延線の遅延を増すか減らすかを示す粗位相調整信号を制御する際に基準信号とフィードバック信号とを比較する。同様に、微細位相検知器が基準信号とフィードバック信号とを比較してロック・バイアス信号を生成する。この信号はアナログ微細遅延線の遅延を増減する。アナログの微細遅延線及び粗遅延線は直列に接続され、粗遅延と微細遅延とからなる全遅延を有するハイブリッド遅延線を作る。更に、微細バイアス発生器はアナログ位相発生からの初期バイアス信号又はロック・バイアス信号に応答して微細遅延を制御する。  (もっと読む)

(もっと読む)

通信用半導体集積回路

【課題】 使用周波数帯を決定するまでに要する時間が長くならないとともに回路の占有面積を小さくすることができ、また、リセット信号等の遅延により誤った周波数帯が選択されない自動バンド選択回路を備えたPLL回路を内蔵した高周波ICを提供する。

【解決手段】 VCO11の発振周波数を制御するPLLループにおいて、所定の周波数の基準信号に対する可変分周回路12の出力の位相の進みまたは遅れを判別する判別回路22と、該判別回路の出力に基づいてVCOの周波数帯を切り替える信号を生成する自動バンド選択回路20と、信号の遅延に基づく位相判別におけるずれを測定しそれを補償するような遅延を固定分周回路14で分周された信号に与える遅延補償回路25とを設け、2分探査方式でVCOの周波数帯を切り替えながら最適な周波数帯を見つけて使用周波数帯を決定するようにした。

(もっと読む)

PLL回路を内蔵する半導体集積回路

【課題】 発振回路と位相比較回路とチャージポンプ回路とループフィルタを含むPLL回路において、複数の容量素子を設けることなくつまり占有面積をそれほど増大させることなくPLLの特性を抵抗素子や容量素子の製造ばらつきに応じて調整することができ、それによってループフィルタをオンチップ化できるようにする。

【解決手段】 ループフィルタ(17)を構成する抵抗素子と容量素子を半導体チップに形成しこのうち抵抗素子は抵抗値の異なる複数の素子を設けてスイッチにより切り替えることで抵抗値を調整可能に構成し、またチャージポンプ回路(16)の電流も調整可能に構成し、抵抗素子の抵抗値の切り替えに応じてチャージポンプ回路の電流を調整するようにした。

(もっと読む)

PLL回路

【課題】 電圧電流変換回路の抵抗値のばらつきを抑えることで電圧制御発振器の発振周波数のばらつきを低減するPLL回路を提供する。

【解決手段】 可変抵抗回路4を内蔵することでプロセスばらつきを制御し、外付抵抗端子の寄生容量の影響を受けずに済み、PLLループ帯域の影響を受けない高帯域で応答可能な電圧電流変換回路が実現できる。この可変抵抗回路4にCMOS可変抵抗を用いて連続的な抵抗値調整を行う。また定電流源を用いるとより精度のよい抵抗値調整を行う事ができる。又リミット回路5を付加することで各ワースト条件に応じたロックレンジを取り出し、カレント比調整回路6を付加することでVCOリングのプロセスバラツキによる変動に応じて供給する制御電流値についてカレント比を変えることで調整し、プロセス変動によらず一定のVCOゲインを実現する。

(もっと読む)

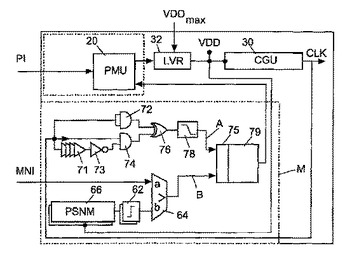

性能調整のための閉ループ制御

本発明は、監視される性能指標に応答して集積回路の性能を制御するための、方法および回路構成に関し、集積回路の電力供給は、前記性能指標に基づいて制御される。制御された電力供給の雑音レベルと前記集積回路内で発生されたクロック周波数の少なくとも一方が監視され、チェック結果が所定の範囲内にない場合、それぞれの制御信号が制御機能にフィードバックされる。それによって、プロセス変動への簡単で容易に拡張可能な自動適応が達成されることができる。  (もっと読む)

(もっと読む)

クロック同期回路におけるクロック捕捉

クロック捕捉同期回路は、まず基準クロック信号から同期クロック信号を生成し、そして同期クロック信号を捕捉し、基準クロック信号が除かれた後も同期クロック信号を出力し続ける。クロック捕捉同期回路はまた、同期クロック信号の入力依存ジッタを低減する。本発明により、基準クロック信号が除かれた後、同期クロック信号を出力し続けるクロック同期回路が提供される。また、本発明により、同期クロック出力信号の入力依存ジッタをもし除去しないとしても低減はするクロック同期回路が提供される。  (もっと読む)

(もっと読む)

温度安定化された電圧制御発振器

セルラー電話のような電池から電力を得る装置中の集積回路電圧制御発振器(VCO)は、比較的狭い制御電圧範囲を使用して非常に広い周波数範囲にわたって同調するように構成されることができる。VCOの周波数応答は、VCO共振回路の一部を形成するバラクタ310a-310bに温度可変電圧ソースを与えることにより温度補償されることができる。バラクタのレファレンス端部は、バラクタ温度依存性を実質的に補償する温度依存性を有する温度依存電圧ソース370、380により供給されることができる。温度依存電圧ソース370,380は、絶対温度比例(PTAT)装置であることができる。VCOは、基板上に製造されたCMOS発振器、基板上のLC共振タンク、および共通の陽極接続を有する少なくとも一対のバラクタ310a、310b;320a、320bを含んでいる。 (もっと読む)

スイッチトキャパシタフィルタ及びフィードバックシステム

ループフィルタ(30)は、電流信号の入力端と基準電圧との間に設けられた第1の容量素子(31)と、上記入力端と第1の容量素子(31)との間に設けられたスイッチトキャパシタ回路(32)と、第1の容量素子(31)及び前記スイッチトキャパシタ回路(32)に並列に設けられた第2の容量素子(33)とを備えている。スイッチトキャパシタ回路(32)において、第3の容量素子(321)が第1の容量素子(31)側に接続されるとき、第4の容量素子(322)は第2の容量素子(33)側に接続される。上記構成のループフィルタ(30)において、第2の容量素子(33)の容量値を、第3及び第4の容量素子(321,322)の容量値よりも大きく設定する。 (もっと読む)

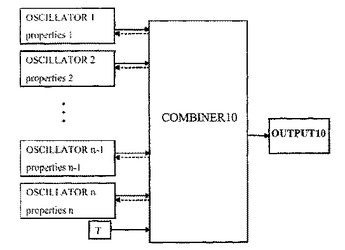

モノリシックなクロック・ジェネレータおよびタイミング/周波数リファレンス

電力節約モード、クロック・モード、リファレンス・モード、およびパルス化モードなどの複数の動作モードと共に、クロック・ジェネレータおよび/またはタイミングおよび周波数のリファレンスを提供する。共振周波数を有する第1の信号を供給するようになっている共振器と、増幅器と、温度に応じてこの共振周波数を修正するようになっている温度補償器と、製造プロセス変動に応じてこの共振周波数を修正するようになっているプロセス変動補償器とを含んでいる。さらに、実質的にこの共振周波数以下の対応する複数の周波数を有する複数の第2の信号に、この共振周波数を有する第1の信号を分周するようになっている周波数分割器と、これらの複数の第2の信号から1つの出力信号を供給するようになっている周波数セレクタとを含むことができる。  (もっと読む)

(もっと読む)

サブμ技術に適したデジタル位相同期回路

本発明は、デジタル制御発振器(4)と、位相検出器(11、12、13)と、デジタルループフィルタ(14)とを含む、デジタル位相同期回路に関するものである。上記デジタル制御発振器(4)は、出力周波数を生成するためのものである。上記の位相検出器(11、12、13)は、基準周波数と発振器(4)の出力周波数との位相差を検出するためのものであり、デルタシグマ周波数決定器(11)を含んでいる。上記デジタルループフィルタは、位相検出器の下流に接続されており、デジタル制御発振器(4)を駆動するためのものである。  (もっと読む)

(もっと読む)

基準発振器の周波数安定化

従来技術の不利な点を取り除き、特性(1)高い長期安定性、(2)低位相雑音、(3)高耐熱性、(4)その基準発振器の周波数についての正確な値、を改善したMEMS基準発振器を提供することが、本発明の目的である。  (もっと読む)

(もっと読む)

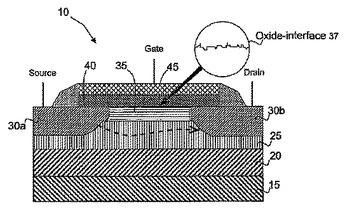

ストレインド・シリコン電圧制御発振器(VCO)

ストレインド・シリコン電圧制御発振器(VCO)は、ストレインド・シリコン層を有する第1Pチャネル金属酸化膜半導体(PMOS)装置を含み、ストレインド・シリコン層を有する第2PMOS装置に結合される。  (もっと読む)

(もっと読む)

位相スイッチングデュアルモジュラスプリスケーラ

デュアルモジュラス分周器を有する位相スイッチングデュアルモジュラスプリスケーラがもたらされる。前記分周器は第一及び第二の2分周回路(A;B)を有しており、前記第二の2分周回路(B)は、前記第一の2分周回路(A)の出力部に結合され、少なくとも前記第二の2分周回路(B)は各々90度で分離される四つの位相出力を有している。位相選択ユニット (PSU)が、第二の2分周回路(B)の四つの位相出力(Ip, In, Qp, Qn; INi, INni, INq, INnq)の一つを選択するためにもたらされる。更に、位相制御ユニットが、制御信号(C0, NC0; C1, NC1; C2, NC2)を位相選択ユニットに供給するためにもたらされ、位相選択ユニットPSUは、制御信号(C0, NC0; C1, NC1; C2, NC2)による四つの位相出力(Ip, In, Qp, Qn; INi, INni, INq, INnq)の選択を実行する。直接論理に基づく位相制御ユニット(PSU)の実現により、より高い速度が可能になり、チップ上の面積が節減される。  (もっと読む)

(もっと読む)

バイアス電流補償回路を有するタイミング発生器及び方法

カレントミラーと共に使用するための電流補償回路が開示される。カレントミラー回路は、第2カレントミラー段を駆動する第1カレントミラー段によって規定される電流経路を有し、第2カレントミラー段は、供給電圧源に結合している。電流補償回路は、供給電圧及び出力ノードに結合するインピーダンス分割器を備える。インピーダンス分割器は、供給電圧源の電圧変化を表す、ノードにおける補償信号を生成するように動作する。補償回路はさらに、出力ノードに結合する入力及び電流経路に接続される電流出力を有する利得段を含む。利得段は補償信号に応答して電流経路に印加するための補償電流を生成するように動作する。  (もっと読む)

(もっと読む)

181 - 197 / 197

[ Back to top ]