Fターム[5J106KK37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | IC化,LSI化 (197)

Fターム[5J106KK37]に分類される特許

21 - 40 / 197

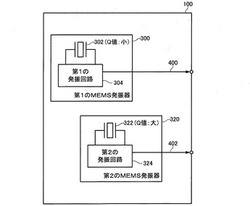

MEMSデバイス、電子機器

【課題】実装面積やコストを抑え、起動時間を短縮し、周波数精度の高いクロックも出力できるMEMSデバイス等を提供する。

【解決手段】 第1のクロック信号400と第2のクロック信号402の少なくとも一方を出力するMEMSデバイス100であって、同一の基板上に設けられた第1のMEMS共振子302を有する第1のMEMS発振器300と第2のMEMS共振子322を有する第2のMEMS発振器320とを含み、第1のMEMS発振器の共振周波数である第1の共振周波数と、第2のMEMS発振器の共振周波数である第2の共振周波数とは略一致し、第1のMEMS共振子のQ値と第2のMEMS共振子のQ値とは異なり、第1のMEMS発振器は、第1の共振周波数を周波数とする第1のクロック信号を出力し、第2のMEMS発振器は、第2の共振周波数を周波数とする第2のクロック信号を出力する。

(もっと読む)

DLL回路およびそれに使用されるレプリカ回路

【課題】 レイアウト的な制限がないDLL回路を提供すること。

【解決手段】 DLL回路に使用されるレプリカ回路は、第1の電源電圧が供給され、クロックバッファへの入力クロック信号が入力され、レプリカクロック信号を出力する遅延回路を含む。遅延回路は、第1乃至第MのCMOSインバータ回路および第(M+1)乃至第NのCMOSインバータ回路が縦続接続された回路である。複数のトランジスタは、遅延回路の後段側の第(M+1)乃至第NのCMOSインバータ回路のnチャネルMOSトランジスタのソースにそれぞれ接続されている。ローパスフィルタ回路は、第1の電源電圧と異なる第2の電源電圧を低域通過濾波して、その低域濾波した電源電圧を複数のトランジスタの制御端子へ供給する。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

クロック生成回路及びこれを備える半導体装置、並びに、クロック信号の生成方法

【課題】クロック信号の周波数に依存しないデューティ調整回路が搭載されたDLL回路を提供する。

【解決手段】内部クロック信号ICLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を指定するカウンタ回路123と、カウンタ回路123のカウント値を調整するカウンタ制御回路122と、内部クロック信号ICLKとレプリカクロック信号RepCLKのライズエッジが一致する第1及び第2のカウント値との差分を演算する減算回路133とを備え、得られた差分の1/2に相当する値に基づいて、内部クロック信号LCLKのフォールエッジを調整する。これにより、キャパシタを交互にディスチャージするタイプのデューティ調整回路を用いた場合のように、適用可能な周波数帯域が限られることがない。

(もっと読む)

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

デジタルクロック再生器

サンプリング装置(110)は、変動する周期時間を有する入力クロック信号(CLKin)を受信し、入力クロック信号(CLKin)の平均周波数より実質的に高い周波数を有するサンプリングクロック信号(CLKsmpl)に基づいて、入力クロック信号(CLKin)をサンプリングする。サンプリング装置(110)は、入力クロック信号(CLKin)の各周期に対して、各周期長値(PL)を生成する。平均化装置(120)は、いくつかの周期長値(PL)をサンプリング装置(110)から受信し、それに基づき、前記数の周期長値(PL)に等しい周期数を含む平均化期間に渡って、入力クロック信号(CLKin)に対して平均周期時間を表す平均周期長値(PLavg)を生成する。出力装置(151)は、平均周期長値(PLavg)およびサンプリングクロック信号(CLKsmpl)に基づいて、安定した出力クロック信号(CLKout)を生成する。 (もっと読む)

記憶装置およびDLL回路制御方法

【課題】セルフリフレッシュ動作後にDLL回路がロック動作を実行しない状況での記憶装置の評価を行うことが可能な記憶装置を提供する。

【解決手段】通常モードとテストモードとを有しセルフリフレッシュ動作を行う記憶装置は、DLL回路と制御部とを含む。DLL回路は、入力信号を受け付けると入力信号を遅延した遅延信号を出力し、また、入力信号と遅延信号との位相差が所定値になるように遅延信号の遅延量を設定するロック動作を行い、その後、位相差が所定値である状態を維持する。制御部は、通常モード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させ、テストモード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させない。

(もっと読む)

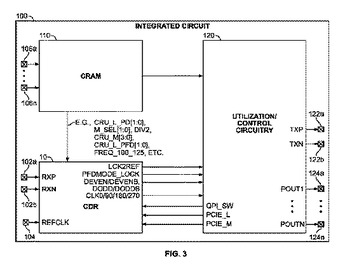

オートスピードネゴシエーションおよび他の可能な特徴を有するクロック・データ再生回路

集積回路(「IC」)は、入力データ信号からデータ情報を再生するためのクロック・データ再生(「CDR」)回路を含んでもよい。CDR回路は、参照クロックループと、データループとを含んでもよい。CDR回路によって出力される時刻変更(再生)データ信号は、その信号に含有される通信変更要求について、IC上の他の制御回路によって監視される。そのような要求に応答して、制御回路は、CDR回路の動作パラメータ(例えば、上述のループのうちのいずれか一方で使用される周波数分割ファクター)を変更することができる。これは、オートスピードネゴシエーションを採用するICサポート通信プロトコルに役立つことができる。  (もっと読む)

(もっと読む)

レジスタ制御ディレイロックループを備えた半導体デバイス

【課題】DLLクロックの無用なトグリングによる電流の消耗を低減することができるレジスタ制御ディレイロックループを備えた半導体デバイスを提供する。

【解決手段】レジスタ制御ディレイロックループから出力されたDLLクロックを用いる内部回路を備えた半導体デバイスにおいて、半導体デバイスに対する作動信号及び非作動信号に応答して、内部回路に印加されるDLLクロックをイネーブルしたりディスエーブルしたりするクロックイネーブル信号を生成する手段を備える。その場合、クロックイネーブル信号を生成する手段は、作動信号又は非作動信号に応答してプルダウン又はプルアップ動作を行う駆動手段と、半導体デバイスに対する作動信号に応答して駆動手段の出力ノードをリセットするリセット手段と、駆動手段の出力ノードに印加された信号をラッチし、バッファリングして出力する出力手段とを備えている。

(もっと読む)

ループフィルタ部品を低減するために二重経路およびデュアルバラクタを用いるタイプII位相ロックループ

【課題】フィルタ内のオンチップ部品サイズを低減するデュアルチャージポンプおよび対応する二重信号経路を有し、低減されたループフィルタ部品を備えた位相ロックループ(PLL)の提供。

【解決手段】二重経路は、電圧制御発振器内のデュアルバラクタを介して有利に結合され、ループフィルタ部品をさらに低減する。PLLは、二重経路構成を加算するために通常用いられる回路によってもたらされるノイズの欠点をなくす。

(もっと読む)

半導体装置

【課題】出力ドライバのスイング能力を変化させた場合に生じるリードデータのスキューをキャンセルする。

【解決手段】リードデータDQを外部に出力する出力ドライバ90と、出力ドライバ90のスイング能力を設定するモードレジスタ53とを備える。出力ドライバ90によって駆動されるリードデータDQの遷移開始タイミングは、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に大きく設定されている場合には相対的に早められ、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に小さく設定されている場合には相対的に遅らせる。これにより、出力ドライバ90のスイング能力に関わらず、リードデータDQがしきい値レベルを超えるタイミングを所望のタイミングに一致させることが可能となる。

(もっと読む)

周波数−電流フィードバックを有する温度安定形発振回路

フェーズロックループや低周波温度安定形発振器を必要としない信号生成回路(600)および方法が開示される。この方法は、振動出力信号の周波数を制御するフィードバック信号(608)に応じて振動出力信号(CLK1〜CLKN)を生成することと、振動出力信号の周波数に対応する大きさを有する電流出力信号を生成することと、フィードバック信号を生成するために電流出力信号を基準信号(654)と比較することとを含んでよい。信号生成回路(600)は、フィードバック信号(608)に反応する発振回路(602)と、振動出力信号の周波数に対応する周波数依存性電流信号を生成する周波数−電流変換回路(620)とを含んでよい。発振回路へ向けてフィードバック信号(608)を生成するため、フィードバック変換回路(612)は出力信号を基準信号(654)と比較する。  (もっと読む)

(もっと読む)

半導体記憶装置及び遅延時間制御方法

【課題】高速で遅延時間を行い、パフォーマンスを向上させる。

【解決手段】温度センサS1は、温度を検知し、温度情報として出力する。TAP保持回路S2は、予め使用される周波数と電圧状態とにおいて、使用温度範囲でDLL回路S4をロックさせ、その時々の温度センサS1により検知された温度に対応付けて、DLL回路S4のロック状態を初期遅延時間情報として保持する。実使用時には、DLL回路S4は、遅延時間制御開始時に温度センサS1により生成された温度に対する初期遅延時間情報をTAP保持回路S2から読み出し、そのロック情報に基づいて遅延時間を開始させる。

(もっと読む)

無線回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる無線回路、集積回路装置及び電子機器等を提供すること。

【解決手段】無線回路100は、電圧制御発振回路を有するPLL回路120を有し送信信号を生成して出力する送信信号生成回路110と、送信信号を増幅するパワーアンプ130と、周波数測定回路140とを含む。PLL回路120は、送信データ出力期間の前の期間ではクローズドループ動作に設定され、送信データ出力期間ではオープンループ動作に設定される。周波数測定回路140は、クローズドループ動作からオープンループ動作への切り換え時における送信信号の搬送波信号の周波数シフト量、及び送信データ出力期間における搬送波信号の周波数ドリフト量の少なくとも一方を測定する。

(もっと読む)

半導体集積回路

【課題】テストパターンや期待値パターンを蓄えておくメモリを半導体集積回路に増設することなく、SSCG、PLL、又は、DLL等のクロック生成モジュールの単体試験を容易に可能とする。

【解決手段】この半導体集積回路は、入力されるクロック信号に基づいて新たなクロック信号を生成して出力するモジュールと、モジュールに入力されるクロック信号に含まれているパルス数をカウントする第1のカウンタと、モジュールから出力されるクロック信号に含まれているパルス数をカウントする第2のカウンタと、第1のカウンタのカウント値と第2のカウンタのカウント値とを比較して、両者が一致するか否かを表す信号を出力するコンパレータと、コンパレータから出力される信号をサンプリングする回路とを具備する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】比較的小さな電源電圧による速度変動を高精度で抑制して比較的大きな電源電圧による速度変動を高速で抑制する。

【解決手段】半導体集積回路は、第1と第2の機能ブロックMOD00、01、クロック生成回路PLL、クロック供給回路CS0を具備する。第1と第2の機能ブロックMOD00、01には、電圧値の相違する第1と第2の電源電圧VDD00、1が供給される。MOD00は一方の電源電圧VDD01が供給可能な第1の内部回路BUF00と第1の論理回路MFF00を含み、MOD01は他方の電源電圧VDD00が供給可能な第2の内部回路BUF01と第2の論理回路MFF01を含む。クロック供給回路CS0は微調遅延段回路FC0と粗調遅延段回路CC0と位相差計測回路RSM0を含み、RSM0は第1と第2の動作クロック信号COUT00、01の位相差に応答してFC0の遅延時間TF0とCC0の遅延時間TC0を制御する。

(もっと読む)

チャージポンプ回路及びそれを用いるPLL回路

【課題】電流供給および吸入用の定電流源と、それらの定電流源の間に設けられる2つの直列に接続されたスイッチ素子から成り第1の出力端子を持つ主出力側電流路と、同様に2つのスイッチ素子から成り第2の出力端子を持つ副出力側電流路とを備え、位相比較器からの駆動信号に応答して、主出力側電流路のスイッチと副出力側電流路との各スイッチ素子が開閉し、第1の出力端子から正負の電流パルスが出力される差動スイッチング方式のチャージポンプ回路において、ダイ面積を縮小するとともに、消費電力を削減する。

【解決手段】主出力側電流路のスイッチ素子Q7,Q8間の電位と副出力側電流路のスイッチ素子Q5,Q6間の電位との差に起因して定電流源Q3,Q4の寄生容量の充放電に伴い発生する緩慢なグリッチを補償するために、コンパレータ37と、ラッチ回路38と、コンデンサC1と、充放電器Q9,Q10とを用いてグリッチ補償回路36を構成する。

(もっと読む)

遅延ロックループ回路、半導体集積回路装置

【課題】低い周波数から高い周波数までの幅広い周波数帯域に対応して、回路面積の小さい遅延ロックループ回路、その遅延ロックループ回路を搭載する半導体集積回路装置を提供する。

【解決手段】遅延ロックループ回路は、位相変更回路と、遅延線回路と、遅延制御回路とを具備する。位相変更回路は、入力される基準クロックに対して第1の位相差を有する第1の信号と、第2の位相差を有する第2の信号とを出力する。第1の位相差と第2の位相差との差分は所定の位相遅延量を示す。遅延線回路は、変更可能な単位遅延量を備える遅延回路を複数含む。遅延制御回路は、単位遅延量の合計が基準位相遅延量になるように単位遅延量を制御する。

(もっと読む)

周波数逓倍遅延ロックループ

【課題】周波数逓倍回路を提供する。

【解決手段】周波数逓倍回路(100)は、遅延ラインとクロック合成回路(TOG)を備える。遅延ラインは、その一端でリファレンスクロック(102)を受けて、一周期に一致した複数の遅延素子(101)からクロックタップ出力を発生させる。クロック合成回路(TOG)は、一対のタップ出力に応答して、各タップ出力から出力クロックパルスの立ち上がり及び立ち下がりエッジを発生させる。出力クロックの周期は入力クロックの周期よりも短い。遅延ラインは、遅延素子(101)の周期に一致するように遅延ロックループに含まれてもよい。所定数の遅延段タップ出力に接続された入力を有し、相補出力を供給する、複数の合成回路セル(TOG)が設けられる。セレクタ(106)は、位相検出器(112)からの選択制御信号に応答して、合成セルの1つに係る一対の相補出力のうちの一方から出力を選択する。

(もっと読む)

高電圧振幅状態の下での電圧制御発振器(VCO)バッファに対するデバイス信頼性の向上

電圧制御発振器(VCO)バッファのための回路が説明される。回路は、VCOコアと接続されるVCOバッファの入力と接続された第1のキャパシタを含む。回路は、また、VCOバッファの入力と、p型金属酸化膜半導体電界効果(PMOS)トランジスタのゲートとに接続された第2のキャパシタを含む。回路は、さらに、第1のキャパシタと、PMOSトランジスタのゲートとに接続された第1のスイッチを含む。回路は、また、VCOバッファの入力と接続された第3のキャパシタを含む。回路は、さらに、VCOバッファの入力と、n型金属酸化膜半導体電界効果(NMOS)トランジスタのゲートとに接続された第4のキャパシタを含む。回路は、また、第3のキャパシタとNMOSトランジスタのゲートとに接続された第2のスイッチを含む。 (もっと読む)

21 - 40 / 197

[ Back to top ]