Fターム[5J106KK37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | IC化,LSI化 (197)

Fターム[5J106KK37]に分類される特許

161 - 180 / 197

位相同期ループ回路のロック検出のためのシステム及び方法

【課題】位相同期ループ回路のロックを検出するためのシステム及び方法。特に、PLLロック検出された出力をアサートする前のユーザー定義の期間に対するPLLの安定性を検出するために構成されたロック検出器。

【解決手段】安定性は、PLL回路に挿入され位相−周波数検出器とチャージポンプとの間に配置されたカウンタにより示されることができる。カウンタ値は位相−周波数検出器により作動されるので、PLLロックはカウンタ値の安定性により示される。デジタルカウンタ値は、デジタルチャージポンプとロック検出回路に同時に供給されることができる。ロック検出器は、いつカウンタ値間の差がユーザー定義の許容値未満になるかを判定するためにレジスタと差検出器を含む。ロック検出器は、カウンタ値がカウンタ値の変動周波数と同じ周波数でサンプリングされる場合に生じる可能性があるロックの誤表示を避けるために、可変タイマーを含むことができる。

(もっと読む)

局部発振回路、携帯情報端末および局部発振制御方法

【課題】 TDMA/TDDのスロット可変型通信における周波数の変動を防止する。

【解決手段】 2系統のPLL回路をそれぞれ有する第1の集積回路(40a)および第2の集積回路(40b)と、基準発振回路(30)と、2系統の周波数帯域の信号を出力する出力回路(50,60)とを備える。互いに同一系統となる2つの第1PLL回路(70A,70B)は、該各PLL回路をフレーム期間中の異なるタイムスロットにて動作させるための制御信号が供給される信号線(70AC,70BC)と出力回路とに接続される。第1の集積回路の第2PLL回路(80A)は、該PLL回路を上記タイムスロットの双方にて動作させるための制御信号が供給される信号線(80AC)と出力回路とに接続される。第2の集積回路の第2PLL回路(80B)は、出力回路には接続されず、第1の集積回路のPLL回路が接続された信号線(70AC,80AC)のうちのいずれかと接続される。

(もっと読む)

位相同期ループ回路、オフセットPLL送信機、通信用高周波集積回路及び無線通信システム

【課題】ループ利得の変動を抑圧できるループ利得検出回路を備えたPLL回路を提供する。

【解決手段】ループ利得検出にあたっては、まず、位相比較器101の第2の入力(IN−2)への入力信号の周波数を変化させ、その変化に対する応答を電圧制御型発信器102の出力で検出する。検出手段としては、電圧制御型発信器102の出力にカウンタ103を接続し、そのカウンタ103の出力に積分器104を接続することで行う。この検出結果をチャージポンプ105の電流値にフィードバックすることで、位相同期ループ特性を最適化する。

(もっと読む)

無線基地局

【課題】 無線回路の部品コストを安価にし、回路設計および設計検証に掛かる時間を削減した無線基地局を得る。

【解決手段】 無線基地局は、送信信号をデジタルからアナログに変換するDA変換器と、送信信号を増幅する増幅回路と、所定の周波数で発振するPLL回路と、前記PLL回路を用いて送信信号を無線周波数にアップコンバージョンする周波数変換部とを備え、少なくとも前記増幅回路、PLL回路および周波数変換部を1つの集積回路に集積している。こうした構成により、部品コストを安価にでき、回路設計および設計検証に掛かる時間を削減できる。

(もっと読む)

位相ロックループ回路装置及びこれを利用したクロック信号発生方法

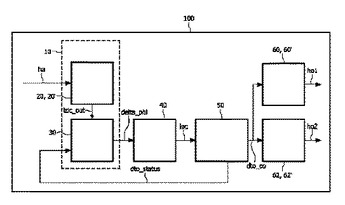

回路装置(100)、特にサブクロックまたはサブピクセルの正確な位相測定及び位相発生用の位相ロックループ、並びにこれに対応する方法を、クロック乗算器位相ロックループを時間−ディジタル変換器の後方に設けず、アナログ遅延線も信号除算器ユニットも、ディジタルランプ発振器または離散時間発振器とディジタル−時間変換器との間に設けず、ディジタル環境におけるノイズ及び接地バウンスの影響を受け易いアナログ回路がより少ない方法でさらに発展させるために、少なくとも1つの位相測定ユニット(10);少なくとも1つの位相検出器ユニット(30)の少なくとも1つの出力信号(delta_phi)を供給される少なくとも1つのループフィルタユニット(40, 40’);ループフィルタユニット(40, 40’)少なくとも1つの出力信号、特に少なくとも1つの増分(inc)を供給される少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)を設け、ディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つのレジスタユニット(54, 54’)の状態信号(dto_status)は位相検出器ユニット(30)に入力信号として供給され、さらに、少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つの出力信号(dto_co)を供給されて少なくとも1つの出力信号(ho1, ho2)発生する少なくとも1つのディジタル−時間変換器ユニット(60, 62, 60’, 62’)を設けることを提案する。  (もっと読む)

(もっと読む)

検出回路及び半導体装置

【課題】

簡易な回路構成により、外部クロックの停止を効率よく検出できる検出回路及び半導体装置を提供すること。

【解決手段】

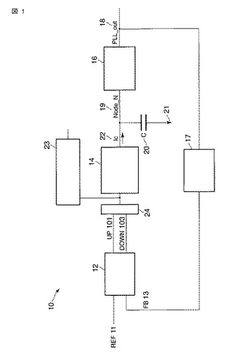

本発明にかかる半導体装置は、発振クロックを逓倍したPLL出力クロックを生成するPLL回路11と、PLL出力クロックに基づいて動作する内部回路13と、発振クロックとPLL出力クロックに基づいて発振クロックの停止を検出し、検出した結果を内部回路13へ出力する発振停止検出回路12と、を有するものである。

(もっと読む)

通信用半導体集積回路

【課題】所定の周波数の局部発振信号を発生する発振器を含むPLL回路を内蔵し、温度が変化してVCOの発振周波数が変動してもPLLループのロックがはずれにくい高周波ICを提供する。

【解決手段】発振周波数帯を切り替え可能なVCO11と可変分周回路12と位相比較回路15とループフィルタ17とを含み、ループフィルタとVCOとの間を切り離した開ループ状態で、複数の所定の固定電圧のいずれかをVCOへ印加する切替えスイッチと、所定の周波数の基準信号に対する可変分周回路の出力の位相の進みまたは遅れを判別する判別回路22と、判別回路の出力に基づいてVCOの周波数帯を切り替える信号を生成する自動バンド切り替え回路23とを設け、2分探査方式でVCOの周波数帯を切り替えながら最適な周波数帯を見つけ、さらにVCOへ印加する固定電圧を2分探査方式で切り替え最適な印加電圧を見つけPLLループをロックさせる。

(もっと読む)

PLL回路を内蔵する通信用半導体集積回路

【課題】 オフセットPLL方式の送信回路を有する高周波ICにおいて、中間周波数の信号を生成するIFVCOが不要であるとともに、フラクショナルPLLのような複雑な分周制御回路を必要とせずに所望の周波数帯の送受信信号の変復調を行なうことができ、それによってチップサイズを低減させることが可能な回路技術を提供する。

【解決手段】 送信回路と受信回路に共通のローカル発振信号を生成するRFVCOを含むRF−PLL(263)に、基準となる発振信号を分周する分周回路(266)と自らの発振信号を分周してフィードバックする分周回路(267)としてそれぞれ整数で表わされる分周比で分周可能な可変分周回路を設けるとともに、上記RF−PLLで生成されたローカル発振信号を分周して送信回路で必要な中間周波数の信号を生成する分周回路(231)を設け、上記可変分周回路の分周比をそれぞれ送信周波数または受信周波数に応じて適宜切り替えるようにした。

(もっと読む)

PLL回路およびそれを用いた無線通信端末機器

【課題】PLL帯域を広げることなくセットリング時間を短縮し、かつ、IC化に適したPLL回路を提供する。

【解決手段】PLL回路の位相比較器1を電流出力型とし、セットリング時間を短縮するために、電流出力型位相比較器1の出力端に定電流源2を接続する。また、PLLのリセット用スイッチ3を電流出力型位相比較器1の出力端に接続する。セットリング時間を短縮するために、PLL帯域を広げる必要がなく、雑音を低減できる。また、リセット用スイッチおよびセットリング時間短縮用の定電流源のIC化が可能となる。

(もっと読む)

PLL回路

【課題】 回路規模の増大を抑制しつつ、PLL回路の電磁輻射ノイズを低減させる。

【解決手段】 PLL回路2を半導体チップ1に形成するとともに、PLL回路2にリファレンスクロックSaを入力するリファレンスクロック入力端子3a、PLL回路2の周波数制御に用いられる制御電圧Sbが入力される制御電圧入力端子3bおよびPLL回路2にて生成されたクロック信号Scを出力するクロック出力端子3cを配置し、制御電圧入力端子3bとリファレンスクロック入力端子3aとの間隔Aは、リファレンスクロックSaによって制御電圧Sbのレベル変動Bが発生するように設定し、制御電圧Sbのレベル変動Bに対応してクロック信号Scのクロック発振周波数を所定の周期で変調させる。

(もっと読む)

電圧制御発振回路、およびその調整方法

【課題】 簡易な回路構成により、構成素子の特性の製造バラツキにかかわらず、出力特性のバラツキを抑制する調整が可能な、電圧制御発振回路、およびその調整方法を提供すること。

【解決手段】 低域通過フィルタ15、高域通過フィルタ16は、電圧制御発振回路11を構成する素子と同一構造の素子で構成され、所定の相関関係が形成される。補正素子14は、電圧制御発振回路11において発振周波数制御信号VTが入力される主素子と並列に接続される。目標ゲイン値TGにおいて、低域通過フィルタ15と高域通過フィルタ16との周波数−ゲイン特性は互いに逆の傾きを有して交差する。容量値が低くばらつく場合、基準周波数fREFにおいて、出力信号SL2がSH2よりも出力レベルが大きくなり、出力レベル差LD2が発生し、LD2に応じた調整信号VCNT2が出力され、発振周波数fVCOが低くされる。

(もっと読む)

クロック信号調整回路

【課題】 本発明は、LSI等の集積回路に組み込まれた回路にクロック信号を分配するためのクロック分配回路に関し、特にクロック信号の位相差調整を自動的に行うクロック調整回路を提供するものである。

【解決手段】 本発明は、LSIチップに構築された回路素子を駆動する際、駆動の基準となるクロック信号の供給を第1分配から順次階層状に下層に分配し、例えば第5分配「5」からLSIチップの各エリアに供給する回路であり、その際クロック信号の遅延を位相差検出回路によって検出し、その検出結果に基づいて各第5分配「5」に内装された遅延調整回路に遅延情報として自動的に書き込み、以後当該遅延情報を使用してLSIチップが実装された際のクロック信号の位相差を調整する。

(もっと読む)

チャージポンプ回路及びその半導体集積装置

【課題】チャージポンプ回路をより高い周波数で動作できるようにすることである。

【解決手段】UP信号がローレベルのとき、pチャネルMOSトランジスタTR1のゲートに、VDD−Vth<Pb<VDDの条件を満たすバイアス電圧Pbを供給し、DOWN信号がローレベルのとき、nチャネルMOSトランジスタTR2のゲートに、GND<Nb<Vthの条件を満たすバイアス電圧Nbを供給する。これにより、pチャネルMOSトランジスタTR1とnチャネルMOSトランジスタTR2がオン状態になるまでの遅延時間を短くすることができる。

(もっと読む)

位相同期回路

【課題】位相同期回路のループバンド幅を最適制御する。

【解決手段】位相同期回路は、電圧制御発振器40のゲインを設定するゲイン設定回路60と、チャージポンプ回路20の電流の大きさ及びループフィルタ30の容量値から決定される時定数を設定する時定数設定回路70とを備えている。位相同期回路のループバンド幅は、ゲイン設定回路60がゲインを所定値に設定し、時定数設定回路70が時定数を所定値に設定することによって、所望値に設定される。

(もっと読む)

周波数シンセサイザ

【課題】 VCOのF−V特性が温度や製造プロセスのばらつきにより変動した場合にも所望の周波数で発振できるようにVCOの制御電圧を適切な値に制御する。

【解決手段】 参照周波数Frefを有する参照信号と第1の周波数を有する第1の信号とを与えられて位相を比較し、この位相比較結果に基づいた制御電圧をVCO21の入力端子に与えて発振周波数を有する第2の信号を生成して出力端子から出力し、この第2の信号をデバイダ15に与えて分周して第1の信号を出力する位相同期ループ回路PLL11と、制御信号を生成してVCO21に与える制御部CT21とを備え、VCO21は、入力端子と出力端子との間にコイル及び可変容量が並列に接続され、さらに入力端子と出力端子との間に可変容量に並列に、複数の容量をスイッチにより選択的に接続する構成を有し、このスイッチは制御信号によりオン/オフが制御される。

(もっと読む)

ロッキング速度が向上した内部クロック発生回路とこれに含まれるアナログシンクロナスミラーディレイ

【課題】外部クロック信号に対する内部クロック信号のロッキング所要時間を短縮させる内部クロック発生回路と、動作領域の幅が広くて、クロック信号の周波数変化に対処可能なアナログシンクロナスミラーディレイを提供する。

【解決手段】内部クロック発生回路は、第1遅延ミラー、巨視ロッキングブロック、電圧制御遅延ブロック、第2遅延ミラー、および微細ロッキングブロックを含む。第1遅延ミラーは、所定のバッファリングクロック信号を所定の第1ミラーリング遅延時間だけ遅延して遅延クロック信号として提供するために駆動し、第1ミラーリング遅延時間は、所定の第1〜第3遅延時間の和と同一であり、バッファリングクロック信号は、外部クロック信号に対して第1送信遅延時間で同期し、巨視ロッキングブロックは、前記バッファリングクロック信号と遅延クロック信号を用いて、所定のアナログ同期クロック信号を提供する。

(もっと読む)

位相同期ループ及び遅延同期ループ

【課題】位相及び遅延同期ループとこれを備えた半導体メモリ装置を提供する。

【解決手段】この回路は、入力クロック信号と出力クロック信号との位相差を検出してアップ信号及びダウン信号を発生する位相差検出器、アップ信号に応答して供給電流を供給して制御信号のレベルを上昇させ、ダウン信号に応答して放電電流を流れるようにして制御信号のレベルを下降させ、ロック状態の後に第1制御電圧に応答して供給電流を補償し、第2制御電圧に応答して放電電流を補償して前記制御信号を出力する電荷ポンプ、ロック状態後にアップ信号とダウン信号とのレベル差に対応する第1制御電圧及び第2制御電圧を発生する補償部、及び、制御信号に応答して出力クロック信号の位相を変更する電圧制御発振器で構成されている。従って、ロック状態後に電荷ポンプの供給電流源と放電電流源との電流量の不一致を補償することによって入力クロック信号と出力クロック信号間の位相差が補償でき、これによりアップ信号とダウン信号間の位相差も補償できる。

(もっと読む)

半導体集積回路

【課題】 外部クロックが停止されてもオンチップのPLL回路を用いて内部クロックを生成する。

【解決手段】 PLL回路(2)は、参照クロック信号の位相と帰還クロック信号の位相とを比較するための位相比較回路(10)と、参照クロック信号の周波数と前記位相比較回路での位相比較結果とに応じた発振制御信号を生成するチャージポンプ回路(11)と、発振制御信号に加算されるバイアス信号を生成するバイアス回路(15)と、発振制御信号とバイアス信号に応じた周波数のクロック信号を形成する発振回路(16)とを有する。外部クロックが停止されてもPLL回路のバイアス回路で生成されるバイアス信号に応じた周波数のクロック信号を形成することができる。必要な周波数はバイアス信号によって決定することができるから、外部から供給されるクロックが停止されたときの生成されるクロック信号の周波数に大きなばらつきを生じ難い。

(もっと読む)

周波数ロック検出器

【課題】 1つのカウンタとクロック個数差検出部とを利用して、位相が同期されない2クロック信号の周波数を比較して、周波数ロックを判別(所望の周波数精度内にあるか否かを判別)することにより、集積化が容易な周波数ロック検出器を提供すること。

【解決手段】 本発明は、周波数ロック検出器において、外部から基準クロック信号を受け取って、基準クロック信号のクロック個数をカウントするためのカウンタと、前記外部から受け取った基準クロック信号と、前記基準クロック信号と互いに位相が同期されない復元されたクロック信号とのクロック個数の差を検出するためのクロック個数差検出部と、前記カウンタと前記クロック個数差検出部の結果値とを利用して、周波数ロックを判別するためのロック判別部とを備える。

(もっと読む)

周波数合成の方法と装置

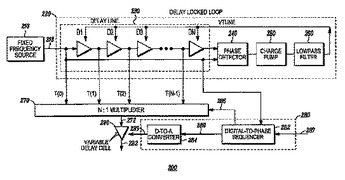

DPC(200)であって、周波数源(20)と、クロック信号を受信し複数の位相シフトされたクロック信号を生成する遅延ロックループ(220)と、合成信号の所望の周波数を識別する入力信号を受信する為の、DPS(282)とDAC(284)とを有した制御装置(280)と、複数の位相シフトされたクロック信号を受信し、位相シフトされたクロック信号の1シーケンスを選択し、粗い合成信号を出力する選択回路(270)と、可変遅延セル(290)とがあるDPC(200)であり、可変遅延セル(290)が、粗い合成信号を修正して、周波数が実質的には所望の周波数である合成信号(292)を生成する為に、粗い合成信号を受信するべく選択回路に結合された第1の入力と、微同調調整信号を受信する為に制御装置に結合された第2の入力とを有している。DPCには更に、DPCを較正するトレーニング装置がある。  (もっと読む)

(もっと読む)

161 - 180 / 197

[ Back to top ]