Fターム[5J106KK37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | IC化,LSI化 (197)

Fターム[5J106KK37]に分類される特許

61 - 80 / 197

半導体集積回路及びその制御方法

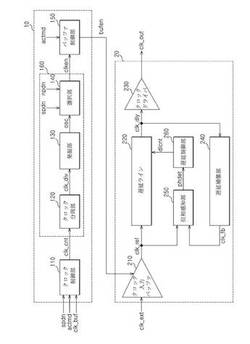

【課題】本発明は、安定ているクロックを生成するために、DLL回路のスマートパワーダウンモードを具現する半導体集積回路及びその制御方法を提供する。

【解決手段】本発明の半導体集積回路は、スマートパワーダウン信号がイネーブルされると、周期的にイネーブルされるパルス信号であるバッファイネーブル信号を生成するDLL制御手段;及び、バッファイネーブル信号に応じて外部クロックの位相を制御して、出力クロックを生成するDLL回路を含む。

(もっと読む)

半導体集積回路

【課題】入力された信号の位相と内部クロック信号の位相との差を所定の範囲内で吸収する能力を正確に試験することができる半導体集積回路を提供する。

【解決手段】半導体集積回路は、入力された信号の位相によって制御された位相を有する信号を生成する信号生成回路と、制御値を生成する制御値生成ブロックとを備えており、制御値生成ブロックが生成した制御値に応じて信号生成回路が生成する信号の位相を強制的にずらすことによって信号生成回路を試験する。ここで、制御値生成ブロックは、内部クロック信号に同期して動作するとともに、外部から、内部クロック信号よりも低い周波数を有する外部クロック信号に同期して目標値を受信し、受信した目標値に基づいて、内部クロック信号に同期して変化する制御値を生成する。

(もっと読む)

クロック・データ・リカバリ回路

【課題】

USB2.0規格などの高速シリアル通信に用いるクロック・データ・リカバリ回路に関し、受信データの取り込みエラーを防止し、かつLSI化に適した回路を提供する。

【解決手段】

周期T1のクロックをN分割したT2単位でずらしたN相のクロックを出力する手段6、シリアル転送された信号をT2毎にサンプリングしてT1毎にNビットパラレルデータに変換する手段4、その出力データをデジタル処理してNビットパラレルデータに変換する手段で、またデータ変化点を示すNビットパラレルデータに変換する手段8、変化点を示すデータを位相情報入力として前記デジタル処理されたデータのデータ変化点の略中間位置を示すデータを出力する手段10、その出力データが示したビット位置に対応する前記デジタル処理されたデータを復元データとする手段12を備える。前記デジタル処理は、移動平均処理、デューティずれ補正処理とすることができる。

(もっと読む)

グローバルPLLベース・タイミング・リカバリ・ループの遅延補償方法及びシステム

【課題】 グローバルPLLベース・タイミング・リカバリ・ループの遅延補償方法及びシステムを提供する。

【解決手段】 一実施形態のシステムは、個々のチャネルに関連する誤差信号をそれぞれ受け取る複数の入力を備えたグローバルPLL回路と、前記グローバルPLL回路と結合された遅延補償回路と、を含む。一実施形態の方法は、個々のチャネルにそれぞれ関連する複数の誤差信号を受け取るステップと、前記誤差信号に1つ又は複数の遅延補償信号を適用するステップと、前記チャネルのそれぞれに関する位相誤差出力信号を出力するステップと、を含む。

(もっと読む)

適応ループ帯域を有する位相同期ループ

【課題】向上されたループ安定度とより早いロッキング率を有する適応的位相同期ループを含む半導体装置を公開する。

【解決手段】本発明の実施形態では、ループの安定度のために第2電荷ポンプを用いない方法として具現されていて、結果的に、本発明の位相同期ループはより小さいチップダイ(chip die)面積を占める。本発明の他の実施形態では、複数の電荷ポンプが用いられて、従来技術に比べてより向上されたロッキング(locking)応答時間を得ることができる。

(もっと読む)

ディジタル位相検出器およびPLL

【課題】従来のディジタル位相検出器は、遅延素子としてインバータ等の遅延時間を使用しているが、遅延素子の配置および配線の固定が必要であることからゲート・アレイやFPGA等ではインプリメントすることが難しい。遅延素子の遅延時間はデバイスの種類やプロセスばらつきにより変動するため位相検出の精度に影響が出る。

【解決手段】2つのクロックが整数比に近い周波数を有している場合において、第1のクロックを入力とするM/N逓倍する逓倍器と、逓倍器の出力クロックを用いて第2のクロックをラッチするF/Fと、F/Fの出力を微分する微分回路と、逓倍器の出力クロックを入力とするカウンタと、微分回路の出力に応じて前記カウンタの出力を保持するラッチ回路と、ラッチ回路の出力を加算する第1の加算器と、第1の加算器の出力を固定値から減算する第2の加算器と、第2の加算器の出力を順次積算する積算器と、を備えるよう構成する。

(もっと読む)

VCOのキャパシタバンクのトリミングとキャリブレーション

技法は、電圧制御発振器(VCO)で使用されるキャパシタバンクに関連するキャパシタンスをトリミングするために開示される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。構成要素のキャパシタンスは、キャパシタバンクのステップのサイズをトリミングするために選択的にイネーブルされ、またはディスイネーブルされ得る。さらなる技法は、キャパシタバンクについてステップのサイズの誤差を最小化するためにトリミング可能なキャパシタンスをキャリブレートするために開示される。  (もっと読む)

(もっと読む)

チャージポンプ回路およびPLL回路

【課題】 広い範囲にわたって良好な特性のチャージポンプ電流の得られるチャージポンプ回路を提供する。

【解決手段】 第1のチャージポンプ部14Aに、定電流源Q1から出力される定電流を、スイッチ回路SW1、SW2の直列回路と、スイッチ回路SW3、SW4の直列回路とに振り分ける制御信号が供給する。残るチャージポンプ部14B、14Cには、定電流源Q1から出力される定電流を、スイッチ回路SW1、SW2の直列回路と、スイッチ回路SW3、SW4の直列回路とに振り分ける制御信号と、スイッチ回路SW1〜SW4をオフにする電位とが、スイッチ回路SWA〜SWDを通じて供給される。必要とするチャージポンプ電流に大きさに対応して、スイッチ回路SW11BA〜SW14Cを制御するとともに、定電流源Q1、Q2の出力電流の大きさを変更することにより、出力端子T3に、必要とする大きさのチャージポンプ電流を得る。

(もっと読む)

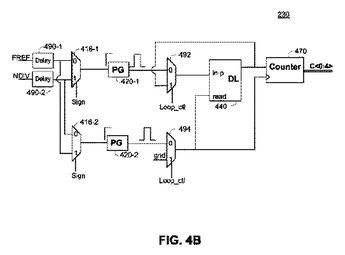

完全デジタル位相ロックループにおける位相デジタル変換器

位相デジタル変換器と、完全デジタル位相ロックループと、完全デジタル位相ロックループを有する装置とについて、本明細書で説明する。位相デジタル変換器は、時間デジタル変換器を駆動する位相周波数変換器を含む。時間デジタル変換器は、位相周波数変換器によって出力された位相差の絶対値と符号とを判断する。時間デジタル変換器は、タップ付き遅延線とループフィードバックカウンタとを利用して、ループ追跡プロセスによくある小さいタイミング差およびループ収集プロセスによくある大きいタイミング差の測定を可能にする。タップ付き遅延線は、基準期間の部分の測定を可能にし、基準クロックの速度に関する要件を低減することによって位相デジタル変換器のより低電力の動作を可能にする。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】動作モードによって周波数変調を行うか行わないかを選択することによって受信側の負荷を低減することができる半導体集積回路を提供すること。

【解決手段】半導体集積回路1は、2以上の内部回路(ビデオデコーダ11、CPU12など)と、所定の周波数のクロックを発生するPLL31と、周波数を変調させたクロックを発生するSSCG PLL32と、内部回路にPLL31からのクロックか、SSCG PLL32からのクロックのいずれかを選択して内部回路に入力するセレクタ21とを有する。

(もっと読む)

原子共振器を使用した周波数発生のためのデバイス、システム、および方法

固体原子クロックは、周波数標準を生成するために、超微細共振を示すことが可能な量子状態を利用する可能性がある。出力信号を生成するために自由走行発振器を超微細共振周波数に結合することが可能なデバイスが本明細書で述べられる。本発明のある態様では、原子クロックは、シリコン基材上で作製されてもよく、また、電子集積回路の一部として、チップスケールで集積化されてもよい。固体原子クロックを利用した動作原理、作製方法、およびシステムもまた開示される。 (もっと読む)

PLL回路

【課題】 高い線形性をもった電圧―電流特性を備え、ゲイン変動を抑えた電圧電流変換回路を有するPLL回路を提供する。

【解決手段】 電圧電流変換回路11は、制御電圧VCを受けるNチャネルMOSトランジスタN1と、NMOSトランジスタN1と直列に接続されたPチャネルMOSトランジスタP1と、PMOSトランジスタP1とミラー回路を構成するPMOSトランジスタP2と、PMOSトランジスタP1と並列に接続された電流源13を備える。PMOSトランジスタP2から出力される制御電流Ioutは、NMOSトランジスタN1に流れる電流から電流源13によって供給される電流の分だけ差し引かれる。

(もっと読む)

半導体素子、クロック同期化回路、及び、クロック同期化回路の駆動方法

【課題】クロック同期化回路は、インジェクションロッキング方式を使用してジッタピーキング現象と制御電圧にパターンジッタが大きくなる現象なく、所望の位相・周波数ロッキング動作を行う。

【解決手段】クロック同期化回路は、基準クロック信号とフィードバックされるフィードバッククロック信号の位相・周波数差を検出信号として出力する位相・周波数検出手段332と、検出信号に応答してチャージポンプ動作を行うチャージポンプ手段334と、チャージポンプ動作に応答して発振制御電圧を生成する制御電圧生成手段336と、発振制御電圧に対応してフィードバッククロック信号を生成する電圧制御発振手段338と、発振制御電圧に応答して自由発振周波数が設定され、基準クロック信号に同期化した内部クロック信号を生成するインジェクションロッキング発振手段310とを具備する。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を遅延して第2のクロック信号を生成するディジタル型の遅延線路と、ディジタル型の遅延線路の遅延時間長を、各段のフリップフロップ出力により設定するリング型シフトレジスタと、第1のクロック信号と前記第2のクロック信号の位相関係に基づいて、リング型シフトレジスタに対するシフトクロックの供給を制御する遅延量制御部とで構成する。

(もっと読む)

半導体集積回路

【課題】マルチバンド無線通信のための複数のミキサーに複数のローカル信号を供給するための複数の分周器の入力を電圧制御発振器の発振出力信号により効率的に駆動すること。

【解決手段】半導体集積回路は、第1と第2と第3のミキサー(25、26、28)と、電圧制御発振器(VCO)16と、第1と第2と第3の分周器(11、12、14)と、信号配線とを具備する。第1分周器11と第3分周器14の第1分周数は、第2分周器12の第2分周数よりも小さな値に設定されている。第1と第2と第3の分周器(11、12、14)の分周出力信号は、第1と第2と第3のミキサー(25、26、28)に供給される。信号配線の略中央にVCO16と第2分周器12とが接続され、信号配線の一端と他端とには第1分周器11と第3分周器14とがそれぞれ接続される。第1分周器と第3分周器の入力に、第1と第2のバッファ電圧増幅器BUFがそれぞれ接続される。

(もっと読む)

半導体装置

【課題】発振信号を出力し、かつ低消費電力化を図ることが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1の制御電圧に応じた周波数で発振することにより発振信号を出力する電圧制御発振回路5と、電圧制御発振回路5から受けた発振信号の周波数を電圧に変換する周波数/電圧変換回路2と、周波数/電圧変換回路2によって変換された電圧と前回生成した第2の制御電圧との間のレベルを有する新たな第2の制御電圧を生成する制御電圧生成回路11と、第2の制御電圧を積分することにより第1の制御電圧を生成し、第1の制御電圧を電圧制御発振回路5へ出力するアナログ積分回路3とを備える。

(もっと読む)

DLL回路及びこれを備える半導体装置、並びに、データ処理システム

【課題】クロックの周波数が高い場合であっても、パルスの消失リスクが少ないDLL回路を提供すること。

【解決手段】DLL回路100において、CKとLCLKの各立ち上がりエッジの位相を比較して判定信号R−U/Dを生成する位相判定回路111と、CKとLCLKの各立ち下がりエッジの位相を比較して判定信号F−U/Dを生成する位相判定回路112と、判定信号R−U/Dに基づいてLCLKRのアクティブエッジの位置を調整する第1の調整回路と、判定信号F−U/Dに基づいてLCLKFのアクティブエッジの位置を調整する第2の調整回路と、LCLKRとLCLKFに基づいてLCLKを生成するクロック生成回路と、LCLKRのアクティブエッジの調整方向とLCLKFのアクティブエッジの調整方向とが互いに逆方向であることに応答して、第2の調整回路による調整動作を停止させる停止回路150とを備える。

(もっと読む)

タイミング調整装置

【課題】温度変化に起因したタイミングのずれによるデータ不一致の発生を抑制

【解決手段】高速揮発性メモリ3にデータを書き込む場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、書き込み用DLL14に対してレジスタ設定を行う。これにより、書き込み用DLL14に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、書き込み用DLL14から出力される。また、高速揮発性メモリ3からデータを読み出す場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、読み出し用DLL11に対してレジスタ設定を行う。これにより、読み出し用DLL11に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、読み出し用DLL11から出力される。

(もっと読む)

PLLシンセサイザー回路

【課題】 電源変動等が生じると、外部からの割込信号により不定期間を待って再度分周データをPLLシンセサイザーICに書き込むことで、安定的にロック状態に復帰させることができるPLLシンセサイザー回路を提供する。

【解決手段】 PLLシンセサイザーIC106の電源投入時又は電源変動時にマイクロプロセッサ(CPU)104への割込を監視手段が発生させ、CPU104はPLLシンセサイザーIC106の電源投入後又は電源変動後の不定期間に相当する期間を待って、分周データをPLLシンセサイザーIC106に出力して書き込みを行い、更に分周データ出力後にロック状態となるまでの期間ウエイトするPLLシンセサイザー回路である。

(もっと読む)

発振回路

【課題】高精度な発振回路を提供する。

【解決手段】例えば、奇数段のインバータ回路IVを含んだ複数のリングオシレータ部RO1,RO2と、このRO1,RO2の出力ノードRO_O1,RO_O2の信号を加算する加算部ADDを設ける。そして、このADDの加算結果をクロック信号として出力ノードOSC_Oから出力すると共に、この出力ノードOSC_OをRO1,RO2の入力ノードRO_I1,RO_I2に帰還する。これによって、例えばRO1,RO2の遅延時間がそれぞれ標準偏差σの正規分布に基づいてばらつく場合に、OSC_Oから得られるクロック信号のばらつきをσ/√2とすることが可能となる。

(もっと読む)

61 - 80 / 197

[ Back to top ]