Fターム[5J106KK37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | IC化,LSI化 (197)

Fターム[5J106KK37]に分類される特許

101 - 120 / 197

位相差検出回路、PLL回路、位相差検出方法及び位相差検出プログラム

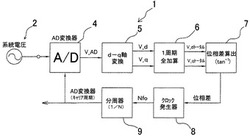

【課題】 ゼロクロスポイント検出用のハードを用いることなく、位相差の検出機能を実現する。

【解決手段】 位相差検出回路は、検出信号と内部基準信号の位相差を検出するための回路であって、d−q軸変換ユニット5と、1周期全加算ユニット6と、位相差算出ユニット7とを備えている。d−q軸変換ユニット5は、内部基準信号を用いて検出信号をd−q軸変換することで、瞬時値有効分dと瞬時値無効分qとを算出する。1周期全加算ユニット6は、瞬時値有効分dを1周期全加算することで有効分Dを算出して、さらに瞬時値無効分qを1周期全加算することで無効分Qを算出する。位相差算出ユニット7は、有効分Dと無効分Qを用いて位相差を算出する。

(もっと読む)

PLL回路及びディスク装置

【課題】温度特性や経時変化がなく、線速度変化に合わせてループ特性をシームレスに補正できるPLL回路を提供する。

【解決手段】デジタルループフィルタ103は、位相比較器102が出力する位相誤差を入力し、デジタル周波数値を生成する。このデジタル周波数値は、D/A変換器104でアナログ電圧に変換され、VCO105は、D/A変換器104が出力する電圧に応じた周波数の同期クロックを出力する。位相比較器102が出力する位相誤差は、デジタルループフィルタ103の出力に所定の係数Aを乗じたものでゲイン補正され、デジタルループフィルタ103に入力される。デジタルループフィルタ103に入力する位相誤差を、出力クロック周波数に比例して変化させることで、PLLループ全体として、出力クロック周波数に依存して線形にループ特性が制御できる。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、遅延時間及びデューティ比を選択可能にしたクロックを、ジッタ劣化させずに生成することができる技術を提供する。

【解決手段】DLL回路201から生成された2つのクロックを、生成クロックのライズエッジ及びフォールエッジを定めるために用いる。DLL回路201からの2つのクロックは遅延時間を選択可能とする。選択された2つのクロックを、クロック合成回路203の2入力に与える。このクロック合成回路203は位相周波数比較器と同様の回路であり、排他的論理和を用いない。この位相周波数比較器の機能により、出力クロックのライズエッジ及びフォールエッジのタイミングは、入力2クロックのライズエッジにより定まる。そのため、入力2クロックの位相(遅延時間)を任意に選択することにより、所望のデューティ比及び遅延時間を持った出力クロックが得られる。

(もっと読む)

タイムトゥデジタルコンバータ

【課題】タイムトゥデジタルコンバータを提供する。

【解決手段】タイムトゥデジタルコンバータは、高い解像度と広い測定範囲のために低解像度タイムトゥデジタルコンバータと高解像度タイムトゥデジタルコンバータとを含む。低解像度タイムトゥデジタルコンバータは、第1信号と第2信号との時間差を第1量子化間隔で測定する。高解像度タイムトゥデジタルコンバータは、第1信号と第2信号との時間差を第1量子化間隔よい更に小さい第2量子化間隔で測定する。低解像度タイムトゥデジタルコンバータは、高解像度タイムトゥデジタルコンバータより広い測定範囲を有する。

(もっと読む)

ルビジウム原子発振器

【課題】スイープ電圧発生のための回路規模を小型化し、且つ非ロック時における周波数引き込み動作を自動的に行なうことが可能なルビジウム原子発振器を提供する。

【解決手段】このルビジウム原子発振器100は、OMU1と、増幅器2と、出力信号をデジタル信号に変換するA/D変換器3と、ロック状態又は非ロック状態を判定する状態判定部11と、位相変調信号fmの周波数成分を選択的に出力するBPF13と、スイープ電圧データを生成するスイープ電圧データ生成手段12と、タイマ15と、第1のBPF13の出力信号又はスイープ電圧データ生成手段12の出力信号を選択するSW−A14と、アナログ信号に変換するD/A変換器5と、位相検波して周波数制御信号を生成する位相検波器6と、周波数制御信号を積分処理する積分回路7と、周波数制御信号に従い出力周波数が制御されるVCXO8と、を備えて構成されている。

(もっと読む)

PLLロック検出回路および半導体装置

【課題】高精度のPLLロック検出信号を得るとともに、平滑回路を削除することができるPLLロック検出回路を提供する。

【解決手段】本発明に係るPLLロック検出回路は、PLL回路において、誤ってロック判定することなく、安定したロック状態においてロック判定とアンロック判定の両方を同時に行うことにより、確実なロック判定を行う。PLLロック状態が数H連続して継続しているかどうかの検出を行う連続性検出部と、PLLアンロック状態が数H連続して継続しているかどうかの判定行う連続性検出部を備え、これら連続性検出部によってPLLのロック状態が同時に検出され、その検出結果を保持するR−Sラッチ部を備えている。

(もっと読む)

PLL回路

【課題】電圧制御発振回路が分周回路の設計値を越えた周波数で発振した場合にも、暴走状態を防止して動作安定を実現するPLL回路を提供する。

【解決手段】第1の複数電源電圧発生回路8は、2つの異なる電圧レベルB,Cを電圧選択回路9に出力し、電圧選択回路9は分周回路5の電源線へいずれかの電圧を出力する。電圧レベルBは、電圧制御発振回路4が暴走を始め、分周回路5が動作不可能となった場合に、分周回路5を動作可能状態にするレベルに設定してある。ループフィルタ3の出力が電圧制御発振回路4を暴走状態にして、分周回路5の動作可能範囲を越える場合、電圧比較回路6はHIGH信号を出力し、電圧選択回路9が分周回路の電源電圧を電圧レベルCから電圧レベルBへ切り替え、分周回路5の出力クロックが生成されるようになる。

(もっと読む)

DLL回路

【課題】 クロックの立ち上がり及び立ち下がりに同期した内部クロックを生成するDLL回路においては、高精度が要求されることから回路規模が大きくなるという問題がある。

【解決手段】 Rise用の遅延調整回路とFall用の遅延調整回路を備え、Fall用の遅延調整回路にはRise用の遅延調整回路でRise側を調整したクロックを入力する。入力されるクロックのRise側が調整されていることから、Fall側の遅延差は非常に小さくなる。そのため、Fall用の遅延調整回路、カウンタの回路規模が大幅に削減できる。その結果少ない回路規模で、高精度のDLL回路が得られる。

(もっと読む)

位相比較信号処理回路

【課題】位相比較回路の出力矩形波信号の処理する際に、簡単な回路構成を有し、PLLで引込み可能な周波数幅を拡げ、同期時間を短縮できる位相比較信号処理回路を提供する。

【解決手段】入力矩形波信号を双極性信号に変換する電圧シフタ2、入力矩形波信号のレベル変化時に制御パルス信号を発生する制御パルス信号発生器7、制御パルス信号の到来時に積分値をリセットし、その後双極性信号を積分して積分値を出力する積分回路3、積分値のリセット時のレベル変化分を微分パルスとして出力する微分回路4、制御パルス信号の到来時に微分パルスを出力するゲート回路6、前記保持回路は最新の入力微分パルスレベルを保持し、微分パルスレベルの更新時にその微分パルスレベルが保持されるように保持電圧値が順次変化する保持信号を形成するホールド回路8を備え、この保持信号を次段のループフィルタに供給する。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】DLL回路を備えた半導体記憶装置のチップを複数備えた半導体装置の消費電力の低減。

【解決手段】DLL(Delay Lock Loop)を備えた半導体記憶装置の積層モジュールまたは半導体記憶装置を複数有するマルチチップモジュール(MCM)において、DLLで遅延調整されたクロック信号(CLK)を、一の半導体記憶装置と他の半導体記憶装置間で共用するための専用パッド(PAD)を有し、一の半導体記憶装置のDLLを動作させ、他の半導体記憶装置ではDLLを動作させず、一の半導体記憶装置の前記専用パッドから、DLLで遅延調整されたクロック信号(CLK)から作られる、差動の外部クロック信号(CLK、CLKB)に同期した、フライングロッククロック信号を出力し、他の半導体記憶装置は、フライングロッククロック信号を、専用パッドから入力する。

(もっと読む)

半導体集積回路

【課題】PLL(Phase Locked Loop)回路を搭載した半導体集積回路において、当該PLL回路の発振安定待ちの時間を有効利用する。

【解決手段】実動作準備期間中に、PLL回路50の帰還ループを遮断した状態で位相比較器51の参照クロック入力部Fpと帰還クロック入力部Frとの双方に基準クロック100を供給して、位相比較器51における位相差の検出不感帯が小さくなるように当該位相比較器51内のリセット信号の遅延を調整する。

(もっと読む)

半導体装置

【課題】微細プロセスに好適で高性能化したPLL回路を備えた半導体装置を提供する。

【解決手段】基準信号と帰還信号と位相比較器で比較する。この位相比較器の位相比較出力でチャージポンプ回路を制御し、その出力電流をフィルタ&電圧−電流変換回路に供給して発振回路を制御する。上記発振回路の出力信号を分周回路で分周して上記帰還信号を形成してPLL回路を構成する。上記フィルタ&電圧−電流変換回路は、一方の入力にバイアス電圧が供給された差動増幅回路の出力信号がゲートに供給された出力MOSFETと、上記出力MOSFETのドレインに設けられた抵抗素子と、上記出力MOSFETのドレインと上記差動増幅回路の他方の入力との間に設けられたキャパシタとで構成される。上記チャージポンプ回路の出力電流を、上記差動増幅回路の他方の入力に供給する。

(もっと読む)

クロック同期回路及びそれを備えた半導体装置

【課題】複数の回路間で異なるクロックを使用した場合であっても、安定した通信が可能であるクロック同期回路及びそれを備えた半導体装置の提供を課題とする。

【解決手段】受信したデータの変化点を検出し、リセット信号を出力する手段と、クロック信号を出力する基準クロック発生回路と、クロック信号をカウントする基準クロックカウンター回路と、基準クロックカウンター回路から出力された信号を分周する分周回路と、分周回路から出力された信号により回路動作用基準クロック信号を出力する手段とを設ける。

(もっと読む)

周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法

【課題】周波数比較回路を少ない素子数で構成できるようにすると共に、第1、第2の信号(例えば、NCLK信号およびMCLK信号)の周波数が一致しているか否かを正しく判定できるようにした周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法を提供する。

【解決手段】NCLK信号の立ち上がりもしくは立ち下がりのエッジを検出し、基準クロックで同期化されたUP信号を生成するエッジ検出回路111aと、MCLK信号の立ち上がりもしくは立ち下がりのエッジを検出し、基準クロックで同期化されたDown信号を生成するエッジ検出回路111bと、UP信号及びDown信号をカウントし、そのカウント値をQ1、Q0信号で出力する2ビットアップダウンカウンタ112と、Q1、Q0信号に基づいて、NCLK信号の周波数とMCLK信号の周波数とが一致しているか否かを判定する判定回路113と、を有する。

(もっと読む)

周波数シンセサイザおよびこれに用いるループフィルタ

【課題】コンデンサの容量値を小さくしてループフィルタのIC化を容易にし、かつ、周波数シンセサイザの同期状態に関係なくC/N特性やスプリアス特性を改善できるようにする。

【解決手段】並列接続された複数のコンデンサC1〜Cnと、これらのチャージ/ディスチャージ動作をパイプライン処理として行うように切り替えを行うスイッチSW11〜SW1n,SW21〜SW2nと、複数のコンデンサC1〜Cnを備えた並列回路の出力側に接続されたコンデンサCHとを備えてLPF15を構成し、各コンデンサC1〜Cnに順次チャージされた電荷が並列回路の出力として得られ、それがコンデンサCHに順次に蓄積されるようにすることにより、各コンデンサC1〜Cn,CHの容量値を小さくすることにより時定数が小さくなっても、回路全体として大きな時定数を実現できるようにする。

(もっと読む)

周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法

【課題】周波数比較回路を少ない素子数で構成できるようにすると共に、NCLK信号およびMCLK信号等の周波数が一致しているか否かを正しく判定できるようにする。

【解決手段】NCLP信号の分周信号であるNCLP2信号と、MCLP信号の分周信号であるMCLP2信号とを生成する。次に、MCLP2信号がHレベルのときはNCLP信号をアップ信号としてカウントし、MCLP2信号がLレベルのときはNCLP信号をダウン信号としてカウントし、そのカウント値をQN1、QN0信号で出力する。また、NCLP2信号がHレベルのときはMCLP信号をアップ信号としてカウントし、NCLP2信号がLレベルのときはMCLP信号をダウン信号としてカウントし、そのカウント値をQM1、QM0信号で出力する。そして、QN1、QN0、QM1、QM0の各信号に基づいて、NCLP信号とMCLP信号の各周波数が一致しているか否かを判定する。

(もっと読む)

集積回路、表示装置及びそれを用いた電子機器

【課題】DLLに求められる保証動作周波数帯域を低め、基準クロック信号が二逓倍された周波数をそれぞれ有し、位相差のある2つのクロック信号を生成することができる集積回路、表示装置及び電子機器を提供する。

【解決手段】タイミングコントロールICは、一周期Tの基準クロック信号ICLKと同一周波数の第1〜第4のクロック信号CLK1〜CLK4であって、第N(N=1,3のいずれか)のクロック信号に対する第(N+1)のクロック信号の位相遅れが位相差T/4で、かつCLK1に対するCLK3の位相遅れが位相差α(0<α<T/4)であるCLK1〜CLK4のクロック信号を発生させるDLL40と、CLK1が二逓倍されたデータ生成用のCLK5を生成し、かつ、CLK3が二逓倍されて、CLK5に基づき生成されデータ信号に対して位相差αの遅れで同期したCLK6を生成する二逓倍回路50とを有する。

(もっと読む)

インピーダンス回路およびこれを用いた信号生成回路

【課題】基準周波数を得る場合、安定した周波数、もしくは遅延要素を得る回路を提供する。

【解決手段】第1の温度変動率を持つ第1のインピーダンス回路1と第1の能動回路3で構成した第1の発振回路6と、第1の温度変動率とは逆の変動方向となる第2の温度変動率を持つ第2のインピーダンス回路2と第2の能動回路4で構成した第2の発振回路7との出力を時系列的に交互に切替器5で選択する。第1のインピーダンス回路1の温度係数の絶対値が第2のインピーダンス回路2の温度係数より大きいとき、第1の発振回路6の使用時間を短くし、温度係数の小さい第2の発振回路7の使用時間を長く動作させるように、温度係数の比と逆の比率で発振回路の使用時間の比率を設定する。温度変動方向が逆の2つの温度係数を有することから、平均値として温度変動がほぼなく軽減される。時間平均値として温度変動が極めて小さく温度変動率の改善された発振周波数を得る。

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】入力される基準クロック信号に基づく変調波を生成するスペクトラム拡散クロック発生回路であって、回路の製造プロセス、電源、又は、温度等に起因する変調波の変動を低減するスペクトラム拡散クロック発生回路を提供すること。

【解決手段】出力信号を分周した分周出力信号を出力する分周器と、前記分周出力信号と受信した基準クロック信号との位相差を検出する位相比較器と、前記位相差に応じて充放電信号を発生するチャージポンプと、前記充放電信号に応じた差信号を発生するループフィルタと、前記差信号と変調波とが入力されて被変調波を生成する変調回路と、前記被変調波に応じた周波数のクロックを発生するクロック発生器とを有するスペクトラム拡散クロック発生回路であって、前記基準クロック信号に基づき前記変調波を生成する変調波生成回路を有するスペクトラム拡散クロック発生回路。

(もっと読む)

クロック生成回路

【課題】

要求されるデューティ比の同期クロック信号を生成できるか否かの判別が正確に行われるクロック生成回路を提供する。

【解決手段】

クロック生成回路100において、外部から入力されてきた外部クロック信号Sextclkを遅延することにより外部クロック信号Sextclkに同期した同期クロック信号Sclkを生成するDLL回路110と、DLL回路110のデューティ比劣化テスト用にパルス幅を変化させたテスト信号Stestを生成するテスト信号生成回路120と、外部クロック信号Sextclkおよびテスト信号Stestのうちの一方の信号を選択してDLL回路110に入力する選択回路130とを備えたことを特徴とする。

(もっと読む)

101 - 120 / 197

[ Back to top ]