Fターム[5J106KK37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | IC化,LSI化 (197)

Fターム[5J106KK37]に分類される特許

141 - 160 / 197

クロックアンドデータリカバリ回路及びSERDES回路

【課題】クロックアンドデータリカバリ回路の動作余裕度の大きさを測定可能とするSERDES回路の提供。

【解決手段】シリアルデータサンプリング回路(101)と、クロックとデータの位相関係を検出する位相比較器(102)と、位相比較結果(UP/DOWN)に基づき位相制御信号を出力する位相制御器(103)と、互いに異なる位相の複数のクロック信号よりなる多相クロックを受け、位相制御信号に基づき位相を補間したクロック信号をデータサンプリング回路(101)に供給する位相補間器(104)とがループを構成する。この位相制御器(103)は、位相制御信号とは別の位相制御信号Aを生成して別の位相補間器(105)に供給し、多相クロックを受け位相制御信号Aに対応して補間したクロック信号に基づき入力データをサンプルする別のデータサンプリング回路(106)を備え、好ましくは、データをサンプルするための閾値レベルが可変に設定される。

(もっと読む)

半導体装置

【課題】PLL回路のロックタイムを短縮しつつ、ロック時のチャージポンプのリーク電流を削減して安定した出力信号を供給する半導体装置を提供する。

【解決手段】一の電源電圧と接続され、半導体基板上に位相同期ループ回路1を配設する半導体装置において、位相同期ループ回路には、複数の回路ブロック2、3、5、6が備わり、半導体基板上には、一の電源電圧から電圧値の異なる電圧を生成して、回路ブロックごとにそれぞれ電圧値の異なる電圧を供給する複数の電源電圧供給手段7、8、9と、かかる電源電圧供給手段から生成された電圧の何れか一つを回路ブロックのうちの少なくとも一つの回路ブロックに含まれるPMOSトランジスタ基板に選択的に供給することにより電圧の供給先となる回路ブロックの出力を制御する供給電圧制御手段10と、を備えることを特徴とする。

(もっと読む)

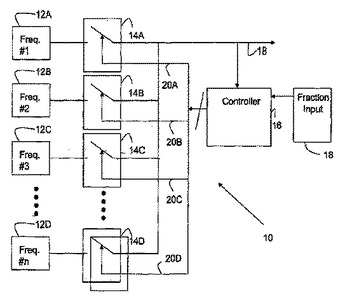

高速スイッチングのための周波数合成の新規方法

単一のソースの設計、マルチプレクサの設計、分数分周器の設計、または周波数逓倍器と周波数分周器の設計で実装可能なデジタル周波数シンセサイザである。実装は、制御器のディザリング回路またはデルタシグマ変調器を利用可能である。この周波数シンセサイザは、CMOS構成において実装可能であり、クリーンアップ位相ロックループ(PLL)を利用可能である。  (もっと読む)

(もっと読む)

DLL回路及びこのDLL回路を備えた半導体装置並びにこの半導体装置を備えた電子機器

【課題】待機状態としたDLL回路を速やかに通常の動作状態に復帰可能としたDLL回路、及びこのDLL回路を備えた半導体装置、並びにこの半導体装置を備えた電子機器を提供する。

【解決手段】DLL回路は、入力されたクロック信号から遅延信号を生成する遅延信号生成回路と、遅延信号とクロック信号との位相差に基づいて制御信号を生成する位相比較回路と、制御信号の電圧レベルを昇圧するチャージポンプ回路とを有し、遅延信号生成回路へのクロック信号の入力をスイッチ回路により遮断されて待機状態となるDLL回路であって、待機状態時に、チャージポンプ回路に設けた昇圧用のキャパシタに所定量のリークが生じたことを検出するリーク検出回路と、このリーク検出回路でのリークの検出に基づいてキャパシタへの充電を開始させる充電制御回路とを有することとした。

(もっと読む)

電圧制御発振器、PLL回路、信号処理回路およびチューナパック

【課題】発振振幅を小さく設定でき、特性の合し込みを容易にできる電圧制御発振器を提供する。

【解決手段】本発明における電圧制御発振器は、発振周波数制御電圧S35に応じ、発振信号S103の周波数を変更する電圧制御発振器103であって、差動増幅型のトランジスタ対を有し、前記トランジスタ対から発振信号S103を出力する差動増幅型発振器50と、前記トランジスタ対に接続され、発振周波数制御電圧S35に応じ、等価容量を変更する発振周波数制御回路51とを備え、前記トランジスタ対を構成するトランジスタQ1およびQ2は、出力電流が実質的に変化しない領域で動作するように構成される。

(もっと読む)

位相ロックループ内でのキャパシタンス乗算のための方法および装置

2つのチャージポンプを用いるキャパシタンス乗算のための方法および装置である。第1のチャージポンプ(206)は、RCネットワークの抵抗器(310)によってまず伝えられ、次いで、RCネットワークのキャパシタによって伝えられる前に3つの電流路に分離される電流信号(I216)を供給する。第1の電流路は、ノード(320)からRCネットワークのキャパシタ(306)に電流を供給する。第2の電流路は、キャパシタ(306)が伝える電流を、第1の電流乗算係数で乗算する。第3の電流路は、第1の電流乗算係数に対して逆の大きさの符号を有する小数値を有する第2の電流乗算係数で第1のチャージポンプ(206)からの電流を乗算する第2のチャージポンプ(208)に電流を供給する。第2および第3の電流路の組合せにより、キャパシタ(306)のキャパシタンスの大きさは効果的に乗算される。  (もっと読む)

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】従来のスペクトラム拡散クロック発生回路では、回路内で前もって設定された複数値の拡散率の中に、他に及ぼす電磁ノイズ(EMI)の影響を最も良好に遮断できる拡散率が無い可能性が生じ、スペクトラム拡散クロック発生回路のEMI対策効果が不十分となる虞がある。

【解決手段】基準クロック信号と帰還クロック信号の位相差を検出する周波数位相比較器と、この位相差に応じて充電又は放電信号を発生するCPと、この充電信号に応じた差信号を発生する充放電回路と、電圧制御発振器を具備するスペクトラム拡散クロック発生回路において、上記スペクトラム拡散変調回路は、制御電圧VC値を可変させることで複数の異なる振幅で変化するスペクトラム拡散アナログ電圧信号を発生する変調器と、差信号にスペクトラム拡散アナログ電圧信号を加算する電圧加算器とを具備するスペクトラム拡散クロック回路。

(もっと読む)

周波数シンセサイザ

【課題】ロックさせる周波数の制御精度と処理速度とを共に擬制にすることなく、PLL回路の構成を1つの半導体チップに集積できるようにする。

【解決手段】アップ/ダウンカウンタ5を用いた第1のロックループによって局部発振周波数の粗調整を行うとともに、S/H回路11を用いた第2のロックループによって局部発振周波数の微調整を行うことにより、位相差に応じてコンデンサに電荷をチャージしたりポンプしたりする動作を不要とし、大容量のコンデンサを用いるLPFを周波数シンセサイザから省略できるようにする。また、S/H回路11を用いた微調整によって局部発振周波数を精度良くロックさせることができるようにするとともに、ロックさせる周波数の制御精度を上げるためにアップ/ダウンカウンタ5のビット数を大きくする必要をなくし、局部発振周波数を所望の周波数に高速にロックさせることができるようにする。

(もっと読む)

半導体装置

【課題】微細プロセスに好適で高性能化したV−I変換回路とPLL回路を備えた半導体装置を提供する。

【解決手段】入力電圧がゲートに供給された第1導電型のソースと第1電圧との間第1抵抗を設ける。第2電圧側に設けられた第2導電型の第2MOSFETと第3MOSFETで電流ミラー回路を構成し、上記第1MOSFETのドレイン電流に対応した出力電流を形成する。第1定電流源の定電流を上記第1電圧側に設けられた第1導電型の第4MOSFETと第5MOSFETで電流ミラー回路を介して上記第2、第3MOSFETの電流ミラー回路に流すようにする。上記中心電圧に対応した入力電圧の変化範囲と、中心電流に対応した出力電流の変化範囲とがほぼ対応するよう上記第5MOSFETに流れる定電流値及び上記第1MOSFETのコンダクタンスを設定する。

(もっと読む)

DLL回路及びその試験方法

【課題】通常時の基準クロックより周波数の低い1本の試験用クロックによるディレイ・ライン回路の動作試験を可能とする。

【解決手段】ディレイ・ライン回路101は、遅延量を変更可能であり、基準クロック信号RCLKに遅延を与えることができる。位相比較回路102は、基準クロック信号RCLKとディレイ・ライン回路101の出力信号との間又は基準クロック信号RCLKより周波数の低い試験クロック信号TCLKとディレイ・ライン回路101の出力信号との間の位相差を検出可能である。また、制御回路103は、位相比較回路102の検出結果に応じて制御信号を出力し、ディレイ・ライン回路101の遅延量を制御する。さらに、ディレイ・ライン回路101に対して、ディレイ・ライン回路101の出力信号と基準クロック信号RCLKとのいずれかを選択して入力できるよう構成されている。

(もっと読む)

DLL回路及びこれらを備えた半導体装置

【課題】 従来のDLL回路では、DQバッファ系の経路とDQレプリカ系の経路とを備え、DQレプリカ系の遅延時間をモニタすることでDQレプリカ系の遅延時間としている。しかし、温度、電圧、製造ばらつき等により、DQバッファ系の遅延時間とDQレプリカ系の遅延時間との誤差が発生するという問題がある。

【解決手段】 ZQキャリブレーション結果により遅延量を可変させる遅延量可変回路を、DQレプリカ系の経路に挿入する回路構成とする。DQレプリカ系の経路の遅延量を可変とし、DQバッファ系とDQレプリカ系とのタイミングスキュー差を一定になるように調整する。ZQキャリブレーション結果は温度、電圧、製造ばらつきに対応して変動することから、これらの変動に対応した遅延量を得ることでスキュー差を一定にできる高精度のDLL回路及びこのDLL回路を備えた半導体装置が得られる。

(もっと読む)

半導体装置

【課題】プロセスの振れ,温度や電圧等の変動による出力データのホールド時間の振れに対して、そのタイミング調整を容易に行い、安定した動作を確保し得る信号位相調整機能を備えた半導体装置を提供する。

【解決手段】外部入力信号の入力に対して入力信号と位相同期した出力信号を出力する入力−出力間での信号位相調整機能を備えた半導体装置において、外部からの入力信号である第1信号と入力信号を所定の遅延量で遅延させてなる第2信号との間で位相の同期をとる位相調整手段と、装置内部から外部への出力信号を遅延させる出力信号遅延手段であって、位相調整手段において両信号間で位相の同期がとられた時点で用いられる制御信号に基づき、出力信号に対して付与される遅延量を調整する出力信号遅延手段と、を設ける。

(もっと読む)

PLL周波数シンセサイザ

【課題】ロックアップタイムが短縮でき、かつ回路規模も小さくて済むPLL周波数シンセサイザを提供する。

【解決手段】PLL周波数シンセサイザにおいて、ループフィルタ7をノッチ周波数がリファレンス周波数に設定されたツインT型ノッチフィルタ71とツインT型ノッチフィルタ71の後ろに直列接続されたローパスフィルタ72とで構成すると共に、ツインT型ノッチフィルタ71の一部を構成する抵抗R2とローパスフィルタ72の一部を構成する抵抗R2とを共用にした。

(もっと読む)

PLL回路におけるアクティブフィルタ。

【課題】 PLL回路の内部のローパスフィルタを構成する回路素子、特に静電容量の値を小さくすることによって、ローパスフィルタをチップに内蔵化可能とする。

【解決手段】 位相比較器の後段に2つのチャージポンプ回路を備えるPLL回路内で用いられるアクティブフィルタが、一方のチャージポンプ回路の出力とアースとの間に接続される第1の回路要素と、他方のチャージポンプ回路の出力とアースとの間に接続される第2の回路要素と、第1、第2の回路要素のそれぞれの両端の電圧を加算する電圧加算器とを備える。

(もっと読む)

DLL装置及びDLLクロック生成方法

【課題】長時間パワーダウンモード状態にとどまる場合にロックフェイル(fail)が発生するのを防止すること。

【解決手段】外部クロックを受信して、バッファリングして、内部クロックを生成するクロックバッファと、クロックイネーブル信号CKEに応答して、ノーマルモードなのか、パワーダウンモードなのか、に対する情報を有する制御信号を生成するパワーダウンモード制御部と、前記の制御信号に応答して、内部クロックに基づいた、ソースクロックを提供するソースクロック生成部と前記のソースクロックに基づいてDLLの位相更新を行い、DLLクロックを提供する位相更新部を備える遅延固定ループを提供する。長時間にパワーダウンモードにとどまる場合にも、パワーダウンモード区間の一部の区間で、DLL位相更新を行なうことによって、ロックフェイル(fail)が発生することを防止できる。

(もっと読む)

半導体集積回路

【課題】 トリミングを行わずに電圧制御発振回路の発振周波数を調整すること。制御回路の面積を抑え、調整誤差の少ない発振回路を内蔵した半導体集積回路を提供すること。

【解決手段】 電圧制御発振回路(VCO)の周波数を調整する可変容量素子を、プロセスや素子のばらつき調整用可変容量素子群と、周波数選択用可変容量素子群との2系統に分離して調整を行い、可変容量素子の切り替えスイッチの数と回路面積の増大を小さくする。調整誤差については、調整期待値との差分を記憶素子で記憶し、その差分値が最小となる容量素子値を求めることにより影響を最小限に押さえることが可能となる。

(もっと読む)

スケーリングされた制動コンデンサを有する位相ロック・ループ

【課題】フィードバック・ループのループ・ダイナミクスおよび安定性に普通なら及ぼすような影響を及ぼすことなく、ループ・フィルタを実施するために使用されるコンデンサの面積を縮小すること。

【解決手段】チャージ・ポンプPLLの面積を縮小するために、ループ・フィルタ電圧の比例成分と積分成分を分離し、別の回路を追加して、積分成分が、実際に使用されたよりもはるかに大きな容量値によって影響を受けたかのように見えるようにすることができる。一態様では、電流ミラーを使用して、総ループ・フィルタ電圧からループ・フィルタ電圧の積分成分の一部分を減じることができる。次いで、差動信号を使用して、チャージ・ポンプPLLで発振器を駆動する。他の態様では、第3の積分器または自動較正ループを使用して、発振器の中央周波数を設定する。

(もっと読む)

位相同期ループ回路及びそのセルフバイアス方法

【課題】工程変化に鈍感なセルフバイアス位相同期ループ回路及びそのセルフバイアス方法を提供する。

【解決手段】第1演算増幅器は、ループフィルタキャパシタの電圧を増幅して出力し、レギュレータとして機能する第2演算増幅器は、第1演算増幅器の出力電圧をさらに増幅して出力する。第2演算増幅器の出力電圧は、電圧制御発振器の制御電圧として使われる。バイアス回路は、第2演算増幅器の出力電圧に応答して、NMOSトランジスタによって第1バイアス電流を発生し、PMOSトランジスタによって第2バイアス電流を発生し、第1バイアス電流と第2バイアス電流とを加算して第3バイアス電流を発生する。そして、第1バイアス電流は、主電荷ポンプ回路及び補助電荷ポンプ回路のバイアス電流として提供され、第3バイアス電流は、第1演算増幅器のバイアス電流として提供される。

(もっと読む)

PLL制御のためのシステム及び方法

【課題】フェーズロックループ(PLL)回路に対するロジックの動作の影響を弱めるためのシステム及び方法を提供する。

【解決手段】システムと方法は、PLL回路が命令の予期される影響を命令の実行前、同時、あるいは後で補償することを実質的に許してもよい。より特に、システムの命令の発行に関連したロジックは、命令に基づいたシステムでのPLLに信号を供給してもよい。その後、PLLはこの制御信号に基づいた命令の予期される影響を補償するために調節されてもよい。

(もっと読む)

フェーズ・ロックト・ループ・フィルタ

第1のチャージ・ポンプ経路に接続する第1のキャパシタと、第2のチャージ・ポンプ経路に接続する並列抵抗/キャパシタ回路とを備えるフェーズ・ロックト・ループ・フィルタである。抵抗/キャパシタ回路は、第2のキャパシタを備える。第1のキャパシタ及び第2のキャパシタは、第1のキャパシタと関連した電圧及び並列抵抗/キャパシタ回路と関連した電圧とを加えあわせるのを可能にするよう直列に接続されている。  (もっと読む)

(もっと読む)

141 - 160 / 197

[ Back to top ]